| ±ύΦ≠ΆΤΦω: |

±ΨΈΡΦρΒΞΒΊΫ≤ΫβΝΥ«ΐΕ·»μΦΰΙΛ≥Χ Π±Ί±ΗΒΡ”≤ΦΰΜυ¥Γ÷Σ ΕΘ§Οη ωΝΥ¥ΠάμΤςΓΔ¥φ¥ΔΤςΒΡΖ÷άύ“‘ΦΑΗς÷÷¥ΠάμΤςΓΔ¥φ¥ΔΤςΒΡ‘≠άμ”κ”ΟΆΨΘ§≤ΔΖ÷ΈωΝΥ≥ΘΦϊΒΡΆβΈß…η±ΗΫ”ΩΎ”κΉήœΏΒΡΙΛΉςΖΫ ΫΓΘ

¥ΥΆβΘ§±Ψ’¬ΜΙΫ≤ ωΝΥΕ‘«ΐΕ·ΙΛ≥Χ ΠΫχ–– ΒΦ œνΡΩΩΣΖΔ”–Αο÷ζΒΡ‘≠άμΆΦΓΔ”≤Φΰ ±–ρΖ÷ΈωΖΫΖ®Θ§–ΨΤ§ ΐΨί ÷≤α‘ΡΕΝΖΫΖ®“‘ΦΑΆρ”Ο±μΓΔ Ψ≤®ΤςΚΆ¬ΏΦ≠Ζ÷Έω“«ΒΡ Ι”ΟΖΫΖ®ΓΘ

±ΨΈΡά¥Ή‘”Ύ ÷ΣΚθ Θ§”…ΜπΝζΙϊ»μΦΰLinda±ύΦ≠ΓΔΆΤΦωΓΘ |

|

…η±Η«ΐΕ·Ής”Ο

ΟΜ”–≤ΌΉςœΒΆ≥…η±Η«ΐΕ·

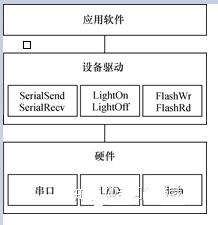

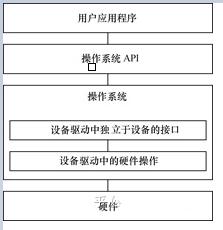

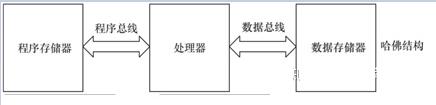

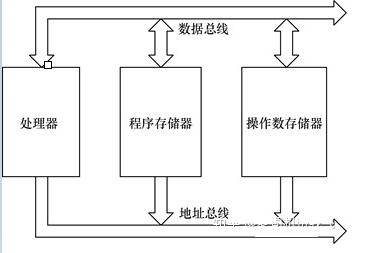

…η±Η«ΐΕ·Ϋ”ΩΎ÷±Ϋ”ΧαΙ©Ηχ”Π”Ο»μΦΰΙΛ≥Χ ΠΘ§”Π”Ο»μΦΰΟΜ”–Ωγ‘Ϋ»ΈΚΈ≤ψ¥ΈΨΆ÷±Ϋ”ΖΟΈ ΝΥ…η±Η«ΐΕ·ΒΡΫ”ΩΎΘ§»γœ¬ΆΦΥυ ΨΘΚ

”–≤ΌΉςœΒΆ≥ΒΡ…η±Η«ΐΕ·

Υυ”–…η±Η«ΐΕ·…ηΦΤ±Ί–κΖϊΚœ≤ΌΉςœΒΆ≥ΡΎΚΥΒΡΫ”ΩΎΙφΕ®Θ§«ΐΕ·±δ≥…Ν§Ϋ””≤ΦΰΚΆΡΎΚΥΒΡ«≈ΝΚΘ§Ε‘Άβ≥ œ÷ΈΣ≤ΌΉςœΒΆ≥ΒΡAPIΘ§≤Μ‘ΌΗχ”Π”Ο»μΦΰΙΛ≥Χ Π÷±Ϋ”ΧαΙ©Ϋ”ΩΎΓΘ”Π”Ο»μΦΰΙΛ≥Χ Π–η“ΣΆ®ΙΐœΒΆ≥Βς”ΟΜρΤδΥϋΖΫ ΫΦδΫ”≤ΌΉς«ΐΕ·…η±ΗΫ”ΩΎΓΘ

…η±Η«ΐΕ·Ϋι…ή

…η±ΗΖ÷άύΦΑΧΊΒψ

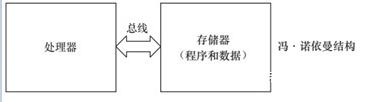

ΦΤΥψΜζœΒΆ≥ΒΡ”≤Φΰ÷ς“Σ”…CPUΓΔ¥φ¥ΔΤςΚΆΆβ…ηΉι≥…ΓΘΥφΉ≈IC ÷ΤΉςΙΛ“’ΒΡΖΔ’ΙΘ§ΡΩ«ΑΘ§–ΨΤ§ΒΡΦ·≥…Ε»‘Ϋά¥‘ΫΗΏΘ§ΆυΆυ‘ΎCPUΡΎ≤ΩΨΆΦ·≥…ΝΥ¥φ¥ΔΤςΚΆΆβ…η ≈δΤςΓΘΤ©»γΘ§œύΒ±ΕύΒΡARMΓΔPowerPCΓΔMIPSΒ»¥ΠάμΤςΕΦΦ·≥…ΝΥ

UARTΓΔ I2C ΩΊ÷ΤΤςΓΔ SPI ΩΊ÷ΤΤςΓΔ USB ΩΊ÷ΤΤςΓΔSDRAMΩΊ÷ΤΤςΒ»Θ§”–ΒΡ¥ΠάμΤςΜΙΦ·≥…ΝΥ

GPUΘ®ΆΦ–Έ¥ΠάμΤςΘ©ΓΔ ”ΤΒ±ύΫβ¬κΤςΒ»ΓΘ«ΐΕ·’κΕ‘ΒΡΕ‘œσ «¥φ¥ΔΤςΚΆΆβ…ηΘ®Αϋά® CPU ΡΎ≤ΩΦ·≥…ΒΡ¥φ¥ΔΤςΚΆΆβ…ηΘ©Θ§Εχ≤Μ «’κΕ‘CPU

ΡΎΚΥΓΘ Linux ΫΪ¥φ¥ΔΤςΚΆΆβ…ηΖ÷ΈΣ 3 ΗωΜυ¥Γ¥σάύΓΘ

Γώ Ή÷Ζϊ…η±ΗΓΘ

Γώ Ωι…η±ΗΓΘ

Γώ Άχ¬γ…η±Η

Linux …η±Η«ΐΕ·”κ’ϊΗω»μ”≤ΦΰœΒΆ≥ΒΡΙΊœΒ

»γœ¬ΆΦΥυ ΨΘ§≥ΐΆχ¬γ…η±ΗΆβΘ§Ή÷Ζϊ…η±Η”κΩι…η±ΗΕΦ±Μ”≥…δΒΫ Linux ΈΡΦΰœΒΆ≥ΒΡΈΡΦΰΚΆ

ΡΩ¬ΦΘ§Ά®ΙΐΈΡΦΰœΒΆ≥ΒΡœΒΆ≥Βς”ΟΫ”ΩΎ open()ΓΔ write()ΓΔ read()ΓΔ close()

Β»Φ¥Ω…ΖΟΈ Ή÷Ζϊ…η±ΗΚΆΩι…η±ΗΓΘΥυ”–Ή÷Ζϊ…η±ΗΚΆΩι…η±ΗΕΦΆ≥“Μ≥ œ÷Ηχ”ΟΜßΓΘ Linux ΒΡΩι…η±Η”–ΝΫ÷÷ΖΟΈ ΖΫΖ®ΘΚ“Μ÷÷ «άύΥΤ

dd ΟϋΝνΕ‘”ΠΒΡ‘≠ ΦΩι…η±ΗΘ§»γΓΑ /dev/sdb1Γ±Β»ΘΜΝμΆβ“Μ÷÷ΖΫΖ® «‘ΎΩι…η±Η…œΫ®ΝΔFATΓΔ EXT4ΓΔ

BTRFS Β»ΈΡΦΰœΒΆ≥Θ§»ΜΚσ“‘ΈΡΦΰ¬ΖΨΕ»γΓΑ /home/barry/hello.txtΓ±ΒΡ–Έ ΫΫχ––ΖΟΈ ΓΘ‘Ύ

Linux ÷–Θ§’κΕ‘ NORΓΔ NAND Β»ΧαΙ©ΝΥΕάΝΔΒΡΡΎ¥φΦΦ θ…η±ΗΘ® Memory TechnologyDeviceΘ§

MTDΘ©Ή”œΒΆ≥Θ§Τδ…œ‘Υ–– YAFFS2ΓΔ JFFS2ΓΔ UBIFS Β»ΨΏ±Η≤Ν≥ΐΚΆΗΚ‘ΊΨυΚβΡήΝΠΒΡΈΡΦΰœΒΆ≥ΓΘ’κΕ‘¥≈≈ΧΜρ’Ώ

Flash …η±ΗΒΡ FATΓΔ EXT4ΓΔ YAFFS2ΓΔ JFFS2ΓΔ UBIFS Β»ΈΡΦΰœΒΆ≥Ε®“εΝΥΈΡΦΰΚΆΡΩ¬Φ‘Ύ¥φ¥ΔΫι÷ …œΒΡΉι÷·ΓΘΕχ

Linux ΒΡ–ιΡβΈΡΦΰœΒΆ≥‘ρΆ≥“ΜΕ‘ΥϋΟ«Ϋχ––ΝΥ≥ιœσΓΘ

―ßœΑLinux…η±Η«ΐΕ·“Σ«σ

Linux …η±Η«ΐΕ·ΒΡ―ßœΑ «“ΜœνΚΤΖ±ΒΡΙΛ≥ΧΘ§ΑϋΚ§»γœ¬÷ΊΒψΓΔΡ―ΒψΓΘ

Γώ ±ύ–¥ Linux …η±Η«ΐΕ·“Σ«σΙΛ≥Χ Π”–Ζ«≥ΘΚΟΒΡ”≤ΦΰΜυ¥ΓΘ§Ε°ΒΟ SRAMΓΔ FlashΓΔ SDRAMΓΔ¥≈≈ΧΒΡΕΝ–¥ΖΫ ΫΘ§

UARTΓΔ I2CΓΔ USB Β»…η±ΗΒΡΫ”ΩΎ“‘ΦΑ¬÷―·ΓΔ÷–ΕœΓΔ DMA ΒΡ‘≠άμΘ§PCI ΉήœΏΒΡΙΛΉςΖΫ Ϋ“‘ΦΑ

CPU ΒΡΡΎ¥φΙήάμΒΞ‘ΣΘ® MMUΘ©Β»

Γώ ±ύ–¥ Linux …η±Η«ΐΕ·“Σ«σΙΛ≥Χ Π”–Ζ«≥ΘΚΟΒΡ C ”ο―‘Μυ¥ΓΘ§ΡήΝιΜνΒΊ‘Υ”Ο C ”ο―‘ΒΡΫαΙΙΧεΓΔ÷Η’κΓΔΚ· ΐ÷Η’κΦΑΡΎ¥φΕ·Χ§…ξ«κΚΆ ΆΖ≈Β»ΓΘ

Γώ ±ύ–¥ Linux …η±Η«ΐΕ·“Σ«σΙΛ≥Χ Π”–“ΜΕ®ΒΡ Linux ΡΎΚΥΜυ¥ΓΘ§Υδ»Μ≤Δ≤Μ“Σ«σΙΛ≥Χ ΠΕ‘ΡΎΚΥΗςΗω≤ΩΖ÷”–…ν»κΒΡ―–ΨΩΘ§ΒΪ÷Ν…Ό“ΣΟςΑΉ«ΐΕ·”κΡΎΚΥΒΡΫ”ΩΎΓΘ”»Τδ «Ε‘”ΎΩι…η±ΗΓΔΆχ¬γ…η±ΗΓΔ

Flash …η±ΗΓΔ¥°ΩΎ…η±ΗΒ»Η¥‘”…η±ΗΘ§ΡΎΚΥΕ®“εΒΡ«ΐΕ·ΧεœΒΫαΙΙ±Ψ…μΨΆΖ«≥ΘΗ¥‘”ΓΘ

Γώ ±ύ–¥ Linux …η±Η«ΐΕ·“Σ«σΙΛ≥Χ Π”–Ζ«≥ΘΚΟΒΡΕύ»ΈΈώ≤ΔΖΔΩΊ÷ΤΚΆΆ§≤ΫΒΡΜυ¥ΓΘ§“ρΈΣ‘Ύ«ΐΕ·÷–Μα¥σΝΩ Ι”ΟΉ‘–ΐΥχΓΔΜΞ≥βΓΔ–≈Κ≈ΝΩΓΔΒ»¥ΐΕ”Ν–Β»≤ΔΖΔ”κΆ§≤ΫΜζ÷ΤΓΘ

«ΐΕ·…ηΦΤ”≤ΦΰΜυ¥Γ

ΒΉ≤ψ«ΐΕ·ΙΛ≥Χ ΠΗζ”≤Φΰ¥ρΫΜΒάΘ§–η“ΣΕ‘«Ε»κ Ϋ”≤Φΰ‘≠άμ“‘ΦΑœύΙΊΈΔΩΊ÷ΤΤςΓΔΈΔ¥ΠάμΤςΓΔ ΐΉ÷–≈Κ≈¥ΠάμΤςΚΆΧΊΕ®Νλ”ρΒΡ¥ΠάμΤςΧεœΒΫαΙΙΚΆ÷ΗΝνΦ·”–ΥυΝΥΫβΓΘ«Ε»κ ΫœΒΆ≥ Ι”ΟΒΡΗςάύ¥φ¥ΔΤςΚΆCPUΫ”ΩΎΘ§Άβ…ηΫ”ΩΎ”κΉήœΏΙΛΉςΖΫ ΫΘ§»γ¥°ΩΎΓΔI2CΓΔSPIΓΔUSBΓΔ“‘ΧΪΆχΫ”ΩΎΓΔPCI/PCIEΓΔSDIOΒ»Θ§ΝμΆβ“≤Μα”ΟΒΫCPLDΚΆFPGAΓΘ ΒΦ ΩΣΖΔΙΐ≥Χ÷––η“ΣGetΒΡΦΦΡήΘΚ

Ω¥Ε°ΚΆΖ÷Έω‘≠άμΆΦ

Βγ¬Ζ ±–ρΖ÷Έω

ΩλΥΌ‘ΡΕΝΚΆΜώ»Γ–ΨΤ§ ΐΨί ÷≤αœύΙΊ–≈œΔ

λœΛ≥Θ”Ο“«Τς“«±μ Ι”ΟΖΫΖ®Θ§Άρ”Ο±μΓΔ Ψ≤®ΤςΓΔ¬ΏΦ≠Ζ÷Έω“«Β»

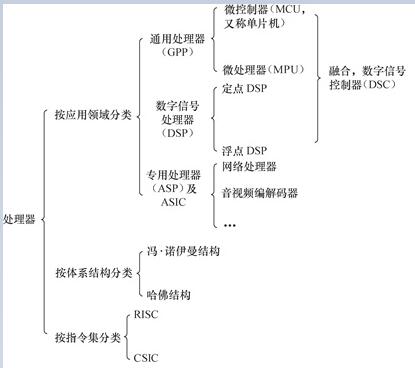

¥ΠάμΤς

Ά®”Ο¥ΠάμΤς

÷ςΝςΒΡΆ®”Ο¥ΠάμΤςΘ® GPPΘ©Εύ≤…”Ο SoCΘ®Τ§…œœΒΆ≥Θ©ΒΡ–ΨΤ§…ηΦΤΖΫΖ®Θ§Φ·≥…ΝΥΗς÷÷ΙΠΡήΡΘΩιΘ§ΟΩ“Μ÷÷ΙΠΡήΕΦ «”…”≤ΦΰΟη ω”ο―‘…ηΦΤ≥Χ–ρΘ§»ΜΚσ‘Ύ

SoC ΡΎ”…Βγ¬Ζ Βœ÷ΒΡΓΘARM ΡΎΚΥΒΡ…ηΦΤΦΦ θ±Μ Ύ»®Ηχ ΐΑΌΦ“ΑκΒΦΧε≥ß…ΧΘ§Ήω≥…≤ΜΆ§ΒΡ SoC –ΨΤ§ΓΘ

ARM ΒΡΙΠΚΡΚήΒΆΘ§‘ΎΒ±ΫώΉνΜν‘ΨΒΡΈόœΏΨ÷”ρΆχΓΔ 3GΓΔ ÷Μζ÷’ΕΥΓΔ ÷≥÷…η±ΗΓΔ”–œΏΆχ¬γΆ®–≈…η±ΗΒ»÷–”Π”ΟΖ«≥ΘΙψΖΚΓΘ÷Ν±Ψ ι±ύ–¥ ±Θ§ –Οφ…œΨχ¥σΕύ ΐ÷«Ρή ÷ΜζΓΔΤΫΑεΒγΡ‘ΕΦ Ι”Ο

ARM SoC ΉςΈΣ÷ς–ΨΤ§ΓΘΚήΕύ ARM ÷ςΩΊ–ΨΤ§ΒΡΦ·≥…Ε»Ζ«≥ΘΗΏΘ§≥ΐΝΥΦ·≥…ΕύΚΥ ARM “‘ΆβΘ§ΜΙΩ…ΡήΦ·≥…ΆΦ–Έ¥ΠάμΤςΓΔ ”ΤΒ±ύΫβ¬κΤςΓΔΗΓΒψ–≠¥ΠάμΤςΓΔ

GPSΓΔ WiFiΓΔάΕ―άΓΔΜυ¥χΓΔ Camera Β»“ΜœΒΝ–ΙΠΡήΓΘ –≥Γ±»Ϋœ≥ΘΦϊΒΡARM–ΨΤ§ΧαΙ©…ΧΑϋά®ΗΏΆ®ΓΔ»ΐ–«ΓΔ”ΔΈΑ¥οΓΔΝΣΖΔΩΤΓΔΚΘΥΦΓΔΒ¬÷ί“«ΤςΓΔ≤©Ά®Β»Β»ΓΘ

÷–―κ¥ΠάμΤςΒΡΧεœΒΫαΙΙΩ…“‘Ζ÷ΈΣΝΫάύΘ§“ΜάύΈΣΖκΓΛ ≈Β“ά¬ϋΫαΙΙΘ§Νμ“ΜάύΈΣΙΰΖπΫαΙΙΓΘ Intel ΙΪΥΨΒΡ÷–―κ¥ΠάμΤςΓΔ

ARM ΒΡ ARM7ΓΔ MIPS ΙΪΥΨΒΡ MIPS¥Π άμ Τς ≤… ”ΟΝΥΖκΓΛ≈Β “ά¬ϋΫαΙΙΘΜ ΕχAVRΓΔ

ARM9ΓΔ ARM10ΓΔ ARM11 “‘ ΦΑCortex A œΒΝ–Β»‘ρ≤…”ΟΝΥΙΰΖπΫαΙΙΓΘΖκΓΛ≈Β“ά¬ϋΫαΙΙ“≤≥ΤΤ’Ν÷ΥΙΕΌΫαΙΙΘ§ «“Μ÷÷ΫΪ≥Χ–ρ÷ΗΝν¥φ¥ΔΤςΚΆ ΐΨί¥φ¥ΔΤςΚœ≤Δ‘Ύ“ΜΤπΒΡ¥φ¥ΔΤςΫαΙΙΓΘ≥Χ–ρ÷ΗΝν¥φ¥ΔΒΊ÷ΖΚΆ ΐΨί¥φ¥ΔΒΊ÷Ζ÷ΗœρΆ§“ΜΗω¥φ¥ΔΤςΒΡ≤ΜΆ§ΈοάμΈΜ÷ΟΘ§“ρ¥Υ≥Χ–ρ÷ΗΝνΚΆ ΐΨίΒΡΩμΕ»œύΆ§ΓΘ

ΕχΙΰΖπΫαΙΙΫΪ≥Χ–ρ÷ΗΝνΚΆ ΐΨίΖ÷ΩΣ¥φ¥ΔΘ§÷ΗΝνΚΆ ΐΨίΩ…“‘”–≤ΜΆ§ΒΡ ΐΨίΩμΕ»ΓΘ¥ΥΆβΘ§ΙΰΖπΫαΙΙΜΙ≤…”ΟΝΥΕάΝΔΒΡ≥Χ–ρΉήœΏΚΆ ΐΨίΉήœΏΘ§Ζ÷±πΉςΈΣ

CPU ”κΟΩΗω¥φ¥ΔΤς÷°ΦδΒΡΉ®”ΟΆ®–≈¬ΖΨΕΘ§ΨΏ”–ΫœΗΏΒΡ÷¥–––߬ ΓΘ

–μΕύ–ΨΤ§≤…”ΟΒΡ «œ¬ΆΦΥυ ΨΒΡΗΡΫχΒΡΙΰΖπΦήΙΙΘ§ΥϋΨΏ”–ΕάΝΔΒΡΒΊ÷ΖΉήœΏΚΆ ΐΨίΉήœΏΘ§ΝΫΧθΉήœΏ”…≥Χ–ρ¥φ¥ΔΤςΚΆ ΐΨί¥φ¥ΔΤςΖ÷ ±Ι≤”ΟΓΘ“ρ¥ΥΘ§ΗΡΫχΒΡΙΰΖπΫαΙΙ’κΕ‘≥Χ–ρΚΆ ΐΨίΘ§Τδ ΒΟΜ”–ΕάΝΔΒΡΉήœΏΘ§Εχ « Ι”ΟΙΪ”Ο ΐΨίΉήœΏά¥Άξ≥…≥Χ–ρ¥φ¥ΔΡΘΩιΜρ ΐΨί¥φ¥ΔΡΘΩι”κ

CPU ÷°ΦδΒΡ ΐΨί¥Ϊ δΘ§ΙΪ”ΟΒΡΒΊ÷ΖΉήœΏά¥―Α÷Ζ≥Χ–ρΚΆ ΐΨίΓΘ

ΐΉ÷–≈Κ≈¥ΠάμΤς

ΐΉ÷–≈Κ≈¥ΠάμΤςΘ®DSPΘ©’κΕ‘Ά®–≈ΓΔΆΦœώΓΔ”ο“τΚΆ ”ΤΒ¥ΠάμΒ»Νλ”ρΒΡΥψΖ®Εχ…ηΦΤΓΘΥϋΑϋΚ§ΕάΝΔΒΡ”≤Φΰ≥ΥΖ®ΤςΓΘ

DSP ΒΡ≥ΥΖ®÷ΗΝν“ΜΑψ‘ΎΒΞ÷ήΤΎΡΎΆξ≥…Θ§«“”≈Μ·ΝΥΨμΜΐΓΔ ΐΉ÷¬Υ≤®ΓΔFFTΘ®ΩλΥΌΗΒάο“Ε±δΜΜΘ©ΓΔœύΙΊΨΊ’σ‘ΥΥψΒ»ΥψΖ®÷–ΒΡ¥σΝΩ÷ΊΗ¥≥ΥΖ®ΓΘ

DSP Ζ÷ΈΣΝΫάύΘ§“Μάύ «Ε®Βψ DSPΘ§Νμ“Μάύ «ΗΓΒψ DSPΓΘΗΓΒψ DSP ΒΡΗΓΒψ‘ΥΥψ”Ο”≤Φΰά¥ Βœ÷Θ§Ω…“‘‘ΎΒΞ÷ήΤΎΡΎΆξ≥…Θ§“ρΕχΤδΗΓΒψ‘ΥΥψ¥ΠάμΥΌΕ»ΗΏ”ΎΕ®Βψ

DSPΓΘΕχΕ®Βψ DSP ÷ΜΡή”ΟΕ®Βψ‘ΥΥψΡΘΡβΗΓΒψ‘ΥΥψΓΘ

Β¬÷ί“«ΤςΘ® TIΘ©ΓΔΟάΙζΡΘΡβΤςΦΰΙΪΥΨΘ® ADIΘ© «»Ϊ«ρ DSP ΒΡΝΫ¥σ÷ς“Σ≥ß…ΧΓΘ

Εύ¥ΠάμΤς»ΎΚœ

Ά®”Ο¥ΠάμΤςΚΆ ΐΉ÷–≈Κ≈¥ΠάμΤςΘ§…θ÷ΝΉιΚœΚΆ ±–ρ¬ΏΦ≠CPLDΓΔFPGA»ΎΚœΩ…“‘»Γ≥Λ≤ΙΕΧΘ§»γTI–ΨΤ§≥ß…ΧΧαΙ©ΒΡARM+DSPΥΪΚΥ“‘ΦΑΕύΚΥARMΓΔDSP¥ΠάμΤςΘ§ΡΎ≤ΩΜΙΦ·≥…Ή®”ΟΒΡ“τ ”ΤΒΆΦœώ±ύΫβ¬κΚΆISPΘ§ΨΏΧε–ΨΤ§”–DM365/368/386,DM6467,DM8168,DM8127Θ§DM6657/6455Β»Θ§ΕΦ «”Ο”Ύ ”ΤΒΆΦœώ¥ΠάμΝλ”ρΘ§ΝμΆβAltera”κXilinx

ARM+FPGAΒΡSOCΘ§“≤”Ο”Ύ ”ΤΒΦύΩΊΓΔΤϊ≥ΒΗ®÷ζΦί Μ“‘ΦΑΙΛ≥ΧΉ‘Ε·Μ·Β»ΓΘ

¥φ¥ΔΤς

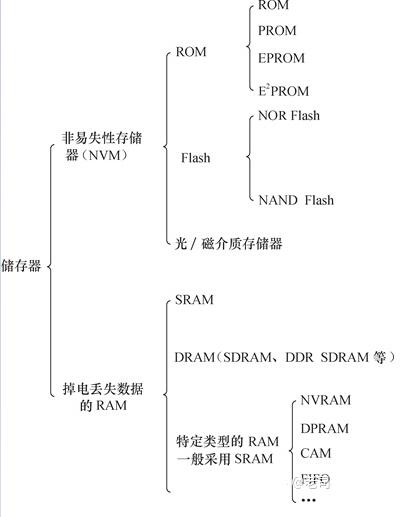

¥φ¥ΔΤς÷ς“ΣΩ…Ζ÷άύΈΣ÷ΜΕΝ¥Δ¥φΤςΘ® ROMΘ©ΓΔ…Ν¥φΘ® FlashΘ©ΓΔΥφΜζ¥φ»Γ¥φ¥ΔΤςΘ® RAMΘ©ΓΔΙβ /¥≈Ϋι÷ ¥Δ¥φΤςΓΘ

ROM ΜΙ Ω… ‘Ό œΗ Ζ÷ ΈΣ ≤Μ Ω… ±ύ ≥Χ ROMΓΔ Ω… ±ύ ≥Χ ROMΘ® PROMΘ©ΓΔ Ω…

≤Ν ≥ΐΩ… ±ύ ≥Χ ROMΘ® EPROMΘ©ΚΆΒγΩ…≤Ν≥ΐΩ…±ύ≥Χ ROMΘ® E2PROMΘ©Θ§ E2PROM

Άξ»ΪΩ…“‘”Ο»μΦΰά¥≤Ν–¥Θ§“―Ψ≠Ζ«≥ΘΖΫ±ψΝΥΓΘ

NORΘ®ΜρΖ«Θ©ΚΆ NANDΘ®”κΖ«Θ© « –≥Γ…œΝΫ÷÷÷ς“ΣΒΡ Flash …Ν¥φΦΦ θΓΘΒδ–ΆΒΡάύSRAMΫ”ΩΎ»γœ¬ΆΦΥυ ΨΘΚ

Ης÷÷ ROMΓΔ Flash ΚΆ¥≈Ϋι÷ ¥φ¥ΔΤςΕΦ τ”ΎΖ«“Ή ß–‘¥φ¥ΔΤςΘ® NVMΘ©ΒΡΖΕ≥κΘ§

ΒτΒγ ±–≈œΔ≤ΜΜαΕΣ ßΘ§Εχ RAM ‘ρ”κ¥ΥœύΖ¥ΓΘ

RAM “≤Ω…‘ΌΖ÷ΈΣΨ≤Χ§ RAMΘ® SRAMΘ©ΚΆΕ·Χ§ RAMΘ® DRAMΘ©ΓΘ DRAM “‘ΒγΚ…–Έ ΫΫχ

––¥φ¥ΔΘ§ ΐΨί¥φ¥Δ‘ΎΒγ»ίΤς÷–ΓΘ”…”ΎΒγ»ίΤςΜα“ρ¬©ΒγΕχ≥ωœ÷ΒγΚ…ΕΣ ßΘ§Υυ“‘ DRAM ΤςΦΰ–η

“ΣΕ®ΤΎΥΔ–¬ΓΘ SRAM «Ψ≤Χ§ΒΡΘ§÷Μ“ΣΙ©ΒγΥϋΨΆΜα±Θ≥÷“ΜΗω÷ΒΘ§ SRAM ΟΜ”–ΥΔ–¬÷ήΤΎΓΘΟΩΗω

SRAM ¥φ¥ΔΒΞ‘Σ”… 6 ΗωΨßΧεΙήΉι≥…Θ§Εχ DRAM ¥φ¥ΔΒΞ‘Σ”… 1 ΗωΨßΧεΙήΚΆ 1 ΗωΒγ»ίΤςΉι≥…ΓΘ

Ης¥φ¥ΔΤςΖ÷άύ»γœ¬ΆΦΥυ ΨΘΚ

Ϋ”ΩΎΚΆΉήœΏ

¥°ΩΎ

RS-232ΓΔ RS-422 ”κ RS-485 ΕΦ «¥°–– ΐΨίΫ”ΩΎ±ξΉΦΘ§RS-232C ±ξΉΦΫ”ΩΎ”– 25ΧθœΏΘ®

4 Χθ ΐΨίœΏΓΔ 11 ΧθΩΊ÷ΤœΏΓΔ 3 ΧθΕ® ±œΏΓΔ 7 Χθ±Η”ΟΚΆΈ¥Ε®“εœΏΘ©Θ§≥Θ”ΟΒΡ÷Μ”– 9 ΗυΘ§ΥϋΟ« «

RTS/CTSΘ®«κ«σΖΔΥΆ / «ε≥ΐΖΔΥΆΝςΩΊ÷ΤΘ©ΓΔ RxD/TxDΘ® ΐΨί ’ΖΔΘ©ΓΔ DSR/DTRΘ® ΐΨί÷’ΕΥΨΆ–ς

/ ΐΨί…η÷ΟΨΆ–ςΝςΩΊ÷ΤΘ©ΓΔ DCDΘ® ΐΨί‘Ί≤®Φλ≤βΘ§“≤≥Τ RLSDΘ§Φ¥Ϋ” ’œΏ–≈Κ≈Φλ≥ωΘ©ΓΔRinging-RIΘ®’ώΝε÷Η ΨΘ©ΓΔ

SGΘ®–≈Κ≈ΒΊΘ©–≈Κ≈ΓΘ RTS/CTSΓΔ RxD / TxDΓΔ DSR/DTR Β»–≈Κ≈ΒΡΕ®“ε»γœ¬ΓΘ

Γώ RTSΘΚ”Οά¥±μ Ψ DTE «κ«σ DCE ΖΔΥΆ ΐΨίΘ§Β±÷’ΕΥ“ΣΖΔΥΆ ΐΨί ±Θ§ ΙΗΟ–≈Κ≈”––ßΓΘ

Γώ CTSΘΚ”Οά¥±μ Ψ DCE ΉΦ±ΗΚΟΫ” ’ DTE ΖΔά¥ΒΡ ΐΨίΘ§ «Ε‘ RTS ΒΡœλ”Π–≈Κ≈ΓΘ

Γώ RxDΘΚ DTE Ά®Ιΐ RxD Ϋ” ’¥” DCE ΖΔά¥ΒΡ¥°–– ΐΨίΓΘ

Γώ TxDΘΚ DTE Ά®Ιΐ TxD ΫΪ¥°–– ΐΨίΖΔΥΆΒΫ DCEΓΘ

Γώ DSRΘΚ”––ßΘ® ON Ή¥Χ§Θ©±μΟς DCE Ω…“‘ Ι”ΟΓΘ

Γώ DTRΘΚ”––ßΘ® ON Ή¥Χ§Θ©±μΟς DTE Ω…“‘ Ι”ΟΓΘ

Γώ DCD ΘΚΒ±±ΨΒΊ DCE …η±Η ’ΒΫΕ‘ΖΫ DCE …η±ΗΥΆά¥ΒΡ‘Ί≤®–≈Κ≈ ±Θ§ Ι DCD ”––ßΘ§Ά®÷Σ

DTE ΉΦ±ΗΫ” ’Θ§≤Δ«“”… DCE ΫΪΫ” ’ΒΫΒΡ‘Ί≤®–≈Κ≈ΫβΒςΈΣ ΐΉ÷–≈Κ≈Θ§Ψ≠ RxD œΏΥΆΗχ

DTEΓΘ

Γώ Ringing-RIΘΚΒ±Βς÷ΤΫβΒςΤς ’ΒΫΫΜΜΜΧ®ΥΆά¥ΒΡ’ώΝεΚτΫ––≈Κ≈ ±Θ§ ΙΗΟ–≈Κ≈”––ßΘ® ON Ή¥

Χ§Θ©Θ§Ά®÷Σ÷’ΕΥΘ§“―±ΜΚτΫ–ΓΘ

ΉνΦρΒΞΒΡ RS-232C ¥°ΩΎ÷Μ–η“ΣΝ§Ϋ” RxDΓΔ TxDΓΔ SG ’β 3 Ηω–≈Κ≈Θ§≤Δ Ι”Ο XON/XOFF

»μ

ΦΰΝςΩΊΓΘ

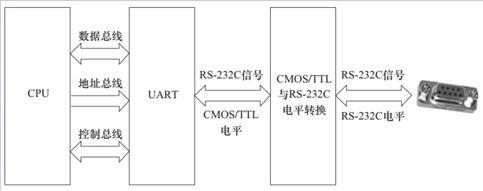

Ήι≥…“ΜΗω RS-232C ¥°ΩΎΒΡ”≤Φΰ‘≠άμ»γœ¬ΆΦΥυ ΨΘ§¥” CPU ΒΫΝ§Ϋ”Τς“ά¥ΈΈΣ CPUΓΔ UARTΘ®Ά®”Ο“λ≤ΫΫ” ’ΤςΖΔΥΆΤςΘ§Ής”Ο «Άξ≥…≤Δ

/ ¥°ΉΣΜΜΘ©ΓΔ CMOS/TTL ΒγΤΫ”κ RS-232C ΒγΤΫΉΣΜΜΓΔDB9/DB25 ΜρΉ‘Ε®“εΝ§Ϋ”ΤςΓΘ

I2C

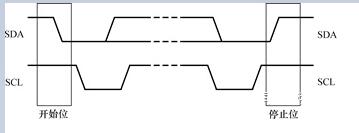

Ήι≥… I2C ΉήœΏΒΡΝΫΗω–≈Κ≈ΈΣ ΐΨίœΏ SDA ΚΆ ±÷” SCLΓΘΈΣΝΥ±ήΟβΉήœΏ–≈Κ≈ΒΡΜ묓ȧ“Σ«σΗς

…η±ΗΝ§Ϋ”ΒΫΉήœΏΒΡ δ≥ωΕΥ±Ί–κ «ΩΣ¬© δ≥ωΜρΦ·ΒγΦΪΩΣ¬Ζ δ≥ωΒΡΫαΙΙΓΘΉήœΏΩ’œ– ±Θ§…œά≠ΒγΉη Ι SDA ΚΆ SCL

œΏΕΦ±Θ≥÷ΗΏΒγΤΫΓΘΗυΨίΩΣ¬© δ≥ωΜρΦ·ΒγΦΪΩΣ¬Ζ δ≥ω–≈Κ≈ΒΡΓΑœΏ”κΓ±¬ΏΦ≠Θ§ I2CΉήœΏ…œ»Έ“βΤςΦΰ δ≥ωΒΆΒγΤΫΕΦΜα Ιœύ”ΠΉήœΏ…œΒΡ–≈Κ≈œΏ±δΒΆ.

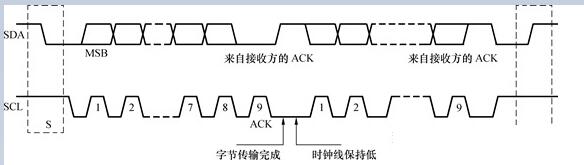

I2C …η±Η…œΒΡ¥°–– ΐΨίœΏ SDA Ϋ”ΩΎΒγ¬Ζ «ΥΪœρΒΡΘ§ δ≥ωΒγ¬Ζ”Ο”ΎœρΉήœΏ…œΖΔΥΆ ΐΨίΘ§ δ»κΒγ¬Ζ”Ο”ΎΫ” ’ΉήœΏ…œΒΡ ΐΨίΓΘΆ§―υΒΊΘ§¥°–– ±÷”œΏ

SCL “≤ «ΥΪœρΒΡΘ§ΉςΈΣΩΊ÷ΤΉήœΏ ΐΨί¥ΪΥΆΒΡ÷ςΜζ“ΣΆ®Ιΐ SCL δ≥ωΒγ¬ΖΖΔΥΆ ±÷”–≈Κ≈Θ§≤ΔΦλ≤βΉήœΏ…œ SCL

…œΒΡΒγΤΫ“‘ΨωΕ® ≤Ο¥ ±ΚρΖΔœ¬“ΜΗω ±÷”¬ω≥εΒγΤΫΘΜΉςΈΣΫ” ’÷ςΜζΟϋΝνΒΡ¥”…η±Η–ηΑ¥ΉήœΏ…œ SCL ΒΡ–≈Κ≈ΖΔΥΆΜρΫ” ’SDA

…œΒΡ–≈Κ≈Θ§Υϋ“≤Ω…“‘œρ SCL œΏΖΔ≥ωΒΆΒγΤΫ–≈Κ≈“‘―”≥ΛΉήœΏ ±÷”–≈Κ≈÷ήΤΎΓΘΒ± SCL Έ»Ε®‘ΎΗΏΒγΤΫ ±Θ§

SDA ”…ΗΏΒΫΒΆΒΡ±δΜ·ΫΪ≤ζ…ζ“ΜΗωΩΣ ΦΈΜΘ§Εχ”…ΒΆΒΫΗΏΒΡ±δΜ·‘ρ≤ζ…ζ“ΜΗωΆΘ÷ΙΈΜΘ§»γœ¬ΆΦΥυ ΨΓΘ

ΩΣ ΦΈΜΚΆΆΘ÷ΙΈΜΕΦ”… I2C ÷ς…η±Η≤ζ…ζΓΘ‘Ύ―Γ‘ώ¥”…η±Η ±Θ§»γΙϊ¥”…η±Η≤…”Ο 7 ΈΜΒΊ÷ΖΘ§‘ρ÷ς…η±Η‘ΎΖΔΤπ¥Ϊ δΙΐ≥Χ«ΑΘ§–ηœ»ΖΔΥΆ

1 Ή÷ΫΎΒΡΒΊ÷Ζ–≈œΔΘ§«Α 7 ΈΜΈΣ…η±ΗΒΊ÷ΖΘ§ΉνΚσ 1 ΈΜΈΣΕΝ–¥±ξ÷ΨΓΘ÷°ΚσΘ§ΟΩ¥Έ¥Ϊ δΒΡ ΐΨί“≤ « 1 Ή÷ΫΎΘ§¥”

MSB ΩΣ Φ¥Ϊ δΓΘΟΩΗωΉ÷ΫΎ¥ΪΆξΚσΘ§‘Ύ SCL30 ΒΡΒΎ 9 Ηω…œ…ΐ―ΊΒΫά¥÷°«ΑΘ§Ϋ” ’ΖΫ”ΠΗΟΖΔ≥ω 1 Ηω

ACK ΈΜΓΘ SCL …œΒΡ ±÷”¬ω≥ε”… I2C ÷ςΩΊΖΫΖΔ≥ωΘ§‘ΎΒΎ 8 Ηω ±÷”÷ήΤΎ÷°ΚσΘ§÷ςΩΊΖΫ”ΠΗΟ ΆΖ≈

SDAΘ§ I2C ΉήœΏΒΡ ±–ρ»γœ¬ΆΦΥυ ΨΓΘ

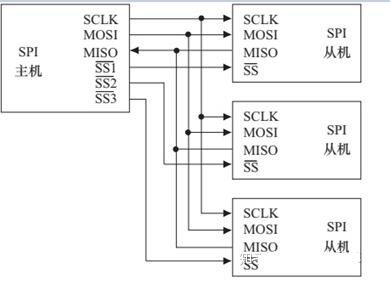

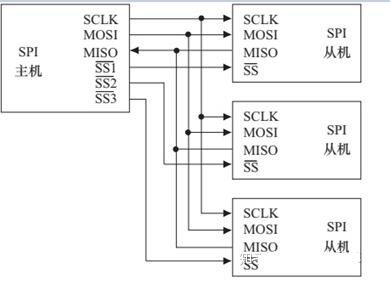

SPI

SPIΘ® Serial Peripheral InterfaceΘ§¥°––Άβ…ηΫ”ΩΎΘ©ΉήœΏœΒΆ≥ «“Μ÷÷Ά§≤Ϋ¥°––Άβ…ηΫ”ΩΎΘ§

ΥϋΩ…“‘ Ι CPU ”κΗς÷÷ΆβΈß…η±Η“‘¥°––ΖΫ ΫΫχ–– Ά® –≈ “‘ ΫΜ ΜΜ –≈ œΔΓΘ “Μ Αψ ÷ς ΩΊ SoC

Ής ΈΣSPI ΒΡΓΑ÷ςΓ±Θ§ΕχΆβ…ηΉςΈΣ SPI ΒΡΓΑ¥”Γ±ΓΘSPI Ϋ”ΩΎ“ΜΑψ Ι”Ο 4 ΧθœΏΘΚ¥°–– ±÷”œΏΘ®

SCLKΘ©ΓΔ÷ςΜζ δ»κ / ¥”Μζ δ≥ω ΐΨίœΏMISOΓΔ÷ςΜζ δ≥ω / ¥”Μζ δ»κ ΐΨίœΏ MOSIΚΆΒΆΒγΤΫ”––ßΒΡ¥”Μζ―Γ‘ώœΏ

SSΘ®‘Ύ≤ΜΆ§ΒΡΈΡœΉάοΘ§“≤≥Θ≥ΤΈΣ nCSΓΔ CSΓΔ CSBΓΔ CSNΓΔnSSΓΔ STEΓΔ SYNC Β»Θ©ΓΘ

œ¬ΆΦ―ί Ψ ΝΥ 1Ηω÷ςΜζΝ§Ϋ” 3 Ηω SPI Άβ…ηΒΡ”≤ΦΰΝ§Ϋ”ΆΦΓΘ

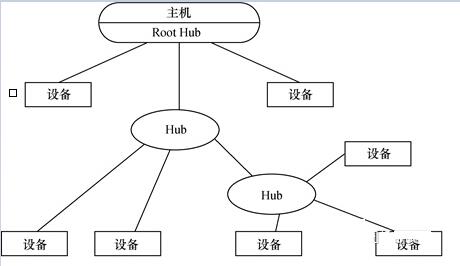

USB

USBΘ®Ά®”Ο¥°––ΉήœΏΘ© « IntelΓΔ Microsoft Β»≥ß…ΧΈΣΫβΨωΦΤΥψΜζΆβ…η÷÷άύΒΡ»’“φ‘ωΦ””κ”–œόΒΡ÷ςΑε≤ε≤έΚΆΕΥΩΎ÷°ΦδΒΡΟ§ΕήΕχ”Ύ

1995 ΡξΧα≥ωΒΡΘ§ΥϋΨΏ”– ΐΨί¥Ϊ δ¬ ΗΏΓΔ“Ήά©’ΙΓΔ÷ß≥÷Φ¥≤εΦ¥”ΟΚΆ»»≤εΑΈΒΡ”≈ΒψΘ§ΡΩ«Α“―ΒΟΒΫΙψΖΚ”Π”ΟΓΘ

USB 1.1 ΑϋΚ§»ΪΥΌΚΆΒΆΥΌΝΫ÷÷ΡΘ ΫΘ§ΒΆΥΌΖΫ ΫΒΡΥΌ¬ ΈΣ 1.5Mbit/sΘ§÷ß≥÷“Μ–©≤Μ–η“ΣΚή¥σ ΐΨίΆΧΆ¬ΝΩΚΆΚήΗΏ Β ±–‘ΒΡ…η±ΗΘ§»γ σ±ξΒ»ΓΘ»ΪΥΌΡΘ ΫΈΣ

12Mbit/sΘ§Ω…“‘ΆβΫ”ΥΌ¬ ΗϋΗΏΒΡΆβ…ηΓΘ‘Ύ USB 2.0 ÷–Θ§‘ωΦ”ΝΥ“Μ÷÷ΗΏΥΌΖΫ ΫΘ§ ΐΨί¥Ϊ δ¬ ¥οΒΫ

480Mbit/sΘ§ΑκΥΪΙΛΘ§Ω…“‘¬ζΉψΗϋΗΏΥΌΆβ…ηΒΡ–η“ΣΓΘΕχ USB 3.0Θ®“≤±Μ»œΈΣ « Super Speed

USBΘ©ΒΡΉν¥σ¥Ϊ δ¥χΩμΗΏ¥ο 5.0Gbit/sΘ®Φ¥ 640MB/sΘ©Θ§»ΪΥΪΙΛΓΘ

USB 2.0 ΉήœΏΒΡΜζ–ΒΝ§Ϋ”Ζ«≥ΘΦρΒΞΘ§≤…”Ο 4 –ΨΒΡΤΝ±ΈœΏΘ§“ΜΕ‘≤νΖ÷œΏΘ® D+ΓΔ D-Θ©¥ΪΥΆ–≈Κ≈Θ§Νμ“ΜΕ‘Θ®

VBUSΓΔΒγ‘¥ΒΊΘ©¥ΪΥΆ +5V ΒΡ÷±ΝςΒγΓΘ USB 3.0 œΏά¬‘ρ…ηΦΤΝΥ 8 ΧθΡΎ≤ΩœΏ¬ΖΘ§≥ΐVBUSΓΔΒγ‘¥ΒΊ÷°ΆβΘ§Τδ”ύ

3 Ε‘ΨυΈΣ ΐΨί¥Ϊ δœΏ¬ΖΓΘΤδ÷–±ΘΝτΝΥ D+ ”κ D- ’βΝΫΧθΦφ»ί USB2.0 ΒΡœΏ¬ΖΘ§–¬‘ωΝΥ SSRX

”κ SSTX Ή®ΈΣ USB 3.0 Υυ…ηΒΡœΏ¬ΖΓΘ

‘Ύ«Ε»κ ΫœΒΆ≥÷–Θ§Βγ¬ΖΑε»τ–η“ΣΙ“Ϋ” USB …η±ΗΘ§‘ρ–ηΧαΙ© USB ÷ςΜζΘ® HostΘ©ΩΊ÷ΤΤςΚΆΝ§Ϋ”ΤςΘΜ»τΒγ¬ΖΑε–η“ΣΉςΈΣ

USB …η±ΗΘ§‘ρ–ηΧαΙ© USB …η±Η ≈δΤςΚΆΝ§Ϋ”ΤςΓΘΡΩ«ΑΘ§¥σΕύ ΐSoC Φ·≥…ΝΥ USB ÷ςΜζΩΊ÷ΤΤςΘ®

“‘Ν§Ϋ” USB Άβ…ηΘ©ΚΆ…η±Η ≈δΤςΘ®“‘ΫΪ±Ψ«Ε»κ ΫœΒΆ≥ΉςΈΣΤδΥϊΦΤΥψΜζœΒΆ≥ΒΡ USB Άβ…ηΘ§»γ ÷Μζ≥δΒ±

U ≈ΧΘ©ΓΘ”… USB ÷ςΜζΓΔ…η±ΗΚΆ Hub Ήι≥…ΒΡ USB œΒΆ≥ΒΡΈοάμΆΊΤΥΫαΙΙ»γœ¬ΆΦΥυ ΨΓΘ

ΟΩ“ΜΗω USB …η±ΗΜα”–“ΜΗωΜρ’ΏΕύΗω¬ΏΦ≠Ν§Ϋ”Βψ‘ΎάοΟφΘ§ΟΩΗωΝ§Ϋ”ΒψΫ–ΕΥΒψΓΘ USB ΧαΙ©ΝΥΕύ÷÷¥Ϊ δΖΫ Ϋ“‘ ”ΠΗς÷÷…η±ΗΒΡ–η“ΣΘ§“ΜΗωΕΥΒψΩ…“‘―Γ‘ώ»γœ¬“Μ÷÷¥Ϊ δΖΫ ΫΓΘ

ΩΊ÷ΤΘ®ControlΘ©¥Ϊ δΖΫ Ϋ

ΩΊ÷Τ¥Ϊ δ «ΥΪœρ¥Ϊ δΘ§ ΐΨίΝΩΆ®≥ΘΫœ–ΓΘ§÷ς“Σ”Οά¥Ϋχ––≤ι―·ΓΔ≈δ÷ΟΚΆΗχ USB …η±ΗΖΔΥΆΆ®”ΟΟϋΝνΓΘΥυ”– USB

…η±Η±Ί–κ÷ß≥÷±ξΉΦ«κ«σΘ® Standard RequestΘ©Θ§ΩΊ÷Τ¥Ϊ δΖΫ ΫΚΆΕΥΒψ 0ΓΘ

Ά§≤ΫΘ®IsochronousΘ©¥Ϊ δΖΫ Ϋ

Ά§≤Ϋ¥Ϊ δΧαΙ©ΝΥ»ΖΕ®ΒΡ¥χΩμΚΆΦδΗτ ±ΦδΘ§Υϋ”Ο”Ύ ±Φδ“Σ«σ―œΗώ≤ΔΨΏ”–Ϋœ«Ω»ί¥μ–‘ΒΡΝς ΐ

Ψί¥Ϊ δΘ§Μρ’Ώ”Ο”Ύ“Σ«σΚψΕ® ΐΨί¥ΪΥΆ¬ ΒΡΦ¥ ±”Π”ΟΓΘάΐ»γΫχ––”ο“τ“ΒΈώ¥Ϊ δ ±Θ§ Ι”ΟΆ§≤Ϋ¥Ϊ

δΖΫ Ϋ «ΚήΚΟΒΡ―Γ‘ώΓΘΆ§≤Ϋ¥Ϊ δ“≤≥Θ≥ΤΈΣΓΑ Streaming Real-timeΓ±¥Ϊ δΓΘ

÷–ΕœΘ®InterruptΘ©¥Ϊ δΖΫ Ϋ

÷–ΕœΖΫ Ϋ¥ΪΥΆ «ΒΞœρΒΡΘ§Ε‘”Ύ USB ÷ςΜζΕχ―‘Θ§÷Μ”– δ»κΓΘ÷–Εœ¥Ϊ δΖΫ Ϋ÷ς“Σ”Ο”ΎΕ® ±≤ι―·…η±Η «Ζώ”–÷–Εœ ΐΨί“Σ¥ΪΥΆΘ§ΗΟ¥Ϊ δΖΫ Ϋ”Π”Ο‘Ύ…ΌΝΩΖ÷…ΔΒΡΓΔ≤ΜΩ…‘Λ≤βΒΡ ΐΨί¥Ϊ δ≥ΓΚœΘ§

Φϋ≈ΧΓΔ”ΈœΖΗΥΚΆ σ±ξ τ”Ύ’β“Μάύ–ΆΓΘ

≈ζΝΩΘ®BulkΘ©¥Ϊ δΖΫ Ϋ

≈ζΝΩ¥Ϊ δ÷ς“Σ”Π”Ο‘ΎΟΜ”–¥χΩμΓΔΦδΗτ ±Φδ“Σ«σΒΡ≈ζΝΩ ΐΨίΒΡ¥ΪΥΆΚΆΫ” ’÷–Θ§Υϋ“Σ«σ±Θ÷Λ

¥Ϊ δΓΘ¥ρ”ΓΜζΚΆ…®Οη“« τ”Ύ’β÷÷άύ–ΆΓΘΕχ USB 3.0 ‘ρ‘ωΦ”ΝΥ“Μ÷÷ Bulk Streams ¥Ϊ δΡΘ ΫΘ§

USB 2.0 ΒΡ Bulk ΡΘ Ϋ÷Μ÷ß≥÷ 1 Ηω ΐΨίΝςΘ§Εχ Bulk Streams ¥Ϊ δΡΘ Ϋ‘ρΩ…“‘÷ß≥÷ΕύΗω ΐΨίΝςΘ§ΟΩΗω ΐΨίΝς±ΜΖ÷≈δ“ΜΗω

Stream IDΘ® SIDΘ©Θ§ΟΩΗω SID ”κ“ΜΗω÷ςΜζΜΚ≥ε«χΕ‘”ΠΓΘ

‘ΎUSB ΦήΙΙ÷–Θ§Φ·œΏΤςΗΚ‘πΦλ≤β…η±ΗΒΡΝ§Ϋ”ΚΆΕœΩΣΘ§άϊ”ΟΤδ÷–Εœ IN ΕΥΒψΘ® Interrupt INEndpointΘ©ά¥œρ÷ςΜζ±®ΗφΓΘ“ΜΒ©ΜώœΛ”––¬…η±ΗΝ§Ϋ”…œά¥Θ§÷ςΜζΨΆΜαΖΔΥΆ“ΜœΒΝ–«κ«σΗχ…η±ΗΥυΙ“‘ΊΒΡΦ·œΏΤςΘ§‘Ό”…Φ·œΏΤςΫ®ΝΔΤπ“ΜΧθΝ§Ϋ”÷ςΜζΚΆ…η±Η÷°ΦδΒΡΆ®–≈Ά®ΒάΓΘ»ΜΚσ÷ςΜζ“‘ΩΊ÷Τ¥Ϊ δΒΡΖΫ ΫΘ§Ά®ΙΐΕΥΒψ

0 Ε‘…η±ΗΖΔΥΆΗς÷÷«κ«σΘ§…η±Η ’ΒΫ÷ςΜζΖΔά¥ΒΡ«κ«σΚσΜΊΗ¥œύ”ΠΒΡ–≈œΔΘ§Ϋχ––ΟΕΨΌΘ® EnumerateΘ©≤ΌΉςΓΘ“ρ¥Υ

USB ΉήœΏΨΏ±Η»»≤εΑΈΒΡΡήΝΠΓΘ

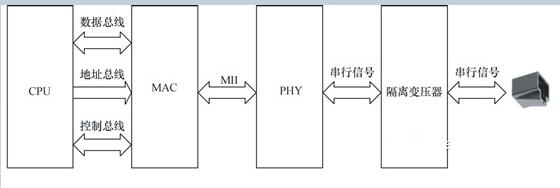

“‘ΧΪΆχΫ”ΩΎ

“‘ΧΪΆχΫ”ΩΎ”… MACΘ®“‘ΧΪΆχΟΫΧεΫ”»κΩΊ÷ΤΤςΘ©ΚΆ PHYΘ®ΈοάμΫ”ΩΎ ’ΖΔΤςΘ©Ήι≥…ΓΘ“‘ΧΪ

Άχ MAC ”… IEEE 802.3 “‘ΧΪΆχ±ξΉΦΕ®“εΘ§ Βœ÷ΝΥ ΐΨίΝ¥¬Ζ≤ψΓΘ≥Θ”ΟΒΡ MAC ÷ß≥÷ 10Mbit/s

Μρ100Mbit/s ΝΫ÷÷ΥΌ¬ ΓΘΦΣ±»ΧΊ“‘ΧΪΆχΘ®“≤≥ΤΈΣ«ß’ΉΈΜ“‘ΧΪΆχΘ© «ΩλΥΌ“‘ΧΪΆχΒΡœ¬“Μ¥ζΦΦ θΘ§ΫΪΆχΥΌΧαΗΏΒΫΝΥ

1000 Mbit/sΓΘ«ß’ΉΈΜ“‘ΧΪΆχ“‘ IEEE 802.3z ΚΆ 802.3ab ΖΔ≤ΦΘ§ΉςΈΣ IEEE

802.3±ξΉΦΒΡ≤Ι≥δΓΘ

MAC ΚΆ PHY ÷°Φδ≤…”Ο MIIΘ®ΟΫΧεΕάΝΔΫ”ΩΎΘ©Ν§Ϋ”Θ§Υϋ « IEEE-802.3 Ε®“εΒΡ“‘ΧΪΆχ––“Β±ξΉΦΘ§Αϋά®

1 Ηω ΐΨίΫ”ΩΎ”κ MAC ΚΆ PHY ÷°ΦδΒΡ 1 ΗωΙήάμΫ”ΩΎΓΘ ΐΨίΫ”ΩΎΑϋά®Ζ÷±π”Ο”ΎΖΔΥΆΚΆΫ” ’ΒΡΝΫΧθΕάΝΔ–≈ΒάΘ§ΟΩΧθ–≈ΒάΕΦ”–Ή‘ΦΚΒΡ ΐΨίΓΔ ±÷”ΚΆΩΊ÷Τ–≈Κ≈Θ§

MII ΐΨίΫ”ΩΎΉήΙ≤–η“Σ 16 Ηω–≈Κ≈ΓΘ MII ΙήάμΫ”ΩΎΑϋΚ§ΝΫΗω–≈Κ≈Θ§“ΜΗω « ±÷”–≈Κ≈Θ§Νμ“ΜΗω « ΐΨί–≈Κ≈ΓΘΆ®ΙΐΙήάμΫ”ΩΎΘ§…œ≤ψΡήΦύ ”ΚΆΩΊ÷Τ

PHYΓΘ

“Μ Ηω “‘ ΧΪ Άχ Ϋ” ΩΎ ΒΡ ”≤ Φΰ Βγ ¬Ζ ‘≠ άμ »γœ¬ΆΦ Υυ ΨΘ§ ¥” CPU ΒΫ Ήν ÷’

Ϋ” ΩΎ “ά ¥Έ ΈΣ CPUΓΔMACΓΔ PHYΓΔ“‘ΧΪΆχΗτάκ±δ―ΙΤςΓΔ RJ45 ≤εΉυΓΘ“‘ΧΪΆχΗτάκ±δ―ΙΤς «“‘ΧΪΆχ ’ΖΔ–ΨΤ§”κΝ§Ϋ”Τς÷°ΦδΒΡ¥≈–‘ΉιΦΰΘ§‘ΎΤδΝΫ’Ώ÷°ΦδΤπΉ≈–≈Κ≈¥Ϊ δΓΔΉηΩΙΤΞ≈δΓΔ≤®–Έ–όΗ¥ΓΔ–≈Κ≈‘”≤®“÷÷ΤΚΆΗΏΒγ―ΙΗτάκΉς”Ο

–μΕύ¥ΠάμΤςΡΎ≤ΩΦ·≥…ΝΥ MAC ΜρΆ§ ±Φ·≥…ΝΥ MAC ΚΆ PHYΘ§Νμ”––μΕύ“‘ΧΪΆχΩΊ÷Τ–ΨΤ§“≤

Φ·≥…ΝΥ MAC ΚΆ PHYΓΘ

CPLDΚΆFPGA

‘≠άμΆΦΖ÷Έω

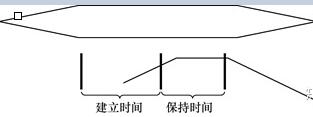

”≤Φΰ ±–ρΖ÷Έω

±–ρΖ÷ΈωΒΡΗ≈Ρν

«ΐΕ·ΙΛ≥Χ Π“ΜΑψ≤Μ–η“ΣΖ÷Έω”≤ΦΰΒΡ ±–ρΘ§ΒΪ «Φχ”Ύ–μΕύΤσ“ΒΡΎ«ΐΕ·ΙΛ≥Χ ΠΜΙ–η“Σ≥–ΒΘΒγ

¬ΖΑεΒς ‘ΒΡ»ΈΈώΘ§“ρ¥ΥΘ§’ΤΈ’ ±–ρΖ÷ΈωΒΡΖΫΖ®“≤ΨΆ±»Ϋœ±Ί“ΣΝΥΓΘ

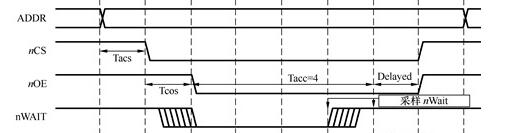

Ε‘«ΐΕ·ΙΛ≥Χ ΠΜρ”≤ΦΰΙΛ≥Χ ΠΕχ―‘Θ§ ±–ρΖ÷ΈωΒΡ“βΥΦ «»Ο–ΨΤ§÷°ΦδΒΡΖΟΈ ¬ζΉψ–ΨΤ§ ΐΨί ÷≤α÷– ±–ρΆΦ–≈Κ≈”––ßΒΡœ»ΚσΥ≥–ρΓΔ≤…―υΫ®ΝΔ ±ΦδΘ®

Setup TimeΘ©ΚΆ±Θ≥÷ ±ΦδΘ® Hold TimeΘ©ΒΡ“Σ«σΘ§‘ΎΒγ¬ΖΑεΙΛΉς≤Μ’ΐ≥ΘΒΡ ±ΚρΘ§ΉΦ»ΖΒΊΕ®ΈΜ ±–ρΖΫΟφΒΡΈ ΧβΓΘ

Ϋ®ΝΔ ±Φδ «÷Η‘Ύ¥ΞΖΔΤςΒΡ ±÷”–≈Κ≈±Ώ―ΊΒΫά¥“‘«ΑΘ§ ΐΨί“―Ψ≠±Θ≥÷Έ»Ε®≤Μ±δΒΡ ±ΦδΘ§»γΙϊ

Ϋ®ΝΔ ±Φδ≤ΜΙΜΘ§ ΐΨίΫΪ≤ΜΡή‘Ύ’βΗω ±÷”±Ώ―Ί±Μ¥ρ»κ¥ΞΖΔΤςΘΜ±Θ≥÷ ±Φδ «÷Η‘Ύ¥ΞΖΔΤςΒΡ ±÷”–≈

Κ≈±Ώ―ΊΒΫά¥“‘ΚσΘ§ ΐΨίΜΙ–ηΈ»Ε®≤Μ±δΒΡ ±ΦδΘ§»γΙϊ±Θ≥÷ ±Φδ≤ΜΙΜΘ§ ΐΨίΆ§―υ≤ΜΡή±Μ¥ρ»κ¥ΞΖΔ

ΤςΓΘ»γœ¬ΆΦΥυ ΨΘ§ ΐΨίΈ»Ε®¥Ϊ δ±Ί–κ¬ζΉψΫ®ΝΔ ±ΦδΚΆ±Θ≥÷ ±ΦδΒΡ“Σ«σΘ§Β±»ΜΘ§‘Ύ“Μ–©«ιΩωœ¬Θ§Ϋ®ΝΔ ±ΦδΚΆ±Θ≥÷ ±ΦδΒΡ÷ΒΩ…“‘ΈΣΝψΓΘ

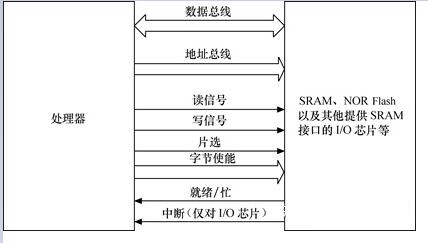

Βδ–ΆΒΡ”≤Φΰ ±–ρ

ΉνΒδ–ΆΒΡ”≤Φΰ ±–ρ « SRAM ΒΡΕΝ–¥ ±–ρΘ§‘ΎΕΝ / –¥Ιΐ≥Χ÷–…φΦΑΒΡ–≈Κ≈Αϋά®ΒΊ÷ΖΓΔ ΐΨίΓΔ

Τ§―ΓΓΔΕΝ / –¥ΓΔΉ÷ΫΎ ΙΡήΚΆΨΆ–ς / ΟΠΓΘΕ‘”Ύ“ΜΗω 16 ΈΜΓΔ 32 ΈΜΘ®…θ÷Ν 64 ΈΜΘ©ΒΡ SRAMΘ§Ή÷ΫΎ ΙΡή±μΟςΡΡ–©Ή÷ΫΎ±ΜΕΝ–¥ΓΘ

œ¬ΆΦΗχ≥ωΝΥ SRAM ΒΡΕΝ ±–ρΘ§–¥ ±–ρ”κ¥ΥœύΥΤΓΘ Ήœ»Θ§ΒΊ÷ΖΉήœΏ…œ δ≥ω“ΣΕΝΘ®–¥Θ©ΒΡΒΊ÷ΖΘ§»ΜΚσΖΔ≥ω SRAM

Τ§―Γ–≈Κ≈Θ§Ϋ”Ή≈ δ≥ωΕΝΘ®–¥Θ©–≈Κ≈Θ§÷°ΚσΕΝΘ®–¥Θ©–≈Κ≈“ΣΨ≠άζ ΐΗωΒ»¥ΐ÷ήΤΎΓΘΒ± SRAM ΕΝΘ®–¥Θ©ΥΌΕ»±»Ϋœ¬ΐ ±Θ§Β»¥ΐ÷ήΤΎΩ…“‘”…

MCU ΒΡœύ”ΠΦΡ¥φΤς…η÷ΟΘ§“≤Ω…“‘Ά®Ιΐ…η±ΗΨΆ–ς / ΟΠΘ®»γΆΦ 2.27 ÷–ΒΡ nWaitΘ©œρ CPU

±®ΗφΘ§’β―υΘ§ΕΝ–¥Ιΐ≥Χ÷–ΜαΉ‘Ε·ΧμΦ”Β»¥ΐ÷ήΤΎΓΘ

–ΨΤ§ ΐΨί ÷≤α‘ΡΕΝΖΫΖ®

–ΨΤ§ ΐΨί ÷≤αΆυΆυ≥Λ¥ο ΐΑΌ“≥Θ§…θ÷Ν…œ«ß“≥Θ§Εχ«“»Ϊ≤Ω «”ΔΈΡΘ§¥”ΆΖΒΫΈ≤≤ΜΦ”«χΖ÷ΒΊ‘Ρ

ΕΝ–η“ΣΜ®Ζ―Ζ«≥Θ≥ΛΒΡ ±ΦδΘ§Εχ«“≤Μ“ΜΕ®ΡήΜώ»ΓΕ‘…ηΦΤ…η±Η«ΐΕ·”–Αο÷ζΒΡ–≈œΔΓΘ–ΨΤ§ ΐΨί ÷≤α

ΒΡ’ΐ»Ζ‘ΡΕΝΖΫΖ® «ΩλΥΌΕχΉΦ»ΖΒΊΕ®ΈΜ”–”Ο–≈œΔΘ§÷ΊΒψ‘ΡΕΝ’β–©–≈œΔΘ§Κω¬‘ΈόΙΊΡΎ»ίΓΘœ¬Οφ“‘

S3C6410A ΒΡ ΐΨί ÷≤αΈΣάΐά¥Ζ÷Έω‘ΡΕΝΖΫΖ®Θ§ΈΣΝΥ÷±ΙέΒΊΖ¥”≥‘ΡΕΝΙΐ≥ΧΘ§±ΨΫΎΒΡΆΦΕΦ «÷±Ϋ”

¥” ΐΨί ÷≤α÷–ΉΞΤΝΕχΒΟΒΫΒΡΓΘ¥ρΩΣ S3C6410 A ΒΡ ΐΨί ÷≤αΘ§ΖΔœ÷“≥ ΐΈΣ 1378 “≥Θ§¥”ΆΖΕΝΒΫΈ≤ «≤Μœ÷ ΒΒΡΓΘS3C6410A

ΐΨί ÷≤αΒΡΒΎ 1 ’¬ΓΑ PRODUCT OVERVIEWΓ±Θ®≤ζΤΖΉέ ωΘ© «±ΊΕΝΒΡΘ§Ά®Ιΐ‘ΡΕΝ’β“Μ≤ΩΖ÷Ω…“‘Μώ÷Σ’ϊΗω–ΨΤ§ΒΡΉι≥…ΓΘ’β“Μ’¬ΆυΆυΜαΗχ≥ω“ΜΗω–ΨΤ§ΒΡ’ϊΧεΫαΙΙΆΦΘ§≤ΔΕ‘–ΨΤ§ΡΎΒΡ÷ς“ΣΡΘΩιΫχ––“ΜΗωΦρΫύΒΡΟη ωΓΘ

S3C6410A ΒΡ’ϊΧεΫαΙΙΆΦ»γΆΦ 2.27 Υυ ΨΘ®Φϊ ΐΨί ÷≤αΒΎ 61 “≥Θ©ΓΘ

ΒΎ 2 ΓΪ 43 ’¬ ÷– ΒΡ ΟΩ “Μ ’¬ ΕΦ Ε‘ ”Π S3C6410A ’ϊ Χε Ϋα ΙΙ ΆΦ ÷– ΒΡ

“Μ Ηω ΡΘ ΩιΘ§ ΆΦ 2.28 ΈΣ ¥”Adobe Acrobat ÷–÷±Ϋ”ΉΞ»ΓΒΡ S3C6410A ΐΨί ÷≤αΒΡΡΩ¬ΦΫαΙΙΆΦΓΘ

ΒΎ 2 ’¬ΓΑ MemoryMapΓ±Θ®ΡΎ¥φ”≥…δΘ©±»ΫœΙΊΦϋΘ§Ε‘”ΎΕ®ΈΜ¥φ¥ΔΤςΚΆΆβ…ηΥυΕ‘”ΠΒΡΜυ÷Ζ”–÷±Ϋ”÷ΗΒΦ“β“εΘ§’β“Μ≤ΩΖ÷”ΠΗΟœΗΩ¥ΓΘ

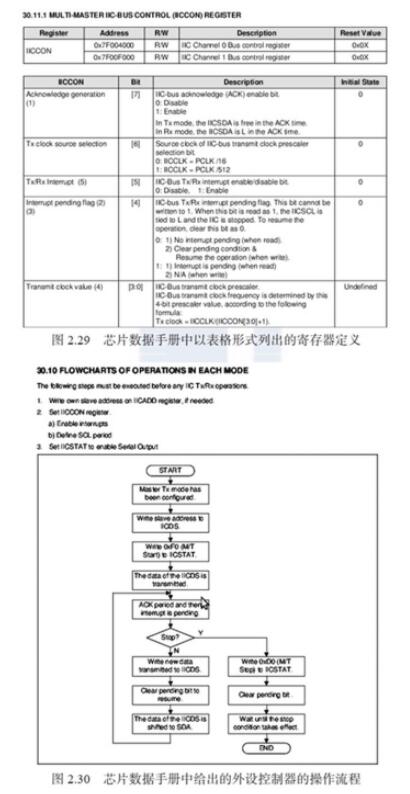

ΒΎ 3 ΓΪ 34 ’¬Ε‘”Π”Ύ CPU ΡΎ≤ΩΦ·≥…ΒΡΆβ…ηΜρΉήœΏΩΊ÷ΤΤςΘ§Β±ΨΏΧε±ύ–¥Ρ≥Ϋ”ΩΎΒΡ«ΐΕ· ±Θ§”ΠΗΟœξœΗ‘ΡΕΝΘ§÷ς“Σ «Ζ÷Έω ΐΨίΓΔΩΊ÷ΤΓΔΒΊ÷ΖΦΡ¥φΤςΘ® ΐΨί ÷≤α÷–“ΜΑψΜα“‘±μΗώΝ–≥ωΘ©ΒΡΖΟΈ ΩΊ÷ΤΚΆΨΏΧε…η±ΗΒΡ≤ΌΉςΝς≥ΧΘ® ΐΨί ÷≤α÷–ΜαΗχ≥ω≤Ϋ÷ηΘ§”–ΒΡΜΙΜαΗχ≥ωΝς≥ΧΆΦΘ©ΓΘΤ©»γΈΣΝΥ±ύ–¥

S3C6410A ΒΡ I2C ΩΊ÷ΤΤς«ΐΕ·Θ§Έ“Ο«–η“ΣœξœΗ‘ΡΕΝάύΥΤΆΦ 2.29 ΒΡΦΡ¥φΤςΕ®“ε±μΗώΚΆΆΦ 2.30ΒΡ≤ΌΉςΝς≥ΧΆΦΓΘ

ΒΎ 44 ’¬ΓΑ ELECTRICAL DATA Γ±Θ®Ε‘”ΎΒγΤχ ΐΨίΘ§‘ΎΆΦ 2.28 ÷–Έ¥Μ≠≥ωΘ©Θ§Οη ω–ΨΤ§ΒΡΒγ

ΤχΧΊ–‘Θ§»γΒγ―ΙΓΔΒγΝςΚΆΗς÷÷ΙΛΉςΡΘ Ϋœ¬ΒΡ ±–ρΓΔΫ®ΝΔ ±ΦδΚΆ±Θ≥÷ ±ΦδΒΡ“Σ«σΓΘΥυ”–ΒΡ ΐ

Ψί ÷≤αΕΦΜαΑϋΚ§άύΥΤ’¬ΫΎΘ§’β“Μ’¬Ε‘”Ύ”≤ΦΰΙΛ≥Χ Π±»ΫœΙΊΦϋΘ§ΒΪ «Θ§“ΜΑψά¥ΥΒΘ§«ΐΕ·ΙΛ≥Χ Π≤Δ≤Μ–η“Σ‘ΡΕΝΓΘ

ΒΎ 45 ’¬ΓΑ MECHANICAL DATAΓ±Θ®Μζ–Β ΐΨίΘ©Οη ω–ΨΤ§ΒΡΈοάμΧΊ–‘ΓΔ≥Ώ¥γΚΆΖβΉΑΘ§”≤Φΰ

ΙΛ≥Χ ΠΜα“άΨί’β“Μ’¬Μφ÷Τ–ΨΤ§ΒΡΖβΉΑΘ® FootprintΘ©Θ§ΒΪ «Θ§«ΐΕ·ΙΛ≥Χ ΠΈό–κ‘ΡΕΝΓΘ

“«Τς“«±μ Ι”Ο

Άρ”Ο±μ

‘ΎΒγ¬ΖΑεΒς ‘Ιΐ≥Χ÷–÷ς“Σ Ι”ΟΆρ”Ο±μΒΡΝΫΗωΙΠΡήΓΘ

≤βΝΩΒγΤΫΓΘ

Ι”ΟΕΰΦΪΙήΒ≤≤βΝΩΒγ¬ΖΑε…œΆχ¬γΒΡΝ§Ά®–‘Θ§Β± Ψ≤®Τς±Μ…η÷Ο‘ΎΕΰΦΪΙήΒ≤Θ§≤βΝΩΝ§Ά®ΒΡ

Άχ¬γΜαΖΔ≥ωΓΑύ÷ύ÷Γ±ΒΡΟυΫ–Θ§Ζώ‘ρΘ§ΟΜ”–Ν§Ά®ΓΘ

Ψ≤®Τς

Ψ≤®Τς «άϊ”ΟΒγΉ” Ψ≤®ΙήΒΡΧΊ–‘Θ§ΫΪ»Υ―έΈόΖ®÷±Ϋ”Ιέ≤βΒΡΫΜ±δΒγ–≈Κ≈ΉΣΜΜ≥…ΆΦœώΘ§œ‘ Ψ

‘Ύ”ΪΙβΤΝ…œ“‘±ψ≤βΝΩΒΡΒγΉ”“«ΤςΓΘΥϋ «Ιέ≤λ ΐΉ÷Βγ¬Ζ Β―ιœ÷œσΓΔΖ÷Έω Β―ι÷–ΒΡΈ ΧβΓΔ≤βΝΩ Β

―ιΫαΙϊ±Ί≤ΜΩ……ΌΒΡ÷Ί“Σ“«ΤςΓΘ

Ι”Ο Ψ≤®Τς ±”Π÷ς“ΣΉΔ“βΒςΫΎ¥Ι÷±ΤΪΉΣ“ρ ΐ―Γ‘ώΘ® VOLTS/DIVΘ©ΚΆΈΔΒςΓΔ ±Μυ―Γ‘ώ

Θ® TIME/DIVΘ©ΚΆΈΔΒς“‘ΦΑ¥ΞΖΔΖΫ ΫΓΘ

»γΙϊ VOLTS/DIV …η÷Ο≤ΜΚœάμΘ§‘ρΩ…Ρή‘λ≥…Βγ―ΙΖυΕ»≥§≥ω’ϊΗωΤΝΡΜΜρ‘ΎΤΝΡΜ…œ±δΕ·ΧΪΙΐΈΔ–Γ“‘÷¬ΈόΖ®Ιέ≤βΒΡœ÷œσΓΘΆΦ

2.31 Υυ ΨΈΣΆ§“ΜΗω≤®–Έ‘Ύ VOLTS/DIV …η÷Ο”…¥σΒΫ–Γ±δΜ·Ιΐ≥Χ÷–ΒΡ Ψ“βΆΦΓΘ

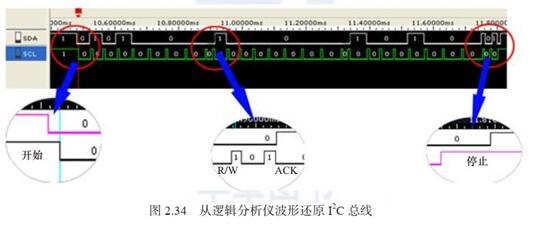

¬ΏΦ≠Ζ÷Έω“«

¬ΏΦ≠Ζ÷Έω“« «άϊ”Ο ±÷”¥”≤β ‘…η±Η…œ≤…Φ· ΐΉ÷–≈Κ≈≤ΔΫχ––œ‘ ΨΒΡ“«ΤςΘ§ΤδΉν÷ς“ΣΒΡΉς”Ο «”Ο”Ύ ±–ρΒΡ≈–Ε®ΓΘ”κ Ψ≤®Τς≤ΜΆ§Θ§¬ΏΦ≠Ζ÷Έω“«≤Δ≤ΜΨΏ±Η–μΕύΒγ―ΙΒ»ΦΕΘ§Ά®≥Θ÷Μœ‘ ΨΝΫΗωΒγ―ΙΘ®¬ΏΦ≠

1 ΚΆ 0Θ©ΓΘ‘Ύ…ηΕ®ΝΥ≤ΈΩΦΒγ―Ι÷°ΚσΘ§¬ΏΦ≠Ζ÷Έω“«Ά®Ιΐ±»ΫœΤςά¥≈–Ε®¥ΐ≤β ‘–≈Κ≈Θ§ΗΏ”Ύ≤ΈΩΦΒγ―Ι’ΏΈΣ 1Θ§ΒΆ”Ύ≤ΈΩΦΒγ―Ι’ΏΈΣ

0ΓΘ

άΐ»γΘ§»γΙϊ“‘ n MHz ≤…―υ¬ ≤βΝΩ“ΜΗω–≈Κ≈Θ§¬ΏΦ≠Ζ÷Έω“«Μα“‘ 1000/n ns ΈΣ÷ήΤΎ≤…―υ–≈Κ≈Θ§Β±≤ΈΩΦΒγ―Ι…ηΕ®ΈΣ

1.5V ±Θ§≥§Ιΐ 1.5V ‘ρ≈–Ε®ΈΣ 1Θ§ΒΆ”Ύ 1.5V ‘ρΈΣ 0Θ§ΫΪ¬ΏΦ≠ 1 ΚΆ 0 Ν§Ϋ”≥…Ν§–χΒΡ≤®–ΈΘ§ΙΛ≥Χ Π“άΨί¥ΥΝ§–χ≤®–ΈΩ…―Α’“ ±–ρΈ ΧβΓΘ

ΗΏΕΥ¬ΏΦ≠Ζ÷Έω“«ΜαΑ≤ΉΑ Windows ≤ΌΉςœΒΆ≥≤ΔΧαΙ©Ζ«≥Θ”―…ΤΒΡ¬ΏΦ≠Ζ÷Έω”Π”Ο»μΦΰΘ§‘ΎΤδ÷–

Ω…ΖΫ±ψΒΊ±ύΦ≠ΧΫ’κΓΔ–≈Κ≈≤Δ≤ιΩ¥≤®–ΈΓΘ’β÷÷¬ΏΦ≠Ζ÷Έω“«“ΜΑψ≥ΤΈΣ¥ΪΆ≥¬ΏΦ≠Ζ÷Έω“«Θ§ΤδΙΠΡή«Ω¥σΘ§ ΐΨί≤…Φ·ΓΔΖ÷ΈωΚΆ≤®–Έœ‘ Ψ»Ύ”Ύ“Μ…μΘ§ΒΪ «ΦέΗώ °Ζ÷ΑΚΙσΓΘ”–ΒΡ¬ΏΦ≠Ζ÷Έω“«‘ρΟΜ”–ΆΦ–ΈΫγΟφΘ§ΒΪ «Ω…“‘Ά®Ιΐ

USB Β»Ϋ”ΩΎ”κ PC Ν§Ϋ”Θ§Ζ÷Έω»μΦΰ‘ρΙΛΉς‘Ύ PC …œΓΘ’β÷÷¬ΏΦ≠Ζ÷Έω“«“ΜΑψ≥ΤΈΣ–ιΡβ¬ΏΦ≠Ζ÷Έω“«Θ§Υϋ «

PC ΦΦ θΚΆ≤βΝΩΦΦ θΫαΚœΒΡ≤ζΈοΘ§¥ΞΖΔΚΆΦ«¬ΦΙΠΡή”…–ιΡβ¬ΏΦ≠Ζ÷Έω“«”≤ΦΰΆξ≥…Θ§≤®–Έœ‘ ΨΓΔ δ»κ…η÷ΟΒ»ΙΠΡή”…

PC Άξ≥…Θ§“ρ¥Υ±»ΫœΝ°ΦέΓΘΆΦ 2.33 Ηχ≥ωΝΥΝΫ÷÷¬ΏΦ≠Ζ÷Έω“«ΓΘ

¬ΏΦ≠Ζ÷Έω“«ΒΡ≤®–ΈΩ…“‘œ‘ ΨΒΊ÷ΖΓΔ ΐΨίΓΔΩΊ÷Τ–≈Κ≈ΦΑ»Έ“βΆβ≤ΩΧΫΆΖ–≈Κ≈ΒΡ±δΜ·ΙλΦΘΘ§‘Ύ

Ι”Ο÷°«Α”Πœ»±ύΦ≠ΟΩΗωΧΫΆΖΒΡ–≈Κ≈ΟϊΓΘ÷°ΚσΘ§ΗυΨί≤®–ΈΜΙ‘≠≥ωΉήœΏΒΡΙΛΉς ±–ρΘ§ΆΦ 2.34 Ηχ≥ωΝΥ“ΜΗω I2C

ΒΡάΐΉ”ΓΘΡΩ«ΑΘ§ΚήΕύ¬ΏΦ≠Ζ÷Έω“«ΕΦΉ‘¥χΝΥ–≠“ιΖ÷ΈωΡήΝΠΘ§Ω…“‘Ή‘Ε·Ζ÷Έω≥ωΉήœΏ…œ¥Ϊ δΒΡΟϋΝνΓΔΒΊ÷ΖΚΆ ΐΨίΒ»–≈œΔΓΘ

ΉήΫα

ΦρΒΞΒΊΫ≤ΫβΝΥ«ΐΕ·»μΦΰΙΛ≥Χ Π±Ί±ΗΒΡ”≤ΦΰΜυ¥Γ÷Σ ΕΘ§Οη ωΝΥ¥ΠάμΤςΓΔ¥φ¥ΔΤςΒΡΖ÷άύ“‘ΦΑΗς÷÷¥ΠάμΤςΓΔ¥φ¥ΔΤςΒΡ‘≠άμ”κ”ΟΆΨΘ§≤ΔΖ÷ΈωΝΥ≥ΘΦϊΒΡΆβΈß…η±ΗΫ”ΩΎ”κΉήœΏΒΡΙΛΉςΖΫ ΫΓΘ

¥ΥΆβΘ§±Ψ’¬ΜΙΫ≤ ωΝΥΕ‘«ΐΕ·ΙΛ≥Χ ΠΫχ–– ΒΦ œνΡΩΩΣΖΔ”–Αο÷ζΒΡ‘≠άμΆΦΓΔ”≤Φΰ ±–ρΖ÷ΈωΖΫΖ®Θ§–ΨΤ§ ΐΨί ÷≤α‘ΡΕΝΖΫΖ®“‘ΦΑΆρ”Ο±μΓΔ Ψ≤®ΤςΚΆ¬ΏΦ≠Ζ÷Έω“«ΒΡ Ι”ΟΖΫΖ®ΓΘ

|