| ±ύΦ≠ΆΤΦω: |

±ΨΈΡ÷ς“ΣΫι…ήΝΥM3ΡΎΚΥ÷–ΒΡΦΡ¥φΤς≤ΌΉςΡΘ ΫΚΆΧΊ»®Β»ΦΕ¥φ¥ΔΤς”≥…δ“‘ΦΑM3ΒΡœΒΆ≥“λ≥ΘΚΆΆβ≤Ω÷–ΕœΘ§œΘΆϊΕ‘ΡζΒΡ―ßœΑ”–ΥυΑο÷ζΓΘ

±ΨΈΡά¥Ή‘”Ύ≤©ΩΆ‘ΑΘ§”…ΜπΝζΙϊ»μΦΰAlice±ύΦ≠ΓΔΆΤΦωΓΘ |

|

1.stm32Ήέ ω

2.ΦΡ¥φΤςΉι

3.≤ΌΉςΡΘ ΫΚΆΧΊ»®ΦΕ±π

4.¥φ¥ΔΤς”≥…δ

5.÷–ΕœΚΆ“λ≥Θ

6.ΤδΥϊ

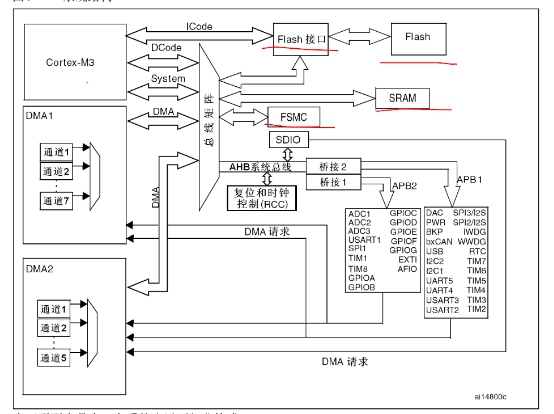

Stm32Ήέ ω

’βΩ…“‘ΥΒ «Έ“ΒΎ“ΜΩν»œ’φ―ßœΑΒΡΒΞΤ§ΜζΝΥΘ§―ßΆξ’βΗωΨΆ“ΣΩΣΤτΈ“Ά®Άυarm9ΒΡ¥σΟ≈ΝΥΘ§Ϋ”œ¬ά¥Α―Έ“―ßΒΫΒΡΕΪΈςΉω“ΜΗωœΒΆ≥ΒΡΗ≈ ωΘΚ

…œΆΦ «stm32ΒΡœΒΆ≥ΫαΙΙΓΘ

Ι”ΟΙΰΗΞΧεœΒΫαΙΙΘ§»Γ÷ΗΚΆ»Γ ΐΨίΖ÷άκΘ§

ICODE÷ΗΝνΉήœΏΝ§Ϋ”ΒΫflash…Ν¥φ÷ΗΝν¥φ¥Δ«χΘ§’βΗω¥φ¥Δ«χΒΡΒΊ÷Ζ‘Ύ0x00000000-0x1FFFFFFF÷°ΦδΘ§ΗΚ‘π»Γ÷Η≤ΌΉςΓΘ

DCODE ΐΨίΉήœΏΗΚ‘π‘Ύ0x00000000-0x1FFFFFFF÷°ΦδΒΡ ΐΨίΖΟΈ ≤ΌΉςΓΘ’βΗω ΐΨί¥φ¥Δ«χΩ…“‘ «SPRAM“≤Ω…“‘ «…Ν¥φΚΆΆβ…ηΓΘ

œΒΆ≥ΉήœΏΘΚΗΚ‘π‘Ύ0x20000000-0xDFFFFFFFΚΆ0xE0100000-0xFFFFFFFF÷°ΦδΥυ”–ΒΡ ΐΨί¥ΪΥΆΓΘ

ΉΔΘΚΩ¥ΒΫ’βΡψΩ…ΡήΜαΟ‘ΜσΘ§M3ΡΎΚΥ≤Μ «÷Μ”–÷ΗΝνΉήœΏΚΆ ΐΨίΉήœΏ¬πΘΩΕ‘ΒΡΘ§ΒΪ «÷ΗΝνΉήœΏΚΆICODE÷ΗΝνΉήœΏ≤Μ «“ΜΗωΘ§―ûÓ̒≈M3ΡΎΚΥ―υάΐ¥ΠάμΤςΒΡΆΦΨΆΟςΑΉΝΥΘΚ

Ηω»ΥάμΫβΘ§D-codeΉήœΏΚΆœΒΆ≥ΉήœΏΕΦ «ά¥‘¥”ΎM3ΡΎΚΥ“ΐ≥ωΒΡ ΐΨίΉήœΏΓΘ

DMAΆ®ΙΐΉήœΏΨΊ’σ÷±Ϋ”ΚΆΡΎ¥φœύΝ§ΓΘ

ΉήœΏΨΊ’σ–≠ΒςΡΎΚΥΚΆDMAΕ‘SPRAMΘ§…Ν¥φΘ§Άβ…ηΒΡΖΟΈ ΓΘ

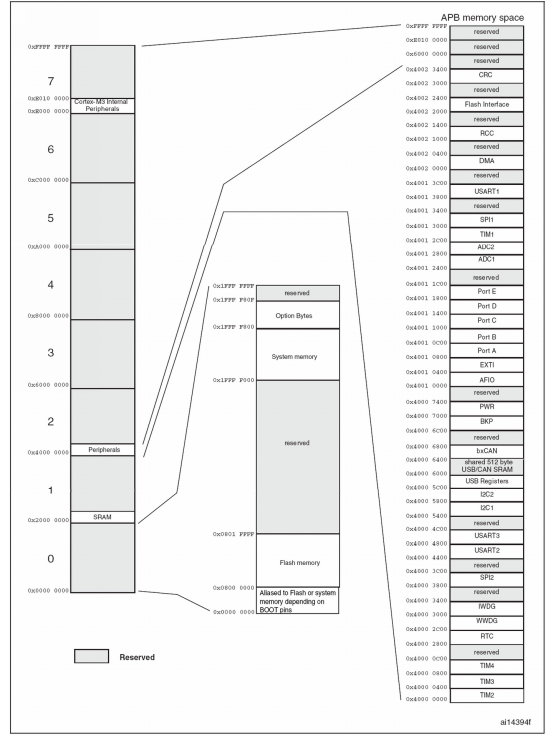

AHPΉήœΏ«≈Ϋ”ΝΫΗωAPBΉήœΏΘ§ΝΫΗωAPBΉήœ‘ΒΟΉνΗΏΥΌΕ»≤ΜΆ§Θ§APB1ΉνΗΏΥΌΕ»œό”Ύ36MHzΘ§APB2œό”Ύ72MHzΓΘΝΫΗωAPBΉήœΏ…œΙ“Ϋ”Ή≈≤ΜΆ§ΥΌ¬ ΒΡ…η±ΗΓΘ

Stm32f10œΒΝ–ΒΡΨ≤Χ§SPRAMΈΣ64KΘ§Τπ ΦΒΊ÷ΖΈΣ0x20000000.

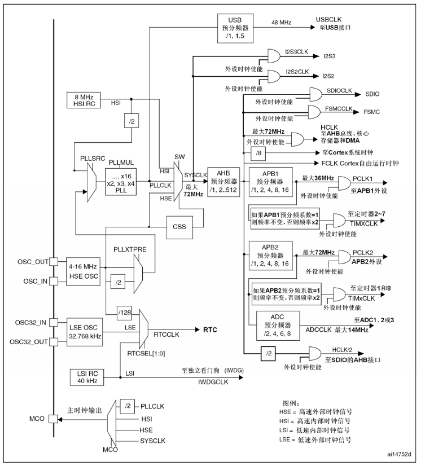

Stm32ΒΡΤτΕ·ΖΫ Ϋ”–“‘œ¬ΦΗ÷÷ΘΚ

œ¬ΟφΒΡ «stm32ΒΡ ±÷” ςΘ§stm32”–ΥΡΗω≤ΜΆ§ΒΡ ±÷”‘¥ΘΚ

1.HSE ±÷”ΘΚΗΏΥΌΆβ≤Ω ±÷”–≈Κ≈Θ§ά¥Ή‘”ΎΆβ≤ΩΨß’ώΘΚΩ…ΉςΈΣœΒΆ≥ ±÷”‘¥Θ§“≤Ω…±ΜPLL±ΕΤΒ÷°ΚσΙ§œΒΆ≥ ±÷” Ι”ΟΓΘ

2.HSI ±÷”ΘΚΗΏΥΌΡΎ≤Ω ±÷”–≈Κ≈Θ§ά¥Ή‘”ΎΡΎ≤ΩRC’ώΒ¥ΤςΘΚΩ…÷±Ϋ”ΉςΈΣœΒΆ≥ ±÷”Θ§Μρ’ΏΕΰΖ÷ΤΒ÷°ΚσΉςΈΣPLL δ»κΘ§±ΕΤΒ÷°ΚσΙ©œΒΆ≥ Ι”ΟΓΘ

3.LSE ±÷”ΘΚΒΆΥΌΆβ≤Ω ±÷”Θ§ά¥Ή‘”ΎΆβ≤ΩΨß’ώΘΚΈΣΕ® ± ±÷”Μρ’ΏΤδΥϊΕ® ±ΙΠΡήΧαΙ©

4.LSI ±÷”ΘΚΒΆΥΌΡΎ≤Ω ±÷”Θ§ά¥Ή‘”ΎΡΎ≤ΩRC’ώΒ¥ΤςΘΚ‘ΎΆΘΜζΜρ’Ώ¥ΐΜζΒΡΡΘ Ϋœ¬Θ§ΈΣΕάΝΔΩ¥Ο≈ΙΖΜρ’ΏΉ‘Ε·ΜΫ–―ΒΞ‘ΣΧαΙ© ±÷”ΓΘ

Ψ≠Ιΐ“Μ–©Ν–±ΕΤΒΘ§Ζ÷ΤΒΒΟΒΫΝΥΦΗΗωΚΆΩΣΖΔ”–ΙΊΒΡ ±÷”ΘΚ

1.SYSCLKΘΚœΒΆ≥ ±÷”¥σ≤ΩΖ÷ ±÷”ΒΡά¥‘¥

2.HCLKΘΚ”…AHB‘ΛΖ÷ΤΒΤς δ≥ωΒΟΒΫΘ§ΗΏΥΌΉήœΏAHBΒΡ ±÷”–≈Κ≈

3.FCLKΘΚ”…AHB‘ΛΖ÷ΤΒΤς δ≥ωΒΟΒΫΘ§Ή‘”…‘Υ–– ±÷”ΓΘ

4.PCLK1ΘΚΆβ…η ±÷”Θ§”…APB1‘ΛΖ÷ΤΒΤςΒΟΒΫΘ§Ήν¥σ36MHz

5.PCLK2ΘΚΆβ…η ±÷”Θ§”…APB2‘ΛΖ÷ΤΒΤςΒΟΒΫΘ§Ήν¥σ72MHz

±÷” ς»γœ¬ΘΚ

Stm32ΒΡGPIOΒΡ8÷÷ΡΘ ΫΘΚ

Θ®1Θ©GPIO_Mode_AIN ΡΘΡβ δ»κ

Θ®2Θ©GPIO_Mode_IN_FLOATING ΗΓΩ’ δ»κ

Θ®3Θ©GPIO_Mode_IPD œ¬ά≠ δ»κ

Θ®4Θ©GPIO_Mode_IPU …œά≠ δ»κ

Θ®5Θ©GPIO_Mode_Out_OD ΩΣ¬© δ≥ω

Θ®6Θ©GPIO_Mode_Out_PP ΆΤΆλ δ≥ω

Θ®7Θ©GPIO_Mode_AF_OD Η¥”ΟΩΣ¬© δ≥ω

Θ®8Θ©GPIO_Mode_AF_PP Η¥”ΟΆΤΆλ δ≥ω

4÷÷ δ»κΘΚΡΘΡβ δ»κΚΆΟςœ‘Ϋ” ήΡΘΡβ–≈Κ≈Θ§±»»γ”Ο”ΎADCΘ§…œά≠ δ»κΚΆœ¬ά≠ δ»κΨΆ «Ρ§»œ ±ΗΏΒγΤΫΚΆΒΆΒγΤΫΓΘΗΓΩ’ δ»κ‘Ύ–ΨΤ§ΡΎ≤ΩΦ»ΟΜ”–Ϋ”…œά≠ΒγΉη“≤ΟΜ”–Ϋ”œ¬ά≠ΒγΉηΘ§“ΐΫ≈Βγ―Ι «Ηω≤Μ»ΖΕ®÷ΒΘ§ δ»κΉηΩΙΫœ¥σΘ§≥Θ”Ο”οI2cΘ§USARTΓΘ

4÷÷ δ≥ωΘΚΖ÷Η¥”ΟΚΆΖ«Η¥”ΟΘ§Η¥”ΟΈΣΖ÷≈δΗχΤ§…œΆβ…ηΘ§Ζ«Η¥”ΟΈΣ”ΟΉς’ΐ≥ΘΒΡIOΩΎΓΘΆΤΟβ δ≥ωΈΣ’ΐ≥ΘΒΡ δ≥ωΘ§Εχ‘ΎΩΣ¬© δ≥ωΡΘ ΫΘ§IOΩΎΩ…“‘”…Άβ≤ΩΒγ¬ΖΗΡ±δΈΣΒΆΒγΤΫΜρ≤Μ±δΓΘΥυ“‘ΩΣ¬©ΡΘ ΫΩ…“‘ΕΝIO δ»κΒγΤΫ±δΜ·Θ§ Βœ÷C51ΒΡIOΥΪœρΙΠΡήΓΘ

Β±ΡξΩ¥≤ΜΕ°ΒΡΕΪΈςΘ§œ÷‘Ύ‘ΫΖΔ«εΈζΓΘ

ΦΡ¥φΤςΉι

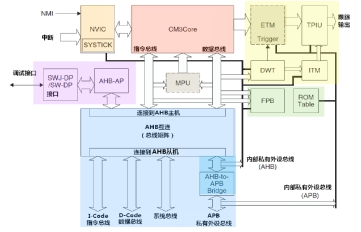

’β“Μ≤ΩΖ÷ΨΆ τ”ΎM3ΡΎΚΥ÷–ΒΡ÷Σ ΕΝΥΓΘ

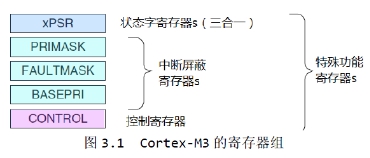

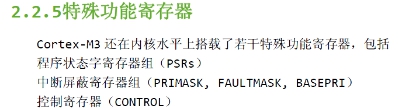

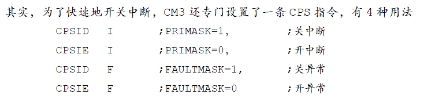

M3ΡΎΚΥ÷–ΒΡΦΡ¥φΤς÷ς“Σ»γœ¬ΘΚ

œ¬ΟφΑΛΗωΫβ Ά

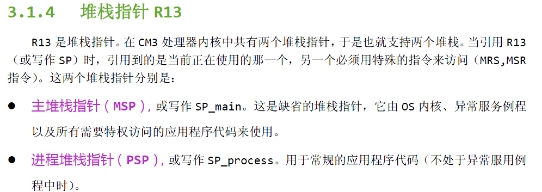

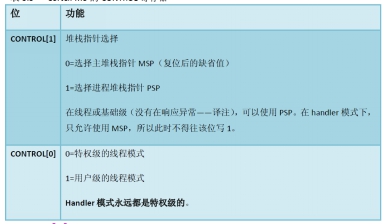

M3 Ι”ΟΒΡ «ΥΪΕ―’ΜΘ§Η¥ΈΜ÷°ΚσΡ§»œ Ι”ΟMSPΘ§Ρ§»œ «ΧΊ»®ΦΕΘ§»γΙϊœκ“Σ«–ΜΜ–η“Σ ÷Ε·–όΗΡΓΘΕχ…œΟφΒΡMSPΚΆPSPΒΡ”ΟΆΨ÷Μ «“Μ÷÷ΆΤΦω”ΟΆΨΘ§≤Δ≤Μ «“ΜΕ®“ΣΡ«Ο¥”ΟΘ§±»»γΥΒΗ¥ΈΜ÷°ΚσΡψΩ…“‘≤Μ–όΗΡΘ§Ρ«Ο¥ΡψΒΡ≥ΘΙφ¥ζ¬κΨΆ“Μ÷± «ΧΊ»®ΦΕΘ§ Ι”ΟMSPΘ®Έ“ΨΆ «’β―υΒΈΓΘΓΘΖΫ±ψ÷Ν…œΘ©ΓΘ

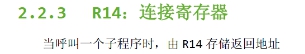

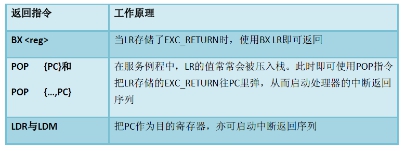

’βΗωΦΡ¥φΤς”÷Ϋ–LRΦΡ¥φΤςȧѫϥ±ʷ ΐ «“ΜΦΕΒς”ΟΒΡ ±ΚρΘ§ΨΆΩ…“‘ΫΪΖΒΜΊΒΊ÷Ζ÷±Ϋ”¥φΒΫLR÷–Θ§ Γ»ΞΝΥΖΟΈ ΡΎ¥φΘ§ΧαΗΏΝΥ–ß¬ Θ§Β±Κ· ΐΒς”ΟΗΏ”Ύ“ΜΦΕΘ§‘ρ–ηΫΪ«ΑΟφΒΡLR÷–ΒΡ÷Β―Ι’ΜΘ§“‘±ψ¥φ¥Δ–¬ΒΡ÷ΒΓΘ

Β±Ϋχ»κ“λ≥ΘΒΡ ±ΚρΘ§LRΦΡ¥φΤςΒΡ÷ΒΗϋ–¬ΈΣΧΊ βΒΡEXE_RETURNΘΚ

ΨΆ «PC¬οΓΘΓΘΓΘΓΘ

ΧΊ βΙΠΡήΦΡ¥φΤς“ΜΕ®“Σ‘ΎΧΊ»®ΦΕ≤≈Ρή±ΜΖΟΈ Θ® Ι”ΟMSRΚΆMRS÷ΗΝνΘ©Θ§÷Ν”Ύ «Thread ΡΘ ΫΜΙ «handlerΡΘ ΫΈόΥυΈΫΓΘ

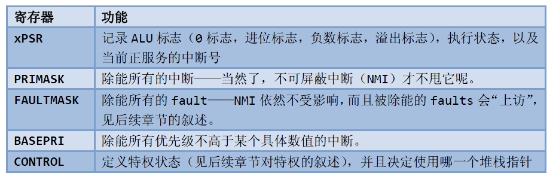

œξœΗΙΠΡή»γœ¬ΘΚ

xPSR τ”Ύ»ΐΚœ“ΜΦΡ¥φΤςΘ§Ω…“‘Ζ÷≥ω»ΐΗωΉ”Ή¥Χ§ΦΡ¥φΤς

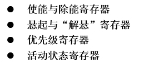

Ά®ΙΐMRSΚΆMSR’β»ΐΗωΦΡ¥φΤςΩ…“‘ΒΞΕάΖΟΈ Θ§“≤Ω…“‘ΝΫΝΫΉιΚœΖΟΈ Θ§“≤Ω…“‘»ΐΚœ“ΜΖΟΈ Θ§’βΗωΦΡ¥φΤς¥σ÷¬»γœ¬Θ®Ω¥œ¬ΨΆΚΟΘ©ΘΚ

Τδ Β≥ΐΝΥ–όΗΡ…œΟφΒΡΦΡ¥φΤςΩ…“‘ΩΣΙΊ÷–ΕœΘ§M3ΜΙ”–Ή®Ο≈ΒΡΩΣΙΊ÷–Εœ÷ΗΝνΘΚ

CONTROLΦΡ¥φΤςΙΠΡή»γœ¬ΘΚ

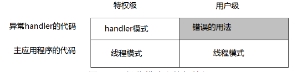

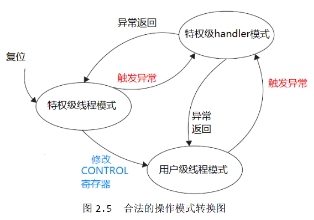

≤ΌΉςΡΘ ΫΚΆΧΊ»®Β»ΦΕ

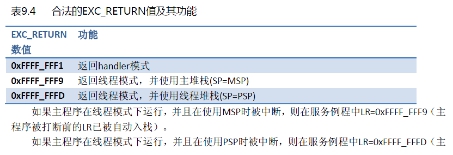

≤ΌΉςΡΘ ΫΖ÷ΈΣThreadΡΘ ΫΚΆHandlerΡΘ ΫΘ§ΧΊ»®Β»ΦΕΖ÷ΈΣΧΊ»®ΦΕΚΆ”ΟΜßΦΕΓΘ”ΟΜßΒΡ≥Χ–ρ¥ζ¬κ“ΜΕ® «ThreadΡΘ ΫΘ§Εχ“λ≥Θ“ΜΕ® «handlerΡΘ ΫΘ§”ΟΜß≥Χ–ρ¥ζ¬κ≥Χ–ρ¥ζ¬κΩ…“‘ «ΧΊ»®ΦΕΚΆ”ΟΜßΦΕΘ§ΒΪ «“λ≥Θ÷ΜΡή «ΧΊ»®ΦΕΓΘ

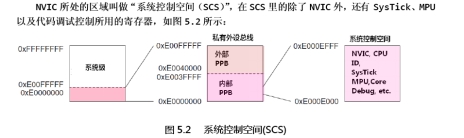

ThreadΡΘ Ϋ+”ΟΜßΦΕΘ§ΨΆ≤ΜΡήΖΟΈ œΒΆ≥ΩΊ÷ΤΩ’ΦδΘ®SCSΘ©ΚΆΧΊ βΦΡ¥φΤς(≥ΐΝΥAPSR)ΓΘ

ΧΊ»®ΦΕ«–ΜΜΒΫ”ΟΜßΦΕΚή»ί“ΉΘ§–όΗΡœ¬controlΦΡ¥φΤςΨΆΚΟΘ§”ΟΜßΦΕ«–ΜΜΒΫΧΊ»®ΦΕΒΡΖΫ Ϋ÷Μ”–¥ΞΖΔ“ΜΗω“λ≥ΘΘ§«–ΜΜΒΫhandlerΡΘ ΫΘ§’βΗω ±Κρ «ΧΊ»®ΦΕΘ§»ΜΚσ–όΗΡcontrolΦΡ¥φΤςΒΡΝψΈΜΘ§‘ΌΖΒΜΊΨΆ «ΧΊ»®ΦΕΓΘ

œ¬ΆΦ «“ΜΗωΗς÷÷«–ΜΜΒΡ Ψ“βΆΦΘΚ

’β÷÷…ηΕ®ΒΡ¥σ÷¬”Ο“βΨΆ «Έ“Ο«–¥Τ’Ά®¥ζ¬κΒΡ ±Κρ…η÷ΟΈΣ”ΟΜßΦΕΘ§’β―υΒΡΜΑΩ…“‘Ζά÷ΙΕ‘SCSΚΆΧΊ βΦΡ¥φΤς’β÷÷ΟτΗ–ΒΊ¥χΒΡΈσ≤ΌΉςΘ§œκ“ΣΖΟΈ ’β–©ΒΡΜΑΨΆ÷ΜΡήΆ®ΙΐΫχ»κhandlerΡΘ Ϋ“Μ≤Ϋ≤Ϋ»ΞΖΟΈ Θ§Εχ«“’β―υΒΡΜΑ“λ≥Θ «ΧΊ»®ΦΕ”ΟMSPΘ§Τ’Ά®ΒΡ”ΟΜߥζ¬κ Ι”ΟΜßΦΕ”ΟPSPΘ§≤ΜΜα≥ωœ÷ ΐΨί“βΆβΜΞœύΗ…»≈ΚΆΤΤΜΒΘ§’β―υΒΡΜΑ’ϊΗωœΒΆ≥ΒΡΩ…ΩΩ–‘ΨΆΜαΚήΚΟΘ§Β±»ΜΈ“Ο«–¥–Γ≥Χ–ρΒΡ ±Κρ≤Μ±Ί’βΟ¥Ψ–ΫςΘ§Ζ¥’ΐΈ““ΜΑψΕΦ «“Μ÷±ΧΊ»®ΦΕ–Γ≥Χ–ρΓΘ

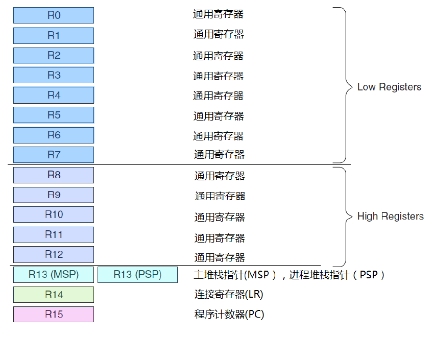

¥φ¥ΔΤς”≥…δ

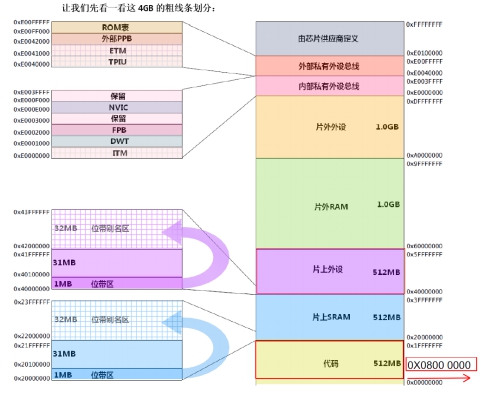

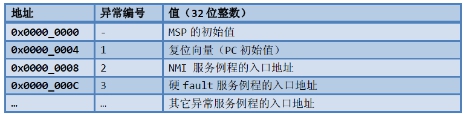

M3ΫΪΡΎ¥φΖ÷ΈΣ8Ηω÷ςΩιΘ§ΟΩΩι512MBΘ§œ»…œ“Μ’≈M3ΡΎΚΥΒΡ¥φ¥ΔΤς”≥…δΘΚ

ΥυΈΫΒΡSCS»γœ¬ΘΚ

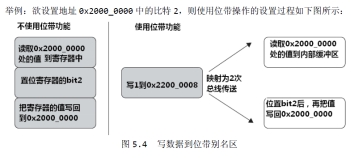

ΥυΈΫΒΡΈΜ¥χΨΆ «ΫΪΈΜ¥χ«χΒΡ1bit≈ρ’ΆΈΣΈΜ¥χ±πΟϊ«χΒΡ32bit“≤ΨΆ «“ΜΗωΉ÷Θ§Ά®ΙΐΖΟΈ ΈΜ¥χ±πΟϊ«χΨΆΡή¥οΒΫΖΟΈ ’βΗωbitΒΡΡΩΒΡΘ§”≈ Τ»γœ¬ΘΚ

Β±»ΜΈΜ¥χΜΙ”–“ΜΗωΟςœ‘ΒΡΚΟ¥ΠΘ§ΨΆ «‘ΎΕύ»ΈΈώΒΡœΒΆ≥÷–Θ§ΝΫΗω»ΈΈώΆ§ ±»Ξ–όΗΡ“ΜΗωΙ≤œμΦΡ¥φΤςΤδ÷–ΒΡΝΫΗωbitΒΡΜΑΩ…ΡήΜα≥ωœ÷ΓΑΈ…¬“œ÷œσΓ±Θ§Υυ“‘ΨΆ–η“ΣΫΪΓΑΕΝ-ΗΡ-–¥Γ±»ΐΧθ÷ΗΝνΦ”…œΝΌΫγ«χΒ» ÷ΕΈΘ§ΒΪ «”–ΝΥΈΜΕΈΘ§M3÷±Ϋ”»Ξ–¥Ρ«ΗωbitΒΡΈΜ¥χ±πΟϊ«χΨΆΩ…“‘ΝΥΘ§’β―υΨΆ≥…ΈΣΝΥ“ΜΗω‘≠Ή”≤ΌΉςΓΘ

≤ΜΙΐ…œΟφΒΡΆΦ»Ζ Β «¥÷œΏΧθΘ§œ¬Οφ…œ–ΨΤ§ ÷≤αΒΡœξœΗΆΦΤ§“Μ’≈ΘΚ

M3”––© ΐΨί¥ΪΥΆ÷ΗΝν÷ß≥÷Ζ«Ε‘Τκ ΐΨί¥ΪΥΆΘ§»γLDR/LDRH/LDRSHΓΘΤδΥϊ÷ΗΝν≤Μ÷ß≥÷ΓΘ

Ε‘Α¥Ή÷¥ΪΥΆά¥ΥΒΘ§»ΈΚΈ“ΜΗω≤ΜΡή±Μ4’ϊ≥ΐΒΡΒΊ÷ΖΕΦ «Ζ«Ε‘ΤκΒΡΓΘΕχΕ‘”ΎΑεΉ”Θ§»ΈΚΈ“ΜΗω≤ΜΡή±Μ2’ϊ≥ΐΒΡΒΊ÷ΖΕΦ «Ζ«Ε‘ΤκΒΡΓΘ

M3÷ß≥÷¥σΕΥΡΘ ΫΚΆ–ΓΕΥΡΘ ΫΘ§ΒΪ «ΆΤΦω Ι”Ο–ΓΕΥΡΘ ΫΓΘM3ΒΡ¥σΕΥΡΘ Ϋ «ΓΑΉ÷ΫΎ≤Μ±δ¥σΕΥΓ±ΓΘ

÷–ΕœΚΆ“λ≥Θ

“λ≥Θ «÷Η»ΈΚΈ¥ρΕœ≥Χ–ρΥ≥–ρ÷¥––ΒΡ ¬ΦΰΓΘ‘ΎΚήΕύ ±ΚρΘ§÷–ΕœΚΆ“λ≥Θ’βΝΫΗωΗ≈Ρν «≤ΜΉω«χΖ÷ΒΡΘ§Υυ“‘Έ““‘œ¬“≤ΨΆ≤ΜΉς«χΖ÷ΝΥΓΘ

M3ΒΡ“λ≥ΘœΒΆ≥Φρ÷±ΨΆ «ΥϋΒΡΨΪΜΣΥυ‘ΎΓΘ

M3ΒΡ“λ≥ΘΖ÷ΈΣœΒΆ≥“λ≥ΘΚΆΆβ≤Ω÷–ΕœΓΘ

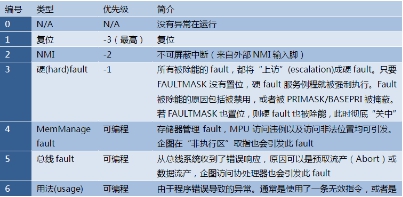

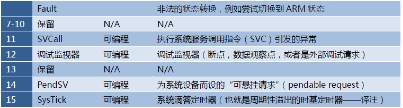

œΒΆ≥“λ≥Θ»γœ¬Θ®stm32―Ί”ΟΘ©ΘΚ

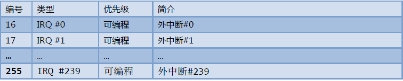

Άβ≤Ω÷–ΕœM3ΡΎΚΥ÷ß≥÷240ΗωΘ§stm32÷Μ Ι”ΟΤδ÷–60ΗωΘΚ

Υυ”–ΒΡ“λ≥ΘΘ§≥ΐΝΥΗ¥ΈΜΘ§NMIΘ§”≤FAULT”≈œ»ΦΕΈΣ-3Θ§-2Θ§-1ΙΧΕ®Θ§ Θœ¬ΒΡΕΦ «Ω…±ύ≥Χ”≈œ»ΦΕΓΘ

”≈œ»ΦΕΘΚ

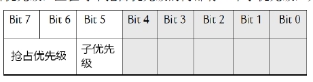

M3ΡΎΚΥ÷–”≈œ»ΦΕΦΡ¥φΤςΈΣ8ΈΜΘ§’β8ΈΜ≤Μ”Ο»Ϊ”ΟΒΫΘ§Ήν…Ό”ΟΒΫ3ΈΜΘ®MSBΕ‘ΤκΘ©Θ§stm32÷Μ”ΟΒΫΤδ÷–ΗΏΥΡΈΜΘ§Υυ“‘stm32ΉήΙ≤”–16÷÷”≈œ»ΦΕΓΘ

M3ΡΎΚΥ÷–Ε‘”ΎΆβ≤Ω÷–Εœ”–«ά’Φ”≈œ»ΦΕΚΆœλ”Π”≈œ»ΦΕΘ§ΗΏ«ά’Φ”≈œ»ΦΕΒΡ÷–ΕœΩ…“‘¥ρΕœΒΆ«ά’Φ”≈œ»ΦΕΒΡ÷–ΕœΓΘ«ά’Φ”≈œ»ΦΕœύΆ§ΒΡΝΫΗω÷–ΕœΆ§ ±ΒΫ¥οΘ§œλ”Πœλ”Π”≈œ»ΦΕΗΏΒΡ÷–ΕœΓΘ»γΙϊΝΫΗω÷–Εœ“Μ«–œύΆ§Θ§Ρ«Ο¥œλ”Π–ρΝ–Κ≈Ηϋ–ΓΒΡΡ«ΗωΓΘ

“ρΈΣΆβ≤Ω÷–ΕœΒΡ”≈œ»ΦΕΦΡ¥φΤςΉήΙ≤ΑΥΈΜΘ§Υυ“‘–η“ΣΕ‘ΤδΫχ––Μ°Ζ÷Θ§œλ”Π”≈œ»ΦΕ÷Ν…Ό”–“ΜΈΜΘ§Υυ“‘M3÷–Άβ≤Ω÷–Εœ«ά’Φ”≈œ»ΦΕΉνΕύΤδ Β «”–128ΗωΕχ≤Μ «256ΗωΓΘœ¬ΆΦ «¥”bit5ΩΣ ΦΜ°Ζ÷Θ§ΉήΙ≤”ΟΒΫ»ΐΈΜ…η÷Ο”≈œ»ΦΕΘΚ

ΨΏΧεΒΡ–ΨΤ§ΨωΕ®”≈œ»ΦΕ”ΟΒΫΕύ…ΌΈΜΘ§“‘ΦΑ¥”ΡΡ“ΜΈΜΩΣ ΦΜ°Ζ÷«ά’ΦΚΆœλ”ΠΘ§stm32”ΟΒΫ4ΈΜ…η÷Ο÷–ΕœΘ§”–5÷÷Ζ÷ΉιΘΚΉι0¥”7bitΜ°Ζ÷Θ®»Ϊ≤ΩΕΦ «œλ”Π”≈œ»ΦΕΘ©Θ§Ήι1¥”6bitΜ°Ζ÷Θ§Ήι2¥”5bitΜ°Ζ÷Θ§Ήι3¥”4bitΜ°Ζ÷Θ§Ήι4¥”3bitΜ°Ζ÷Θ®ΨΆ «÷Μ”ΟΒΫ«ά’Φ”≈œ»ΦΕΘ©ΓΘ

œρΝΩ±μΘΚ

Β±ΖΔ…ζΝΥ“λ≥Θ–η“Σœλ”ΠΒΡ ±ΚρΘ§M3–η“ΣΕ®ΈΜΤδΖΰΈώάΐ≥ΧΒΡ»κΩΎΒΊ÷ΖΘ§’β–©»κΩΎΒΊ÷ΖΨΆ¥φ‘ΎΥυΈΫΒΡΓΑœρΝΩ±μΓ±ΓΘ»± Γ«ιΩωœ¬Θ§’β’≈±μ¥φ‘Ύ0ΒΊ÷Ζ¥ΠΘ®Β±»Μ“≤Ω…–όΗΡNVIC÷–ΒΡœρΝΩ±μΤΪ“ΤΦΡ¥φΤςά¥÷ΊΕ®ΈΜœρΝΩ±μΘ©Θ§ΟΩ“ΜΗω±μœν’Φ4Ή÷ΫΎΓΘ

»γœ¬ΘΚ

Ήœ»œρΝΩ±μΒΡΩΣΆΖ «÷ςΕ―’ΜΒΡΒΊ÷ΖΓΘ

Ω…“‘Ω¥≥ωΘ§≤Μ¬έ»γΚΈ“ΜΗωœρΝΩ±μ÷Ν…ΌΑϋΚ§œ¬Οφ4Ηω±μœνΘΚ

1.MSP≥θ Φ÷Β

2.Η¥ΈΜœρΝΩ

3.NMI

4.”≤faultΖΰΈώάΐ≥Χ

÷–ΕœΒΡ δ»κ”κΙ“ΤπΘΚ

Β±÷–Εœ δ»κΫ≈±Μ÷ΟΈΣ”––ßΚσΘ§ΗΟ÷–ΕœΨΆ±Μ–ϋΤπΘ§ΒΫΝΥœΒΆ≥÷–ΥϋΒΡ”≈œ»ΦΕΉνΗΏΒΡ ±ΚρΘ§ΨΆΜαΒΟΒΫœλ”ΠΓΘ

ΒΪ «Β±Ρ≥Ηω÷–ΕœΒΟΒΫœλ”Π÷°«ΑΘ§Τδ–ϋΤπΈΜ±Μ«ε≥ΐΘ§‘ρ÷–Εœ±Μ»ΓœϊΓΘΘ®Υυ“‘stm32ΕΦ «‘Ύ÷–ΕœΖΰΈώ≥Χ–ρΒΡΉνΚσ«ε≥ΐ÷–Εœ±ξ÷ΨΈΜΘ©

Β±Ρ≥÷–ΕœΒΡΖΰΈώάΐ≥ΧΩΣ Φ÷¥––ΒΡ ±ΚρΘ§ΨΆ≥Τ¥Υ÷–ΕœΫχ»κΝΥΓΑΜν‘ΨΓ±Ή¥Χ§Θ§≤Δ«“Τδ–ϋΤπΈΜΜα±ΜΉ‘Ε·«ε≥ΐΓΘ

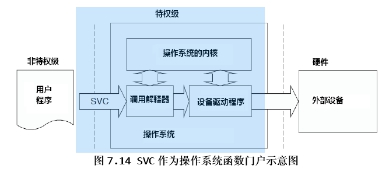

SVCΚΆPENDSVCΘΚ

Ήœ»SVCΘ®œΒΆ≥ΖΰΈώΒς”ΟΘ©ΚΆPENDSVCΘ®Ω…Ι“ΤπœΒΆ≥ΖΰΈώΒς”ΟΘ©ΒΡ«χ±π‘Ύ”ΎSVC“λ≥Θ±Ί–κΝΔΦ¥ΒΟΒΫœύ”ΠΘ§ΕχPENDSVC‘ρ≤Μ «Θ§ΥϊΩ…“‘œώΤ’Ά®÷–Εœ“Μ―υ±ΜΙ“ΤπΘ§÷ΣΒάΤδΥϊ÷Ί“Σ»ΈΈώΆξ≥…≤≈÷¥––ΥϋΘ§Ι“ΤπPENDSVCΒΡΖΫ ΫΈΣΘΚ ÷ΙΛ–¥»κNVICΒΡPENDSVCΙ“ΤπΦΡ¥φΤςΓΘ

SVCΒΡ”ΟΆΨΘΚ≤ΌΉςœΒΆ≥Ω…“‘≤Μ»Ο”ΟΜß÷±Ϋ”ΖΟΈ ”≤ΦΰΘ§Εχ «Ά®Ιΐ¥ΞΖΔSVC“λ≥Θά¥ Ι”ΟSVCœΒΆ≥Βς”Οά¥»Ο”ΟΜß≥Χ–ρΦρΫιΖΟΈ ”≤ΦΰΓΘΚΟ¥ΠΘΚ1.OSΗΚ‘πΨΏΧε”≤ΦΰΘ§”ΟΜß≥Χ–ρ≤Μ±ΊΜ®Ζ―–ΡΥΦΩΊ÷Τ”≤ΦΰΓΘ2.OSΒΡ¥ζ¬κ”ΠΗΟ «Ψ≠Ιΐ≥δΖ÷ΒΡ≤β ‘ΒΡΘ§Υυ“‘’ϊΗωœΒΆ≥Ω…ΩΩ–‘ΗΏΫΓΉ≥–‘ΚΟΓΘ3.”ΟΜß≥Χ–ρΈό–η‘ΎΧΊ»®ΦΕœ¬÷¥––Θ§Έό–ηΒΘ”«“ρΈσ≤ΌΉς»ΟœΒΆ≥Χ±ΜΨΓΘ4.Ά®ΙΐSVCΜζ÷ΤΘ§”ΟΜß≥Χ–ρ”κ”≤ΦΰΈόΙΊΓΘ

PENDSVCΒΡ”Ο¥ΠΘΚ…œœ¬ΈΡ«–ΜΜΘ§»γucos…œœ¬ΈΡ«–ΜΜΨΆ «”ΟΒΫPENDSVCΒΡΓΘ

NVICΘΚ

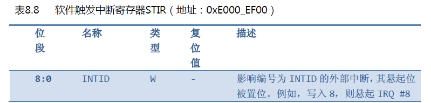

÷–ΕœœρΝΩΩΊ÷ΤΤςΘ§“≤ΨΆ «ΩΊ÷Τ÷–ΕœœρΝΩΒΡΒΊΖΫΘ§ΟΩΗωΆβ≤Ω÷–ΕœΘ®œΒΆ≥÷–Εœ”…SCBΩΊ÷ΤΘ©ΕΦ‘ΎΤδ÷–ΒΡΦΡ¥φΤς’Φ”–“Μœ·÷°ΒΊΘ§ΦΡ¥φΤςΝ–±μ»γœ¬ΘΚ

Τδ÷––ϋΤπΦΡ¥φΤςΩ…“‘œΒΆ≥Ή‘Ε·…η÷ΟΘ§“≤Ω…“‘ ÷ΙΛ–όΗΡ“‘–ϋΤπ“ΜΗω÷–ΕœΓΘ

»μΦΰ÷–ΕœΦΡ¥φΤς“≤¬υ÷Ί“ΣΒΡΘ§»γœ¬ΘΚ

÷–ΕœΒΡœλ”ΠΚΆΖΒΜΊΘΚ

÷–ΕœΒΡœλ”ΠΘΚ

8ΗωΦΡ¥φΤς“‘ΦΑ»κ’ΜΥ≥–ρ»γœ¬ΘΚ

÷–ΕœΒΡΖΒΜΊΘΚ

Ήœ»¥ΞΖΔ÷–ΕœΖΒΜΊΒΡ÷ΗΝν”–»ΐ÷÷ΘΚ

ΖΒΜΊΝΥ÷°ΚσΘ§Ήω»γœ¬ΝΫΦΰ ¬ΘΚ

1.≥ω’ΜΘ§ΜΊΗ¥œ÷≥Γ

2.Ηϋ–¬NVICΦΡ¥φΤς

“ßΈ≤÷–ΕœΘΚ

“ΜΆΦ“‘±Έ÷°ΘΚ

ΤδΥϊ

ΉήΫαΝΥ“ΜΧλΘ§÷’”ΎΒΫΝΥ’β“Μ≤ΫΘ§ΜΙ”––©ΝψΥιΒΡ÷Σ ΕΒψ–¥…œΘΚ

M3ΒΡΕ―’Μ «œρœ¬…ζ≥ΛΒΡΓΘ

M3»Γ÷ΗΘ§Ϋβ¬κΘ§÷¥––»ΐΦΕΝςΥ°Θ§“ρΈΣΤδ≤…”ΟΙΰΗΞΧεΫαΙΙΘ§Υυ“‘»Γ÷ΗΚΆΖΟ¥φΩ…“‘Ά§ ±÷¥––Θ§M3ΡΎ≤Ω”–Ϋβ¬κΡΘΩιΘ§Υυ“‘ΙΙ≥…ΝΥ»ΐΦΕΝςΥ°ΓΘ |