| ±ύΦ≠ΆΤΦω: |

±ΨΈΡΫΪΧΫΧ÷ZIFΦήΙΙΒΡ÷νΕύ”≈ ΤΘ§Ϋι…ή’β–©”≈ Τ»γΚΈ ΙΈόœΏΒγ…ηΦΤ–‘Ρή¥οΒΫΒΡ–¬ΗΏΕ»ΓΘ

±ΨΈΡά¥Ή‘”Ύ≤©ΩΆ‘ΑΘ§”…ΜπΝζΙϊ»μΦΰLinda±ύΦ≠ΓΔΆΤΦωΓΘ

|

|

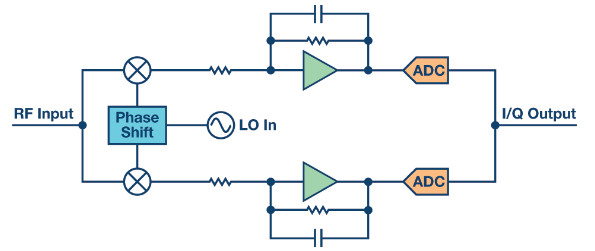

Νψ÷–ΤΒ(ZIF)ΦήΙΙΉ‘ΈόœΏΒγ≥θΤΎΦ¥“―≥ωœ÷ΓΘ»γΫώΘ§ZIFΦήΙΙΩ…“‘‘ΎΦΗΚθΥυ”–œϊΖ―ΈόœΏΒγ”Π”Ο÷–’“ΒΫΘ§Έό¬έ «Βγ ”ΓΔ ÷ΜζΘ§ΜΙ «άΕ―άΦΦ θΓΘZIFΦΦ θ»ΓΒΟΒΡΉν–¬Ϋχ≤ΫΕ‘œ÷”–ΗΏ–‘ΡήΈόœΏΒγΦήΙΙ–Έ≥…ΝΥΧτ’ΫΘ§Τδ¥χά¥ΒΡ–¬≤ζΤΖ»ΓΒΟΝΥ–‘Ρή…œΒΡΆΜΤΤΘ§ΡήΙΜ Βœ÷ZIFΦΦ θ“‘«ΑΆϊ≥ΨΡΣΦΑΒΡ–¬–Ά”Π”ΟΓΘ±ΨΈΡΫΪΧΫΧ÷ZIFΦήΙΙΒΡ÷νΕύ”≈ ΤΘ§Ϋι…ή’β–©”≈ Τ»γΚΈ ΙΈόœΏΒγ…ηΦΤ–‘Ρή¥οΒΫΒΡ–¬ΗΏΕ»ΓΘ

ΈόœΏΒγΙΛ≥Χ ΠΟφΝΌΒΡΧτ’Ϋ

≤ΜΕœ‘ωΕύΒΡ–η«σΗχΒ±ΫώΒΡ ’ΖΔΤςΦήΙΙ Π¥χά¥ΝΥΧτ’ΫΘ§“ρΈΣΈ“Ο«Ε‘ΈόœΏ…η±ΗΚΆ”Π”ΟΒΡ–η«σ≥ ≥÷–χ‘ω≥Λ÷° ΤΓΘΫαΙϊΘ§œϊΖ―’Ώ–η“Σ≥÷–χΖΟΈ ΗϋΕύΒΡ¥χΩμΓΘ

ΐΡξ“‘ά¥Θ§…ηΦΤ Π“―Ψ≠¥”ΒΞ‘Ί≤®ΈόœΏΒγΉΏœρΕύ‘Ί≤®ΈόœΏΒγΦΦ θΓΘΒ±“ΜΗωΤΒΕΈΒΡΤΒΤΉ±Μ»Ϊ≤Ω’Φ”Ο ±Θ§ΨΆΖ÷≈δ–¬ΒΡΤΒΕΈΘΜΡΩ«ΑΘ§±Ί–κΈΣ40ΕύΗωΈόœΏΤΒΕΈΧαΙ©ΖΰΈώΓΘ”…”Ύ‘Υ”Σ…Χ‘ΎΕύΗωΤΒΕΈΕΦ”–ΤΒΤΉΘ§≤Δ«“’β–©Ή ‘¥±Ί–κ–≠ΒςΤπά¥Θ§Υυ“‘Θ§»γΫώΒΡ«ς Τ «ΉΏœρ‘Ί≤®ΨέΚœΘ§Εχ‘Ί≤®ΨέΚœ‘ρΜαΒΦ÷¬ΕύΤΒΕΈΈόœΏΒγΓΘ’β”÷Μα¥χά¥ΗϋΕύΒΡΈόœΏΒγΘ§Τδ–‘ΡήΗϋΗΏΘ§–η“ΣΗϋ”≈–ψΒΡ¥χΆβ“÷÷Τ–‘ΡήΘ§Ηϋ≥ω…ΪΒΡΖχ…δ–‘ΡήΘ§“‘ΦΑΗϋΒΆΒΡΙΠΚΡΥ°ΤΫΓΘ

Υδ»ΜΈόœΏ–η«σ‘ΎΩλΥΌ‘ω≥ΛΘ§ΒΪΙΠΚΡΚΆΩ’Φδ‘ΛΥψ≤ΔΈ¥‘ω≥ΛΓΘ ¬ Β…œΘ§‘ΎΙΠΚΡΚΆΩ’ΦδΫΎ Γ–η«σ≤ΜΕœ‘ω«ΩΒΡΧθΦΰœ¬Θ§Ά§ ±ΫΒΒΆΧΦ≈≈Ζ≈ΚΆΈοάμ≥Ώ¥γΖ«≥Θ÷Ί“ΣΓΘΈΣΝΥ Βœ÷’β–©ΡΩ±ξΘ§–η“Σ¥”–¬ΒΡ ”Ϋ«»Ξ»œ ΕΈόœΏΒγΦήΙΙΚΆΖ÷«χΓΘ

Φ·≥…

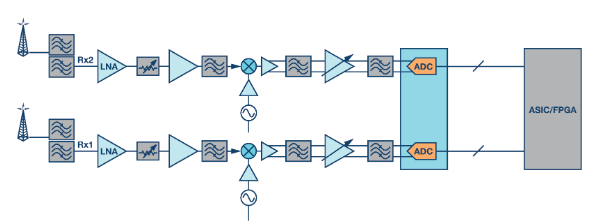

ΈΣΝΥ‘ωΦ”ΧΊΕ®…ηΦΤ÷–ΒΡΈόœΏΒγ ΐΡΩΘ§±Ί–κΦθ–ΓΟΩΦΰΈόœΏΒγΤςΦΰΒΡ≥Ώ¥γΓΘ¥ΪΆ≥ΖΫΖ® «÷π≤ΫΑ―ΗϋΕύΒΡ…ηΦΤΦ·≥…ΒΫ“ΜΤ§ΙηΤ§Β±÷–ΓΘΥδ»Μ¥” ΐΉ÷Ϋ«Ε»ά¥Ω¥Θ§’β―υΉωΩ…Ρή «ΚœάμΒΡΘ§ΒΪ «Θ§ΈΣΝΥΦ·≥…ΕχΦ·≥…ΡΘΡβΙΠΡήΒΡΉωΖ®≤ΜΦϊΒΟ”–“β“εΓΘΤδ÷–“ΜΗω‘≠“ρ «Θ§ΈόœΏΒγ÷–ΒΡ–μΕύΡΘΡβΙΠΡή «ΈόΖ®”––ßΦ·≥…ΒΡΓΘάΐ»γΘ§‘ΎΆΦ1Υυ ΨΒΡ¥ΪΆ≥÷–ΤΒ≤…―υΫ” ’Τς÷–Θ§÷–ΤΒ≤…―υΦήΙΙ”–ΥΡΗωΜυ±ΨΦΕΘΚΒΆ‘κ…υ‘ω“φΚΆ…δΤΒ―Γ‘ώΦΕΓΔΤΒ¬ ΉΣΜΜΦΕΓΔ÷–ΤΒ‘ω“φΚΆ―Γ‘ώΦΕ“‘ΦΑΦλ≤βΦΕΓΘ―Γ‘ώΦΕ“ΜΑψ Ι”ΟSAW¬Υ≤®Τς’β–©ΤςΦΰΕΦ≤ΜΡήΦ·≥…Θ§“ρ¥ΥΘ§±Ί–κ≤Ω π‘ΎΤ§ΆβΓΘΥδ»Μ…δΤΒ―Γ‘ώΦΕ «”…―ΙΒγΜρΜζ–ΒΤςΦΰΧαΙ©ΒΡΘ§ΒΪ”– ±÷–ΤΒ¬Υ≤®ΤςΜα Ι”ΟLC¬Υ≤®ΤςΓΘΨΓΙήLC¬Υ≤®Τς”– ±Ω…ΡήΜαΦ·≥…ΒΫΒΞΤ§ΫαΙΙ÷–Θ§ΒΪ «Θ§¬Υ≤®Τς–‘ΡήΒΡΈΰ…ϋΘ®QΚΆ≤ε»κΥπΚΡΘ©“‘ΦΑ ΐΉ÷Μ·ΤςΘ®Φλ≤®ΤςΘ©≤…―υΥΌ¬ ±Ί“ΣΒΡ‘ωΦ”ΜαΧαΗΏΉήΙΠΚΡΓΘ

ΆΦ1.¥ΪΆ≥–Ά÷–ΤΒ≤…―υΫ” ’Τς

ΐΉ÷Μ·ΤςΘ®ΡΘ ΐΉΣΜΜΤςΘ©±Ί–κ“‘ΒΆ≥…±ΨCMOSΙΛ“’÷Τ≥…Θ§“‘ Ι≥…±ΨΚΆΙΠΚΡ±Θ≥÷”ΎΚœάμΥ°ΤΫΓΘΒ±»ΜΩ…“‘”ΟΥΪΦΪ–‘ΙΛ“’÷Τ‘λΘ§ΒΪΫαΙϊΜαΒΦ÷¬ΤςΦΰ≥Ώ¥γΚΆΙΠΚΡΒΡ‘ωΦ”Θ§”–ψΘ”Ύ”≈Μ·≥Ώ¥γΒΡ≥θ÷‘ΓΘΥυ“‘Θ§±ξΉΦCMOSΙΛ“’ «’β÷÷ΙΠΡήΒΡΉνΦ―÷Τ‘λΙΛ“’ΓΘ’βΨΆΈΣΦ·≥…ΗΏ–‘ΡήΖ≈¥σΤςΘ§”»Τδ «÷–ΤΒΦΕΘ§‘λ≥…ΝΥΦΪ¥σΒΡΧτ’ΫΓΘΥδ»ΜCMOSΙΛ“’Ω…“‘Φ·≥…Ζ≈¥σΤςΘ§ΒΪ «ΚήΡ―¥”’κΕ‘ΒΆΙΠΚΡΚΆΒΆΒγ―ΙΕχ”≈Μ·ΙΐΒΡΙΛ“’÷–»ΓΒΟ–η“ΣΒΡ–‘ΡήΓΘΝμΆβΘ§‘ΎΤ§…œΦ·≥…ΜλΤΒΤςΚΆ÷–ΤΒΖ≈¥σΤς“Σ«σΑ―ΦΕΦδ–≈Κ≈¬Ζ”…ΒΫΤ§ΆβΘ§“‘±ψΖΟΈ ÷–ΤΒΚΆΩΙΜλΒΰ¬Υ≤®ΤςΘ§»ΜΚσ‘Ό ΐΉ÷Μ·Θ§“ρΕχ ß»ΞΝΥΦ·≥…ΒΡ÷νΕύ”≈ ΤΓΘ’β―υΉωΨΆ¥ο≤ΜΒΫΦ·≥…ΒΡΡΩΒΡΘ§“ρΈΣΫαΙϊΜα‘ωΦ”“ΐΫ≈ ΐΚΆΖβΉΑ≥Ώ¥γΓΘΝμΆβΘ§ΙΊΦϋΒΡΡΘΡβ–≈Κ≈ΟΩ¥ΈΆ®Ιΐ“ΜΗωΖβΉΑ“ΐΫ≈ ±Θ§ΨΆΜαΈΰ…ϋ“Μ–©–‘ΡήΓΘ

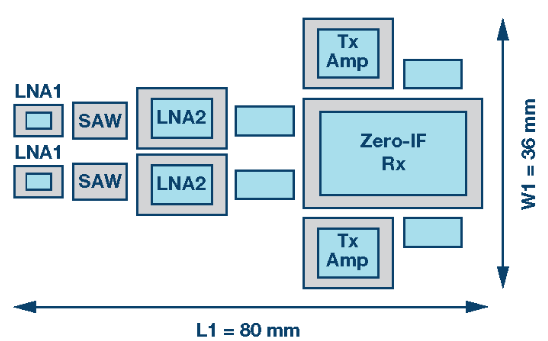

ΉνΦ―Φ·≥…ΖΫ Ϋ «Ε‘œΒΆ≥Ζ÷«χΘ§œϊ≥ΐ≤ΜΡήΦ·≥…ΒΡ‘ΣΦΰΓΘ”…”Ύ≤ΜΡή”––ßΒΊΦ·≥…SAWΚΆLC¬Υ≤®ΤςΘ§Υυ“‘Θ§ΉνΦ――Γ‘ώ «»ΖΕ®»γΚΈΆ®Ιΐ÷Ί–¬…ηΦΤΦήΙΙά¥œϊ≥ΐΥϋΟ«ΓΘΆΦ2’Ι ΨΝΥ“ΜΗωΒδ–ΆΒΡΝψ÷–ΤΒ–≈Κ≈Ν¥Θ§ΥϋΑ―…δΤΒ–≈Κ≈÷±Ϋ”ΉΣΜΜΈΣ“ΜΗωΗ¥ΚœΜυ¥χΘ§Άξ»Ϊœϊ≥ΐΝΥ÷–ΤΒ¬Υ≤®ΤςΚΆ÷–ΤΒΖ≈¥σΤςΒΡ±Ί“Σ–‘Θ§ΫαΙϊ Βœ÷ΝΥ’β–©ΡΩ±ξΓΘ―Γ‘ώΦΕ‘ρΆ®Ιΐ‘ΎI/QΜυ¥χ–≈Κ≈Ν¥άο“ΐ»κ“ΜΕ‘ΒΆΆ®¬Υ≤®ΤςΒΡΖΫ Ϋ”η“‘ Βœ÷Θ§’βΕ‘¬Υ≤®ΤςΩ…“‘ΉςΈΣ”–‘¥ΒΆΆ®¬Υ≤®ΤςΕχΖ«ΙΠΚΡΫœΗΏΒΡΤ§ΆβΙΧΕ®÷–ΤΒΤςΦΰΦ·≥…ΓΘ¥ΪΆ≥–Ά÷–ΤΒSAW¬Υ≤®ΤςΜρLC¬Υ≤®ΤςΧλ…ζΨΆ «ΙΧΕ®–ΆΤςΦΰΘ§Εχ’β–©”–‘¥¬Υ≤®Τς‘ρΩ…“‘ΒγΉ”ΖΫ ΫΘ§‘Ύ ΐΑΌkHz÷Ν ΐΑΌmHzΒΡΖΕΈßΡΎΒς–≥ΓΘΗΡ±δΜυ¥χ¥χΩμΨΆΡή ΙΆ§“ΜΤςΦΰΗ≤Η«ΖΕΈßΗϋΩμΒΡ¥χΩμΘ§Έό–ηΗΡ±δΈοΝœ«εΒΞΘ§“≤≤Μ”Ο‘Ύ≤ΜΆ§ΒΡΙΧΕ®÷–ΤΒ¬Υ≤®Τς÷°Φδά¥ΜΊ«–ΜΜΓΘ

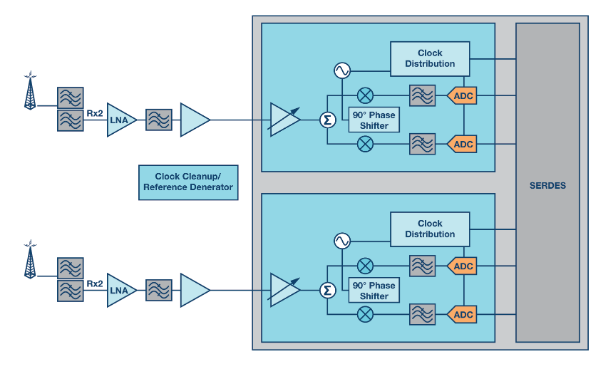

ΆΦ2.Βδ–ΆΒΡΝψ÷–ΤΒ≤…―υΫ” ’Τς

Υδ»ΜΆΦ Ψ≤Δ≤Μ÷±ΙέΘ§ΒΪΆ®ΙΐΗϋΗΡ±Ψ’ώΘ§Νψ÷–ΤΒΫ” ’Τς“≤Ω…Η≤Η«ΖΕΈßΖ«≥ΘΩμΒΡ…δΤΒΤΒ¬ ΓΘΝψ÷–ΤΒ ’ΖΔΤςΩ…ΧαΙ©’φ’ΐΒΡΩμ¥χΧε―ιΘ§Βδ–ΆΝ§–χΗ≤Η«ΖΕΈß¥” ΐΑΌMHzΒΫ‘Φ6GHzΓΘ≤Μ Ι”ΟΙΧΕ®¬Υ≤®ΤςΘ§Ω…“‘ Βœ÷’φ’ΐΝιΜνΒΡΈόœΏΒγΘ§ΫαΙϊΩ…“‘ΦΪ¥σΒΊΦθ…ΌΘ§…θ÷ΝΩ…Ρήœϊ≥ΐ‘ΎΩΣΖΔΈόœΏΒγ…ηΦΤΤΒΕΈ±δΧεΖΫΟφΒΡΆΕ»κΓΘΒΟ“φ”ΎΝιΜνΒΡ ΐΉ÷Μ·ΤςΚΆΩ…±ύ≥ΧΒΡΜυ¥χ¬Υ≤®ΤςΘ§Νψ÷–ΤΒ…ηΦΤ≤ΜΒΪΡή Βœ÷ΗΏ–‘ΡήΘ§ΜΙΨΏ”–ΦΪ¥σΒΡΝιΜν–‘Θ§Φ»Ρή÷ß≥÷ΖΕΈß≥§ΩμΒΡΤΒ¬ ΚΆ¥χΩμΘ§“≤ΡήΈ§≥÷ΫϋΚθΤΫΧΙΒΡ–‘ΡήΘ§Εχ«“Έό–η’κΕ‘ΟΩ÷÷≈δ÷Ο”≈Μ·ΡΘΡβΒγ¬ΖΘ®»γ¬Υ≤®ΤςΘ©ΓΣΩ…ΈΫΟϊΖϊΤδ ΒΒΡ»μΦΰΕ®“εΈόœΏΒγ(SDR)ΦΦ θΓΘ”κ¥ΥΆ§ ±Θ§’β÷÷ΖΫΖ®“≤Μα¥σΖυΦθ–Γ≥Ώ¥γΘ§“ρΈΣΥϋΈΣ±Ί–κΗ≤Η«ΕύΗωΤΒΕΈΒΡ”Π”Οœϊ≥ΐΝΥ‘≠±Ψ–η“ΣΒΡ¬Υ≤®ΤςΉιΓΘ‘Ύ“Μ–©«ιΩωœ¬Θ§Ω…“‘Άξ»Ϊœϊ≥ΐ…δΤΒ¬Υ≤®ΤςΘ§≥…ΨΆΆξ»Ϊ“β“ε…œΒΡΩμ¥χΈόœΏΒγΘ§ΗυΨί≤Μ–η“ΣΗϋΗΡΤΒΕΈΓΘΆ®Ιΐœϊ≥ΐ≤ΩΖ÷ΤςΦΰΓΔΦ·≥…ΤδΥϊΤςΦΰΘ§Ω…“‘¥σΖυΦθ–ΓΝψ÷–ΤΒ…ηΦΤΥυ–η“ΣΒΡPCB≥Ώ¥γΘ§≤ΜΒΪΦρΜ·ΝΥΤΒΕΈΗΏΥΌΙΐ≥ΧΘ§ΜΙΡήΦθ…Ό”–±Ί“ΣΗϋΗΡ≥Ώ¥γ ±ΆΕ»κΒΡΨΪΝΠΓΘ

Ήν–ΓΒΡ≥Ώ¥γ

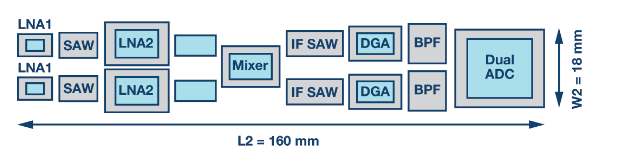

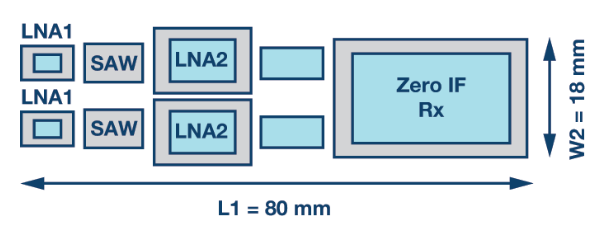

Ά®Ιΐ÷±Ϋ”±»Ϋœ’β–©ΦήΙΙΒΡPCBΟφΜΐΘ®ΆΦ3ΚΆΆΦ4Θ©Ω…÷ΣΘ§Ε‘”ΎΥΪΫ” ’¬ΖΨΕΘ§‘ΎΚœάμ Βœ÷ΖΫ Ϋœ¬Θ§÷–ΤΒ≤…―υΚΆΝψ÷–ΤΒ≤…―υΒΡPCBΟφΜΐΖ÷±πΈΣ2880mm2

(18mmΓΝ160mm)Θ§ΚΆ1434mm2 (18mmΓΝ80mm)ΓΘ»γΙϊ≤ΜΥψΩ…Ρήœϊ≥ΐΒΡ…δΤΒ¬Υ≤®ΤςΚΆΤδΥϊΦρΜ·…ηΦΤΘ§2Νψ÷–ΤΒΦήΙΙ”–Ω…Ρή±»Β±«ΑΒΡ÷–ΤΒ≤…―υΦΦ θΦθ…ΌΉνΗΏ¥ο50%ΒΡΈόœΏΒγ≥Ώ¥γΓΘΈ¥ά¥ΒΡ…ηΦΤ”–Ω…ΡήΆ®ΙΐΕνΆβΒΡΦ·≥…Θ§ Ι≥Ώ¥γ‘ΌΦθ…Ό“Μ±ΕΓΘ

ΆΦ3.Βδ–ΆΒΡ÷–ΤΒ≤…―υ≤ΦΨ÷ΆΦ

ΆΦ4.Βδ–ΆΒΡΝψ÷–ΤΒ≤…―υ≤ΦΨ÷

ΉνΒΆ≥…±Ψ

÷±Ϋ”¥”ΈοΝœ«εΒΞά¥Ω¥Θ§¥”÷–ΤΒ≤…―υœΒΆ≥ΉΣœρΝψ÷–ΤΒΦήΙΙΩ…ΫΎ Γ33%ΒΡΈοΝœΓΘ≥…±ΨΖ÷Έω Φ÷’ΕΦ «Ζ«≥ΘάßΡ―ΒΡΓΘ»ΜΕχΘ§…ν»κΩΦ≤λΆΦ1ΚΆΆΦ2Ω…÷ΣΘ§–μΕύΖ÷ΝΔ Ϋ‘ΣΦΰΨυ“―œϊ≥ΐΘ§Αϋά®÷–ΤΒΚΆΩΙΜλΒΰ¬Υ≤®‘ΣΦΰΘ§≤Δ«“ΜλΤΒΤςΚΆΜυ¥χΖ≈¥σΤςΨυ“―Φ·≥…ΓΘ≤ΜΟς»ΖΒΡ «Θ§”…”ΎΝψ÷–ΤΒΫ” ’Τς±Ψ…μΨΏ”–¥ΪΆ≥÷–ΤΒ≤…―υΦήΙΙ≤ΜΨΏ±ΗΒΡ¥χΆβ“÷÷ΤΙΠΡήΘ§Υυ“‘Θ§’ϊΧεΆβ≤Ω¬Υ≤®“Σ«σΨΆ¥σΖυΫΒΒΆΝΥΓΘΝψ÷–ΤΒΦήΙΙ÷–ΝΫΗω‘ΣΦΰ¥Ό≥…ΝΥ’β“ΜΫαΙϊΓΘΒΎ“ΜΗω‘ΣΦΰ «”–‘¥Μυ¥χ¬Υ≤®ΤςΘ§ΗΟ¬Υ≤®ΤςΆ§ ±ΨΏ±Η¥χΡΎ‘ω“φΚΆ¥χΆβ“÷÷ΤΙΠΡήΓΘΒΎΕΰΗω‘ΣΦΰ «ΗΏ≤…―υΥΌ¬ ΒΆΆ®Π≤-ΠΛΉΣΜΜΤςΘ§”Ο”ΎΕ‘I/Q–≈Κ≈Ϋχ–– ΐΉ÷Μ·ΓΘ”–‘¥¬Υ≤®ΤςΦθ…ΌΝΥ¥χΆβ‘ΣΦΰΘ§ΕχADCΒΡΗΏ≤…―υΥΌ¬ ‘ρ ΙΜλΒΰΒψΧαΗΏΒΫΉψΙΜΗΏΒΡΤΒ¬ Θ§¥”Εχœϊ≥ΐΝΥΆβ≤ΩΩΙΜλΒΰ¬Υ≤®‘ΣΦΰΒΡ±Ί“Σ–‘Θ®“ρΈΣ”–‘¥¬Υ≤®Τς“―Ψ≠≥δΖ÷ΒΊ“÷÷ΤΝΥ–≈Κ≈Θ©ΓΘ

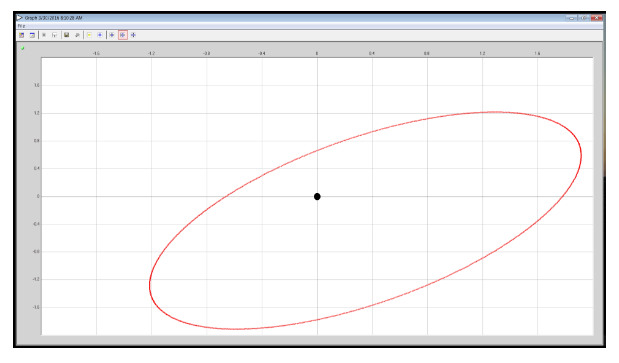

Ά®ΙΐΑ―Μυ¥χ–≈Κ≈ ©Φ”ΒΫ”–‘¥¬Υ≤®Τς…œΘ§»γΆΦ5Υυ ΨΘ§Ω…“‘ΙωΫΒΗΏΤΒΡΎ»ίΓΘ»ΜΚσΘ§ADCΕ‘ά¥Ή‘ΒΆΆ®¬Υ≤®ΤςΒΡ»ΈΚΈ≤–”ύ δ≥ω–≈Κ≈Ϋχ–– ΐΉ÷Μ·ΚΆΉν÷’¬Υ≤®ΓΘ

ΆΦ5.”–‘¥Μυ¥χ¬Υ≤®Τς”κADC

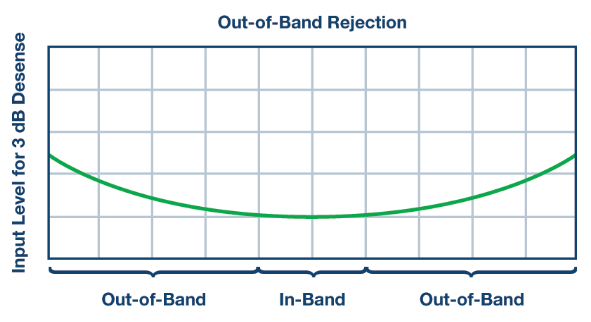

ΦΕΝΣΫαΙϊ»γΆΦ6Υυ ΨΓΘ¥ΥΆΦΥυ ΨΈΣ‘Ύ”–‘¥¬Υ≤®ΤςΚΆΠ≤-ΠΛADCΗ¥Κœ–ß”ΠΉς”Οœ¬ΒΡΒδ–ΆΫ” ’Τς–‘ΡήΓΘ’βάο’Ι ΨΒΡ «¥χΡΎΚΆ¥χΆβΙΠ¬ ΝιΟτΕ»ΫΒΒΆ3dBΒΡΒδ–Ά«ιΩωΓΘΉΔ“βΘ§‘Ύ≤Μ Ι”Ο»ΈΚΈΆβ≤Ω¬Υ≤®‘ΣΦΰΒΡ«ιΩωœ¬Θ§¥χΆβ–‘Ρή”–ΥυΗΡ…ΤΓΘ

ΆΦ6.Βδ–ΆΒΡΝψ÷–ΤΒ¥χΆβ“÷÷Τ

ΈΣΝΥΜώΒΟάύΥΤΒΡ–‘ΡήΥ°ΤΫΘ§÷–ΤΒ≤…―υΫ” ’Τς≤…”ΟΖ÷ΝΔ Ϋ÷–ΤΒ¬Υ≤®‘ΣΦΰΘ®»γSAWΦΦ θΘ©ά¥ Βœ÷―Γ‘ώ–‘ΚΆ¥χΆβ–≈Κ≈±ΘΜΛΙΠΡήΘ§“‘Ζά÷ΙΩμ¥χ–≈Κ≈ΜλΒΰΚΆ‘κ…υΜλΒΰΜΊΤΒΕΈΒ»Έ ΧβΓΘ÷–ΤΒ≤…―υΦήΙΙΜΙ±Ί–κ≤…»ΓΤδΥϊΈό”ΟΜλΤΒΤςœνΒΡ±ΘΜΛ¥κ ©Θ§Αϋά®Ακ÷–ΤΒœνΘ§ΗΟœνΜαΧαΗΏ…δΤΒΚΆ÷–ΤΒ¬Υ≤®“Σ«σ≤Δœό÷Τ≤…―υΥΌ¬ ΚΆ÷–ΤΒΙφΜ°ΓΘΝψ÷–ΤΒΦήΙΙ≤Μ¥φ‘Ύ’β÷÷ΤΒ¬ ΙφΜ°œό÷ΤΓΘ

ΗυΨί…ηΦΤΚΆ”Π”ΟΒΡ≤ΜΆ§Θ§’β÷÷‘≠…ζ“÷÷ΤΙΠΡήΩ…“‘ΫΒΒΆΜρœϊ≥ΐΆβ≤Ω…δΤΒ¬Υ≤®“Σ«σΓΘΆ®Ιΐ ûΒ▩‘ΣΦΰΩ…“‘÷±Ϋ”ΫΎ Γ≥…±ΨΘ§“ρΈΣΗυΨίάύ–ΆΒΡ≤ΜΆ§Θ§Άβ≤Ω…δΤΒ¬Υ≤®ΤςΩ…Ρή±»ΫœΑΚΙσΓΘΝμΆβΘ§“Τ≥ΐ’β–©ΥπΚΡ–‘ΒΡΤςΦΰ”–÷ζ”Ύœϊ≥ΐ…δΤΒ‘ω“φΦΕΘ§ΫαΙϊ≤ΜΒΪΡήΫΎ Γ≥…±ΨΘ§Ά§ ±ΜΙΡήΫΒΒΆΙΠΚΡΓΔΧαΗΏœΏ–‘Ε»ΓΘΥυ”–’β–©ΕΦΩ…Ϋχ“Μ≤Ϋ‘ω«ΩΖ÷«χΚΆ÷«ΡήΦ·≥…ΒΡ”≈ ΤΓΘ

»γ«ΑΥυ ωΘ§≥…±ΨΒΡΙάΥψΖ«≥ΘΡ―Θ§“ρΈΣ’β‘ΎΚή¥σ≥ΧΕ»…œ»ΓΨω”Ύ≤ζΝΩΚΆ”κΙ©”Π…Χ«©Ε©ΒΡ–≠“ιΓΘ»ΜΕχΘ§œξœΗΖ÷Έωœ‘ ΨΘ§Ά®ΙΐΦ·≥…ΓΔœϊ≥ΐ≤ΩΖ÷‘ΣΦΰΓΔΫΒΒΆ“Σ«σΘ§Νψ÷–ΤΒΦήΙΙΉνΗΏΩ… ΙœΒΆ≥Ήή≥…±ΨΫΒΒΆ»ΐΖ÷÷°“ΜΓΘ–η“ΣΦ«ΉΓΒΡ «Θ§’β «œΒΆ≥≥…±ΨΘ§≤Μ «ΤςΦΰ≥…±ΨΓΘ”…”ΎΗϋ…ΌΒΡΤςΦΰ“Σ≥–‘ΊΗϋΕύΒΡΙΠΡήΘ§Υυ“‘‘ΎœΒΆ≥Ήή≥…±ΨΦθ…ΌΒΡ«ιΩωœ¬Θ§”––©ΤςΦΰ≥…±ΨΩ…ΡήΜα‘ωΦ”ΓΘ

≥ΐΝΥ≤ΡΝœ≥…±Ψ“‘ΆβΘ§Φ·≥… ΫΝψ÷–ΤΒΫ” ’ΤςΜΙ”–“Μ–©ΤδΥϊ”≈ ΤΓΘ”…”ΎΦ·≥… ΫœΒΆ≥Ω…“‘Φθ…ΌœΒΆ≥÷–ΒΡΤςΦΰ ΐΝΩΘ§Υυ“‘ΤδΉΑ≈δ≥…±ΨΫœΒΆΘ§ΙΛ≥ßΝΦΤΖ¬ ΫœΗΏΓΘ”…”ΎΖ÷ΝΔ ΫΤςΦΰ ΐΝΩ±δ…ΌΘ§Υυ“‘Ε‘Τκ ±Φδ“≤Μα±δΕΧΓΘ’β–©“ρΥΊœύΦ”Θ§Ω…ΫΒΒΆΙΛ≥ß≥…±ΨΓΘ

”…”ΎΝψ÷–ΤΒΫ” ’Τς «ΟϊΖϊΤδ ΒΒΡΩμ¥χΘ§Υυ“‘Θ§Βς’ϊΤΒΕΈΒΡΙΛ≥Χ≥…±Ψ“≤Φθ…ΌΝΥΓΘ‘Ύ÷–ΤΒ≤…―υœΒΆ≥÷–Θ§±Ί–κ…ς÷Ί―Γ‘ώ÷–ΤΒΤΒ¬ Θ§ΒΪΕ‘”ΎΝψ÷–ΤΒœΒΆ≥Θ§‘ρΈό–ηΫχ––Ϋς…ςΒΡΙφΜ°ΓΘΜυ±Ψ…œΆ®ΙΐΗϋΗΡ±Ψ’ώΨΆΩ…“‘ΧμΦ”–¬ΒΡΤΒΕΈΓΘΝμΆβΘ§”…”Ύ‘Ύ Ι”ΟΝψ÷–ΤΒ ±Θ§–μΕύ”Π”Ο≤Δ≤Μ“Σ«σΆβ≤Ω…δΤΒ¬Υ≤®ΤςΘ§Υυ“‘Θ§ΫαΙϊΩ…Ρή Βœ÷Ϋχ“Μ≤ΫΒΡΦρΜ·ΓΘ’ϊΧεΕχ―‘Θ§Ε‘”ΎΝψ÷–ΤΒΫβΨωΖΫΑΗΘ§»γΙϊΩΦ¬«÷±Ϋ”≥…±Ψ“‘ΦΑ…œΟφΝ–≥ωΒΡ÷Τ‘λ≥…±ΨΚΆΙΛ≥Χ≥…±ΨΘ§Τδ≥…±ΨΫΎ Γ”≈ Τ «Ζ«≥ΘΩ…ΙέΒΡΓΘ

ΉνΒΆΙΠΚΡ

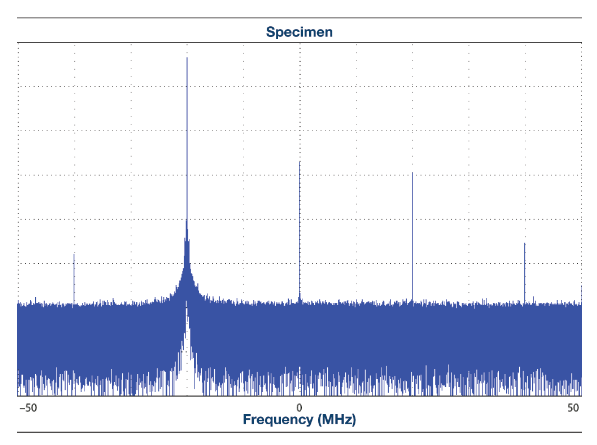

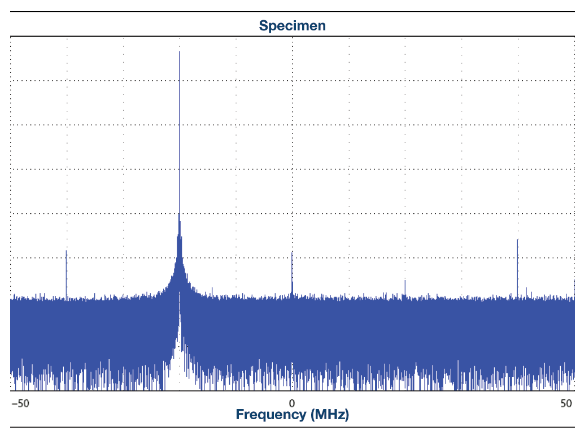

»γΙϊ÷Μ «≤…”ΟΆΦ1Υυ ΨΦήΙΙΘ§≤Δ÷±Ϋ”ΫΪΤδΦ·≥…ΒΫΤ§…œœΒΆ≥÷–Θ§ΫαΙϊ≤Δ≤ΜΜα¥χά¥ΙΠΚΡΚΆ≥…±Ψ…œΒΡ”≈ ΤΓΘ“ΣΫΎ ΓΙΠΚΡΘ§ΨΆ“Σ―Γ‘ώΗΏ–ßΒΡΦήΙΙΘ§ΗΟΦήΙΙΡή’κΕ‘ΡΩ±ξΙΛ“’Ϋχ––”≈Μ·ΓΘάύΥΤ”ΎΆΦ÷–Υυ Ψ÷–ΤΒ≤…―υΫ” ’ΤςΒΡΦήΙΙ…φΦΑΒΫ¥σΝΩΒΡΗΏΤΒΚΆ÷–ΤΒΤΒ¬ Θ§Ρ―“‘‘ΎΒΆ≥…±ΨΙΛ“’ΒΡΜυ¥Γ…œΫχ––ά©’ΙΘ§“ρ¥ΥΘ§“ΣœϊΚΡ¥σΝΩΙΠ¬ “‘÷ß≥÷Υυ–ηΤΒ¬ ΓΘ»ΜΕχΘ§»γΆΦ2Υυ ΨΒΡΝψ÷–ΤΒΦήΙΙΡήΝΔΦ¥ΫΒΒΆ÷Ν÷±ΝςΘ®Μυ¥χΘ©ΒΡΡΩ±ξΤΒ¬ Θ§“ρΕχΩ…“‘ Βœ÷ΤΒ¬ ΉνΒΆΒΡΒγ¬ΖΓΘ

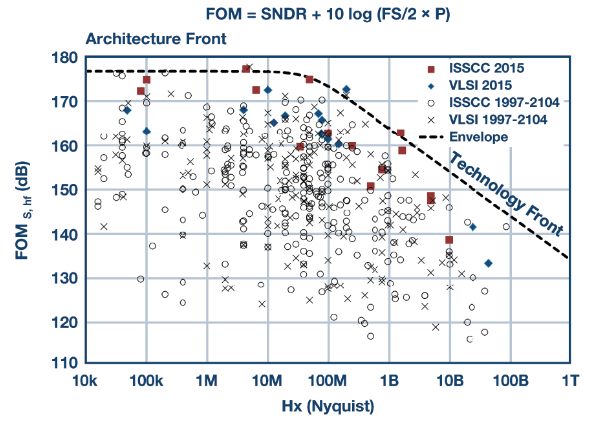

άύΥΤΒΊΘ§Ά®Ιΐ¥χΩμά¥ΫβΨω’βΗωΈ Χβ“≤ «Ζ«≥ΘΒΆ–ßΒΡΓΘάύΥΤ”Ύ÷±Ϋ”…δΤΒ≤…―υΒΡΦήΙΙΩ…ΧαΙ©ΫœΩμΒΡ¥χΩμΘ§≤Δ«“ΨΏ”–ΦΪ¥σΒΡΝιΜν–‘ΓΘ»ΜΕχΘ§ΨίWalden3

ΚΆMurmann.4‘ΎΈΡ÷–Υυ ωΘ§‘ωΦ”œΒΆ≥¥χΩμ Φ÷’ΕΦΜαΧαΗΏΙΠΚΡΓΘ

≥ΐΖ«–η“Σ‘≠ Φ¥χΩμΘ§Ζώ‘ρΘ§Ε‘Εύ ΐΫ” ’Τς”Π”Οά¥ΥΒΘ§ΫωΫωΆ®Ιΐ¥χΩμά¥ΫβΨω’βΗωΈ Χβ≤Δ≤Μ «“Μ÷÷Ψ≠ΦΟΒΡΫβΨωΖΫΑΗΓΘ’β–©≥ΛΤΎ―–ΨΩΒΡ ΐΨί±μΟςΘ§ΉΣΜΜΤςΒΡΖΔ’Ι”–ΝΫΗωΖΫΟφ÷ΒΒΟΙΊΉΔΓΘΦΦ θΟφ»ΓΒΟΝΥ“Μ–©Ϋχ≤ΫΘ§Ρή“‘Ε·Χ§ΖΕΈßΚΆ¥χΩμΒΡ–Έ Ϋœ‘÷χΧαΗΏΡΎΚΥΒΡΫΜΝς–‘ΡήΓΘΦήΙΙΟφ‘ΎΡΎΚΥΦήΙΙΒΡ’ϊΧε–߬ ΖΫΟφ”–ΥυΫχ≤ΫΓΘ“ΜΑψΒΊΘ§«ζœΏœ» «œρ”““ΤΕ·Θ§»ΜΚσΥφΉ≈…ηΦΤΒΡ”≈Μ·Θ§ΩΣ Φœρ…œ‘ΥΕ·ΓΘΕ‘”ΎΆ®–≈”Π”ΟΘ§≤ΌΉς«ςœρ―ΊΦΦ θΟφΫχ––Θ§Τδ÷–Θ§¥”œΏΧθ–±¬ ά¥Ω¥Θ§ΉΣΜΜΤς–߬ ¥σ‘Φœ¬ΫΒΝΥ10dB/ °±ΕΤΒ≥ΧΘ§»γΆΦ7Υυ ΨΓΘ‘Ύ¥Υ–±¬ œ¬Θ§ Ι¥χΩμ‘ωΦ”“Μ±ΕΜαΒΦ÷¬ΙΠΚΡ‘ωΦ”ΝΫ±ΕΓΘ»ΜΕχΘ§‘ΎΑ―’β–©ΡΎΚΥΦ·≥…ΒΫΙΠΡήΤςΦΰ÷–÷°ΚσΘ§–߬ ΨΆ”–ΥυΗΡ…ΤΘ§Β±ΤδΩΩΫϋΦήΙΙΟφ ±Θ§ΙΠ¬ Υπ ßΫ”Ϋϋ2ΓΘ

ΆΦ7.ΡΎΚΥADCΦΦ θΒΡΤΖ÷ “ρ ΐ4

Ε‘”ΎΙΊ–ΡΙΠΚΡΒΡ”Π”Οά¥ΥΒΘ§Ϋα¬έ «Θ§ΙΠΚΡΉνΒΆΒΡΫβΨωΖΫΑΗ «¥χΩμΚΆ≤…―υΥΌ¬ Ψυ’κΕ‘”Π”ΟΕχ”≈Μ·ΙΐΒΡΫβΨωΖΫΑΗΓΘ¥ν‘ΊΠ≤-ΠΛΉΣΜΜΤςΒΡΝψ÷–ΤΒ≤…―υ…ηΦΤΨΆ’κΕ‘’βάύ”Π”ΟΫχ––ΝΥ”≈Μ·ΓΘ“άΨίΨΏΧεΒΡ”Π”ΟΘ§≤…”ΟΝψ÷–ΤΒΫ” ’Τς±»÷–ΤΒ≤…―υΦήΙΙΩ…ΫΎ Γ50%Μρ“‘…œΒΡΙΠΚΡΘ§±»÷±Ϋ”…δΤΒ≤…―υΩ…ΫΎ ΓΗΏ¥ο120%ΒΡΙΠΚΡΓΘ

ΙΠΚΡΜΙ”κ≥…±Ψ÷±Ϋ”œύΙΊΓΘΗϋΗΏΒΡΙΠΚΡ≤ΜΒΪΜαΧαΗΏΖβΉΑ≥…±ΨΚΆΒγ‘¥≥…±ΨΘ§Εχ«“Ε‘”ΎΒγ¬ΖœϊΚΡΒΡΟΩΆΏΧΊΙΠ¬ Θ®…ηΒγΖ―ΈΣ12ΟάΖ÷/«ßΆΏ ±Θ©Θ§ΟΩΡξΟΩΆΏΧΊΒΡ‘Υ”Σ≥…±ΨΜα≥§Ιΐ1Οά‘ΣΓΘΦχ”Ύ–μΕύΒγΉ”ΤςΦΰ≥…±ΨΫœΒΆΘ§Τδ“ΜΡξΒΡ‘Υ––≥…±ΨΨΆΩ…Ρή«αΥ…≥§ΙΐΤδ÷±Ϋ”≥…±ΨΓΘ“ρ¥ΥΘ§ΥφΉ≈Φ·≥… ΫΈόœΏΒγΫβΨωΖΫΑΗ―ΓœνΒΡΆΤ≥ωΘ§Ε‘≥…±ΨΚΆΙΠΚΡΟτΗ–ΒΡ”Π”Ο±Ί–κ―Γ‘ώΫς…ςΒΊΉω≥ω»®ΚβΓΘ―Γ‘ώΜα≤Μ±Ί“ΣΒΊ‘ωΦ”ΙΠΚΡΒΡΦήΙΙΘ§ΫαΙϊ≤ΜΒΪΜα‘ωΦ”ΙΠΚΡΘ§ΜΙΩ…ΡήΜα”ΑœλΫβΨωΖΫΑΗΒΡ≥ΛΤΎ‘Υ––≥…±ΨΓΘ

–‘Ρή‘ω«Ω

ΈόœΏΒγ…ηΦΤ”–»τΗ…÷Ί“ΣΒΡΙΊΦϋ÷Η±ξ–η“ΣΉΔ“βΓΘΤδ÷–Αϋά®‘κ…υœΒ ΐ(NF)ΓΔœΏ–‘Ε»Θ®IP3ΓΔIM3Θ©ΓΔΫΒΟτΓΔ―Γ‘ώ–‘Β»ΓΘ‘Ύ’ΐ≥ΘΒΡΈόœΏΒγΙφΗώ“‘ΆβΘ§ΜΙ”–“Μ–©ΙφΗώ“≤Κή÷Ί“ΣΘ§ΒΪ”ΟΜßΆυΆυΩ¥≤ΜΒΫΓΘΤδ÷–Αϋά®ΙφΗώΖ÷≤ΦΚΆΤ·“Τ”κ ±ΦδΓΔΒγ‘¥ΓΔΈ¬Ε»ΚΆΝς≥ΧΒΡΙΊœΒΓΘΝψ÷–ΤΒΦήΙΙΖϊΚœΙΊ”ΎΈόœΏΒγ…ηΦΤΒΡ’β–©ΚΆΤδΥϊΙΊΦϋ“Σ«σΓΘ

Ά®ΙΐΈ¬Ε»ΓΔΒγ‘¥ΚΆΝς≥ΧΗζΉΌ

»ΪΦ·≥… Ϋ ’ΖΔΤςΦήΙΙΒΡ“ΜΗω”≈ Τ «Θ§Ε‘”Ύ…ηΦΤΚœάμΒΡΈόœΏΒγΘ§ΤςΦΰΤΞ≈δΩ…Ρή“ΣΚΟΒΟΕύΘ§≤ΜΫω‘ΎΤπ≥θ «’β―υΘ§Εχ«“»γΙϊ…ηΦΤΚœάμΘ§ΤςΦΰΩ…“‘”––ßΒΊΫχ––Νς≥ΧΓΔΈ¬Ε»ΓΔΒγ‘¥ΚΆΤΒ¬ ΗζΉΌΓΘ‘Υ”ΟΆ®≥Θ«Ε»κ’β–©Φ·≥…ΫβΨωΖΫΑΗ÷–ΒΡ–≈Κ≈¥ΠάμΦΦ θΘ§Ω…“‘ΫœΚΟΒΊœϊ≥ΐ»ΈΚΈ≤–”ύΒΡ ß≈δΈ ΧβΓΘΥδ»ΜΕ‘IC…ηΦΤά¥ΥΒΘ§’β «Ζ«≥ΘΒδ–ΆΒΡ«ιΩωΘ§ΒΪ «Θ§ΈόœΏΒγΦ·≥…ΒΡ≤ΜΆ§÷°¥Π‘Ύ”ΎΘ§‘ΎΝψ÷–ΤΒ…ηΦΤ÷–Θ§”…”Ύ“άάΒ”ΎΤΒ¬ ΒΡΥυ”–œνΨυ≤Ω π”ΎΤ§…œΘ§Υυ“‘Θ§’β–©œν“≤Ω…“‘ Βœ÷ΗζΉΌΙΠΡήΓΘ»γΆΦ1Υυ ΨΒΡΒδ–ΆΈόœΏΒγΑϋά®“ΜΗωΤ§Άβ÷–ΤΒ¬Υ≤®ΤςΓΘΗΟ÷–ΤΒ¬Υ≤®ΤςΒΡΧΊ–‘ΜαΥφ ±ΦδΓΔΈ¬Ε»ΜρΤςΦΰΕχ±δΜ·Θ§”κΤ§…œΒΡ»ΈΚΈ‘ΣΥΊΨυΈόΙΊΘ§≤Δ«“≤ΜΡήΕ‘ΤδΫχ––ΗζΉΌΓΘ»ΜΕχΘ§Φ·≥…¬Υ≤®ΤςΒΡ“ΜΗω÷ς“Σ”≈ Τ «Θ§“ρΈΣΤδ“‘Τ§…œΤςΦΰΙΙΫ®Θ§Υυ“‘Θ§ΤςΦΰ «Ω…“‘ά©’ΙΒΡΘ§Μρ’ΏΩ…“‘Α¥±»άΐœύΜΞΗζΉΌΘ§“‘±Θ≥÷–‘ΡήΈ»Ε®ΓΘΕ‘”ΎΡ«–©≤ΜΡήΆ®Ιΐ…ηΦΤΈ»Ε®ΒΡœνΘ§Ω…“‘«αΥ…Ϋχ–––ΘΉΦΓΘΉν÷’ΫαΙϊ «Θ§‘Ύ‘ΛΦΤΤςΦΰ≤ν“λ ±Θ§Υυ–η“ΣΒΡ‘ΘΝΩ“Σ‘Ε‘ΕΒΆ”ΎΥυ”–ΤςΦΰΨυΈόΙΊΒΡΖ÷ΝΔ Ϋ…ηΦΤΓΘ

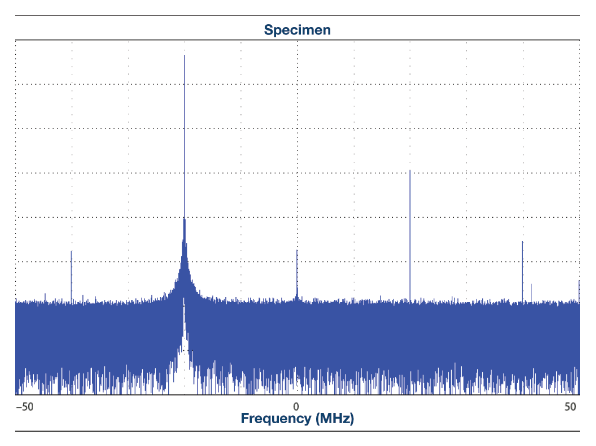

άΐ»γΘ§ΈΣΜλΤΒΤςΓΔ÷–ΤΒ¬Υ≤®ΤςΓΔ÷–ΤΒΖ≈¥σΤςΚΆADCΗςΖ÷≈δ1dBΒΡ‘κ…υœΒ ΐΘ§’β÷÷ΉωΖ®≤Δ≤ΜΚ±ΦϊΓΘ‘Ύ÷ΤΕ®–‘Ρή‘ΛΥψ ±Θ§±Ί–κΑ―’β–©≤ν“λΦΕΝΣΤπά¥ΓΘ»ΜΕχΘ§‘ΎΦ·≥… Ϋ…ηΦΤ÷–Θ§Υυ”–ΙΊΦϋΦΦ θΙφΗώ“ΣΟ¥œύΜΞΗζΉΌΘ§“ΣΟ¥Ά®Ιΐ–ΘΉΦ”η“‘≈≈≥ΐΘ§ΫαΙϊΩ… Βœ÷1dBΒΡΒΞ“ΜΤςΦΰ≤ν“λΘ§ΦΪ¥σΒΊΦρΜ·ΝΥ–≈Κ≈Ν¥≤ν“λΓΘœύ±»Ηςœν≤ΜœύΙΊΒΡ…ηΦΤΘ§’βΩ…ΡήΜαΕ‘…ηΦΤ‘λ≥…÷Ί“ΣΒΡ”ΑœλΘΜ‘ΎΗςœν≤ΜœύΙΊΒΡ…ηΦΤ÷–Θ§–η“ΣΕνΆβΒΡœΒΆ≥‘ω“φά¥Β÷œζΩ…ΡήΜα‘ωΦ”ΒΡ‘κ…υΓΣΜα”ΑœλΒΫΉν÷’≤ζΤΖΒΡ≥…±ΨΓΔΙΠΚΡΚΆœΏ–‘Ε»ΓΘ‘Ύ»γΆΦ2Υυ ΨΒΡΦ·≥… Ϋ…ηΦΤ÷–Θ§–‘ΡήΉή≤ν“λ“Σ‘Ε‘Ε–Γ”Ύ≤ΜœύΙΊ…ηΦΤΘ§“ρ¥ΥΘ§÷Μ–ηΫœ–ΓΒΡœΒΆ≥‘ω“φΓΘ

ΗΏΦΕ–Θ’ΐΦΦ θ

‘ΎΙΐ»ΞΘ§Νψ÷–ΤΒΫ” ’ΤςΆ®≥Θ”–ΝΫΗωΝλ”ρΜα“ΐΤπ»ΥΟ«ΒΡΒΘ”«ΓΘ”…”ΎΗ¥Κœ ΐΨί «”Ο“ΜΕ‘±μ Ψ Β≤ΩΚΆ–ι≤ΩΒΡ Β ΐΦΕΝΣΆχ¬γ…ζ≥…ΚΆ±μ ΨΒΡΘ§ΫαΙϊΨΆ≤ζ…ζΝΥΩ…Ρή±μ ΨΗς–≈Κ≈Ν¥‘ω“φΓΔœύΈΜΚΆ ßΒςΒΡΈσ≤νΘ§»γΆΦ8Υυ ΨΓΘ

ΆΦ8.±μ Ψ‘ω“φΓΔœύΈΜΚΆ ßΒςœνΒΡ’ΐΫΜΈσ≤ν

’β–©Έσ≤ν‘ΎΤΒΤΉ÷–±μœ÷ΈΣΨΒœώΘ§“≤ «ΖΝΑ≠’β–©ΦήΙΙΙψΖΚΤ’ΦΑΒΡ÷ς“Σ‘≠“ρΓΘ»ΜΕχΘ§ΉςΈΣ“Μ÷÷Φ·≥… ΫΫβΨωΖΫΑΗΘ§Ά®ΙΐΡΘΡβ”≈Μ·ΚΆ ΐΉ÷–Θ’ΐΦΦ θΘ§Ω…“‘«αΥ…ΩΊ÷Τ’β–©ΨΒœώΓΘΆΦ9Υυ ΨΈΣΒδ–ΆΒΡΈ¥Ψ≠–Θ’ΐΒΡΗ¥Κœ ΐΨί±μ ΨΖΫ ΫΓΘ‘ΎΆΦ÷–Ω…“‘Ω¥ΒΫLO–Ι¬©Θ®ΚΆ÷±Νς ßΒςΘ©ΦΑΨΒœώ“÷÷ΤΘ®’ΐΫΜΈσ≤νΘ©ΓΘ

ΆΦ9.Βδ–ΆΒΡΈ¥Ψ≠–Θ’ΐΒΡLO–Ι¬©ΚΆΨΒœώ“÷÷Τ

LO–Ι¬©ΩΊ÷Τ

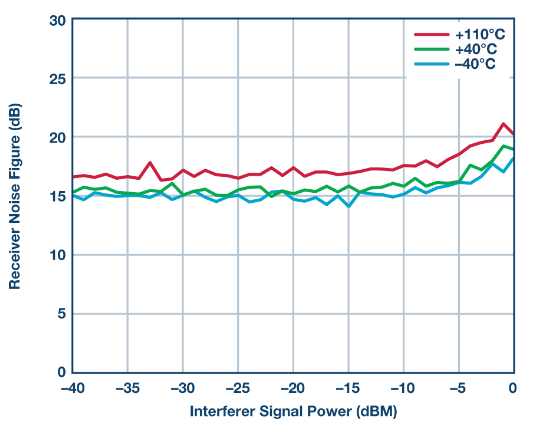

LO–Ι¬©‘ΎIΜρQ–≈Κ≈¬ΖΨΕ÷–±μœ÷ΈΣ‘ω¥σΒΡ÷±Νς ßΒςΓΘΤδ‘≠“ρ «LO÷±Ϋ”ώνΚœ÷Ν…δΤΒ–≈Κ≈¬ΖΨΕ÷–Θ§≤Δ±Μ“‘œύΗ…ΖΫ Ϋœ¬±δΤΒ÷Ν δ≥ωΓΘΫαΙϊ≤ζ…ζΜλΤΒΤςΜΐΘ§±μœ÷ΈΣ÷±Νς ßΒςΘ§Φ”»κ–≈Κ≈Ν¥άο¥φ‘ΎΒΡ»ΈΚΈ≤–”ύ÷±Νς ßΒς÷–ΓΘ”≈–ψΒΡΝψ÷–ΤΒΦήΙΙ≤ΜΒΪΜα‘Ύ≥θ Φ ±Ή‘Ε·ΗζΉΌ≤Δ–Θ’ΐ’β–©Έσ≤νΘ§ΜΙΡήΥφ ±ΦδΓΔΈ¬Ε»ΓΔΒγ‘¥ΚΆΝς≥ΧΉ‘Ε·ΗζΉΌΚΆ–Θ’ΐΘ§ΫαΙϊΩ… Βœ÷”≈”Ύ®C90dBFSΒΡ–‘ΡήΥ°ΤΫΘ§»γΆΦ10Υυ ΨΓΘ

ΆΦ10.Βδ–ΆΒΡLO–Ι¬©ΩΊ÷Τ

QEC

ΈΣΝΥΖά÷ΙΨΒœώ»≈¬“–‘ΡήΘ§“ΜΑψΜα≤…”Ο’ΐΫΜΈσ≤ν–Θ’ΐ(QEC)ΦΦ θΓΘΆΦ11’Ι ΨΝΥ’β÷÷ΙΠΡήΩ…Ρή≤ζ…ζΒΡ”ΑœλΓΘ‘Ύ¥Υάΐ÷–Θ§ΨΒœώΗΡ…Τ÷Ν”≈”Ύ®C105dBcΒΡΥ°ΤΫΘ§≥§ΙΐΝΥΕύ ΐΈόœΏ”Π”ΟΒΡ“Σ«σΓΘΕ‘”ΎLO–Ι¬©ΚΆQECΘ§‘Υ”ΟΗζΉΌΙΠΡή «ΈΣΝΥ»Ζ±Θ‘Ύ–‘ΡήΥφ ±ΦδΕχ±δΜ· ±Θ§–Θ’ΐΡή±Θ≥÷Ήν–¬Ή¥Χ§Θ§¥”Εχ±Θ÷ΛΡή Φ÷’ Βœ÷ΉνΦ―–‘ΡήΓΘ

ΆΦ11.LO–Ι¬©ΩΊ÷ΤΧθΦΰœ¬ΒΡΒδ–Ά’ΐΫΜ–Θ’ΐ

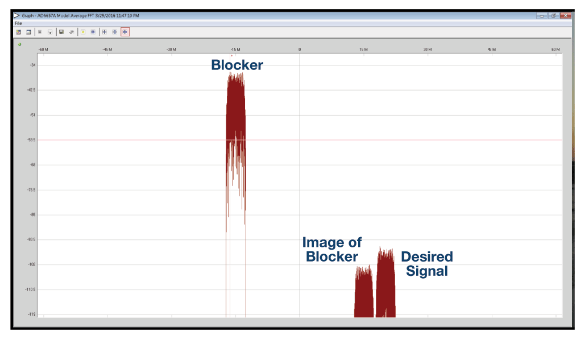

‘ΎΈόœΏΒγœΒΆ≥÷–Θ§’ΐΫΜΈσ≤νΚΆLOάΓΆ®Ζ«≥Θ÷Ί“ΣΓΘ»γΙϊΈσ≤νΉψΙΜ¥σΘ§Ϋœ¥σΒΡΉη≤®ΤςΨΒœώ”–Ω…ΡήΜαΤΝ±ΈΒτΫœ–ΓΒΡΡΩ±ξ–≈Κ≈ΓΘ‘ΎΆΦ12÷–Θ§“ΜΗω¥σΉη≤®ΤςΒΡΨΒœώ≥ωœ÷‘Ύ15MHz¥ΠΘ§Ά§ ±Θ§“ΜΗωΡΩ±ξ–≈Κ≈ΒΡ÷––ΡΈΜ”Ύ20MHzΓΘ»γΙϊΨΒœώ≤ΩΖ÷Μρ»Ϊ≤Ω¬δ‘ΎΡΩ±ξ–≈Κ≈…œΘ§‘ρΜαΒΦ÷¬ΡΩ±ξ–≈Κ≈SNRœ¬ΫΒΘ§ΫαΙϊΩ…Ρή‘ΎΫβΒςΙΠΡήάο‘λ≥…Έσ≤νΓΘ“ΜΑψΒΊΘ§LTEΓΔW-CDMAΒ»œΒΆ≥ΕΦ’κΕ‘’βάύΨΒœώ…η÷ΟΝΥΚœάμΒΡ»ί≤νΘ§ΒΪ≤ΔΖ«Άξ»Ϊ≤Μ ή”ΑœλΓΘ“ΜΑψ«ιΩωœ¬Θ§’β–©œΒΆ≥“Σ«σ75dBcΜρΗϋΚΟΒΡΨΒœώ“÷÷Τ–‘ΡήΘ§»γΆΦ11Υυ ΨΘ§‘Υ”ΟΝψ÷–ΤΒΦήΙΙΩ…“‘«αΥ…¥οΒΫ≤ΔΈ§≥÷’β“Μ“Σ«σΓΘ

ΆΦ12.ΨΒœώΉηΑ≠ΡΩ±ξ–≈Κ≈ΒΡ Ψάΐ

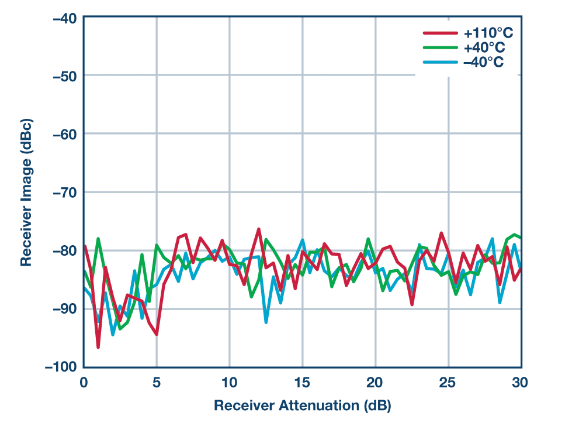

“‘…œΈ“Ο«Ϋι…ήΝΥΝψ÷–ΤΒΒΡ÷νΕύ”≈ ΤΘ§Ϋ”œ¬ά¥Ϋι…ήΝψ÷–ΤΒ‘Ύ”Π”ΟΖΫΟφΒΡ–‘Ρή»γΚΈΓΘ

Νψ÷–ΤΒΖΔ…δΚΆΫ” ’ΒΡ“ΜΗωΒδ–Ά Ψάΐ « AD9371ΓΣΓΣ

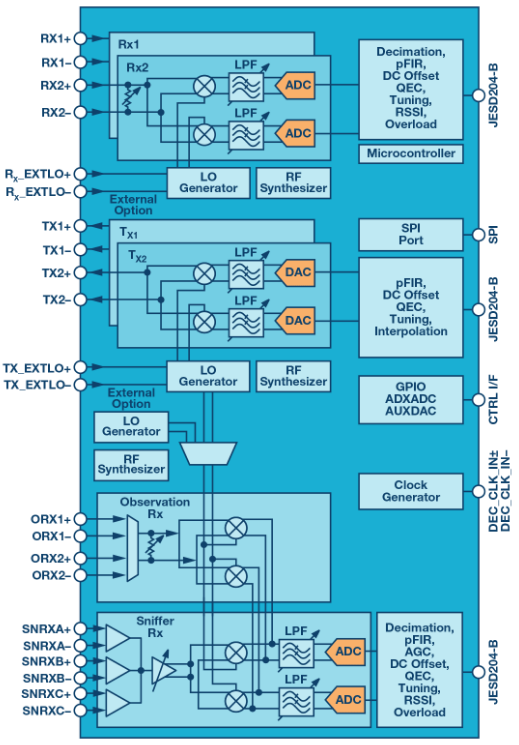

»γΆΦ13Υυ ΨΘ§AD9371ΨΏ”–ΦΪΗΏΒΡΙΠΡήΦ·≥…Ε»Θ§Φ·≥…ΝΥΥΪΖΔ…δΓΔΥΪΫ” ’“‘ΦΑΕύ÷÷ΕνΆβΒΡΙΠΡήΘ§Αϋά®Ιέ≤λΚΆ–αΧΫΫ” ’ΤςΓΔΦ·≥… ΫAGCΓΔ÷±Νς ßΒς–Θ’ΐΘ®LO–Ι¬©ΩΊ÷ΤΘ©ΓΔQECΒ»ΓΘΗΟ≤ζΤΖΨΏ”–ΫœΩμΒΡ…δΤΒΗ≤Η«ΖΕΈßΘ§¥”300MHz÷Ν6GHzΓΘΟΩΗωΖΔ…δΤςΨυΩ…Η≤Η«20MHz÷Ν100MHzΒΡΚœ≥…¥χΩμΘ§ΕχΟΩΗωΫ” ’Τς‘ρΡήΗ≤Η«5MHz÷Ν100MHzΒΡ¥χΩμΓΘΥδ»Μ¥ΥΤςΦΰΟιΉΦΒΡ «3GΚΆ4G”Π”ΟΘ§ΒΪ“≤ «≤Μ≥§Ιΐ6GHzΒΡ–μΕύΤδΥϊΆ®”ΟΈόœΏΒγΚΆ»μΦΰΕ®“ε”Π”ΟΒΡάμœκΫβΨωΖΫΑΗΓΘ

ΆΦ13.AD9371Φ·≥… ΫΝψ÷–ΤΒ ’ΖΔΤς

AD9371‘Ύ12mmΓΝ12mmΒΡBGAΖβΉΑάοΦ·≥…ΝΥΆξ’ϊΒΡœΒΆ≥ΙΠΡήΘ§Αϋά®«ΑΟφΧ÷¬έΙΐΒΡ“άάΒ”ΎΤΒ¬ ΒΡΥυ”–ΤςΦΰΘ§“‘ΦΑΥυ”––ΘΉΦΚΆΕ‘ΤκΙΠΡήΓΘ‘ΎΆΦ4Υυ ΨΫ” ’ΙΠΡήΒΡΜυ¥Γ…œΘ§ΆΦ14‘ωΦ”ΝΥ±Ί“ΣΒΡΖΔ…δΙΠΡήΘ§‘λΨΆΝΥ“Μ÷÷Ζ«≥ΘΫτ¥’ΒΡΥΪ ’ΖΔΤς…ηΦΤΓΘΙΠΚΡ»ΓΨω”Ύ»Ζ«–ΒΡ≈δ÷ΟΘ§Αϋά®¥χΩμΚΆ Βœ÷ΒΡΙΠΡήΘ§ΒΪ «Θ§AD9371ΒΡΒδ–ΆΙΠΚΡΫωΈΣ4.86WΘ§Αϋά®Έ§≥÷LO–Ι¬©ΚΆΨΒœώ“÷÷ΤΒΡ ΐΉ÷ΙΠΡήΓΘ

ΆΦ14.Νψ÷–ΤΒ ’ΖΔΤςΒΡΒδ–Ά≤ΦΨ÷

AD9371ΒΡΙΊΦϋ–‘Ρή÷Η±ξ

‘κ…υœΒ ΐ

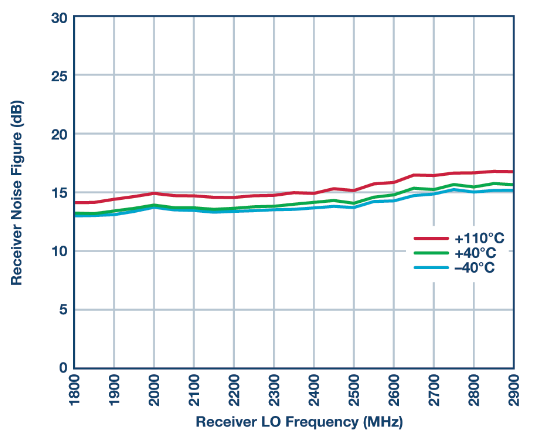

ΆΦ15ΚΆΆΦ16’Ι ΨΝΥAD9371ΒΡΒδ–Ά‘κ…υœΒ ΐΧΊ–‘ΓΘΒΎ“Μ’≈ΆΦ’Ι ΨΝΥΫœΩμΒΡ…δΤΒΤΒ¬ Θ§‘ΎΗΟΤΒΤΉ÷–Θ§‘κ…υœΒ ΐœύΕ‘ΤΫΧΙΓΘΗΟΤςΦΰΒΡ δ»κΫαΙΙ≤…”ΟΥΞΦθΤςΒΡ–Έ ΫΘ§“ρ¥ΥΘ§Ε‘”ΎΟΩdBΘ§‘κ…υœΒ ΐ‘ωΦ”1dBΓΘΦΌ…ηΉν≤νΧθΦΰ‘κ…υœΒ ΐΈΣ16dBΘ§ΥΞΦθΈΣΝψΘ§Άβ≤Ω‘ω“φ≤ν“λ‘ –μ‘Φ4dBΒΡΥΞΦθΘ§‘ρΩ…ΦΌ…ηΉή‘κ…υœΒ ΐΈΣ20dBΓΘΕ‘”Ύ“ΜΗωΧαΙ©÷Ν…Ό24dB‘ω“φΒΡΆβ≤ΩLNA(0.8dB)Θ§œΒΆ≥‘κ…υœΒ ΐΈΣ2dBΓΘ

ΆΦ15.AD9371‘κ…υœΒ ΐΘ®0dBΥΞΦθΚΆ40MHz¥χΩμΘ©

‘ΎΆΦ16÷–Θ§‘κ…υœΒ ΐΈΣ¥χΆβΉη»ϊœύΕ‘”ΎAD9371 δ»κΒΡΚ· ΐΓΘ…ηΆβ≤Ω‘ω“φΈΣ24dBΘ§‘ΎœύΕ‘”ΎΧλœΏΝ§Ϋ”Τς®C24dBm¥ΠΘ§ΜαœύΕ‘”ΎΗΟΤςΦΰ δ»κ≥ωœ÷0dBmΓΘ»γΙϊ÷ΜΩΦ¬«AD9371ΒΡ”ΑœλΘ§»τΦ·≥…Ϋ” ’Τςœ¬ΫΒ3dBΘ§‘ρ‘κ…υœΒ ΐΒΡΉήΧεœ¬ΫΒΖυΕ»‘ΦΈΣ1dBΓΘ

ΆΦ16.AD9371NF”κ¥χΆβ–≈Κ≈ΙΠ¬ ΒΡΙΊœΒ

ΨΒœώ“÷÷Τ

”κLO–Ι¬©άύΥΤΘ§Ϋ” ’ΨΒœώ“÷÷ΤΩ…Μυ”ΎΆΦ17Υυ Ψ–≈œΔΫχ––ΙάΥψΓΘΒ±ΧλœΏΕΥΒΡΒδ–Ά δ»κΒγΤΫΈΣ®C40dBm ±Θ§‘ρΩ…“‘ΙάΥψ≥ωΘ§ΨΒœώ“Σ”≈”Ύ±»ΧλœΏΕΥΩΎΒΆ80dBΜρ®C120dBmΒΡΥ°ΤΫΓΘ

ΆΦ17.Ϋ” ’ΤςΨΒœώ“÷÷Τ

|