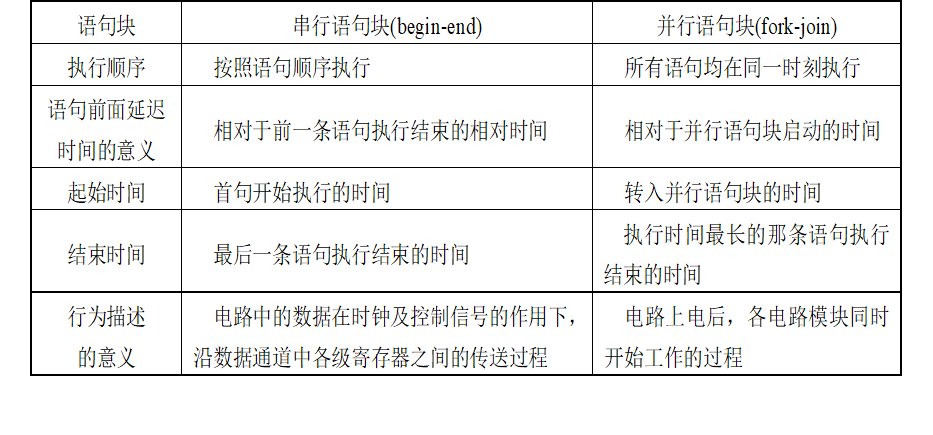

| ±ύΦ≠ΆΤΦω: |

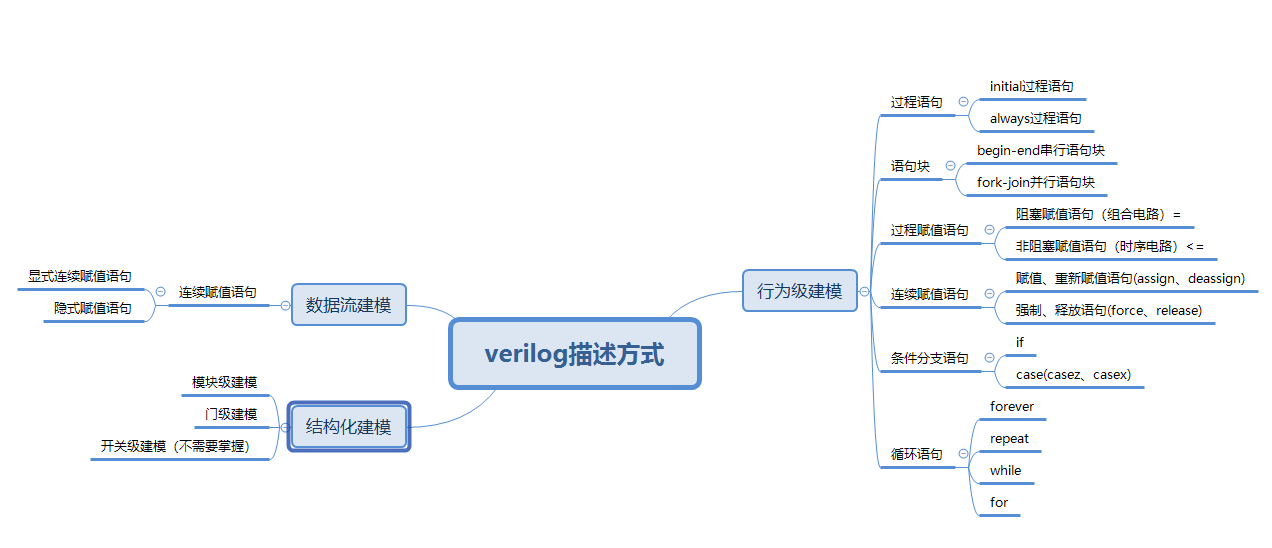

±ΨΈΡ÷ς“ΣΫι…ήVerilog

HDL»ΐ÷÷Οη ωΖΫ ΫΘ§Ζ÷±π « ΐΨίΝςΫ®ΡΘΖΫ ΫΘ§––ΈΣΦΕΫ®ΡΘΖΫ Ϋ“‘ΦΑΫαΙΙΜ·Ϋ®ΡΘΖΫ ΫΘ§œΘΆϊΕ‘ΡζΒΡ―ßœΑ”–ΥυΑο÷ζΓΘ

±ΨΈΡά¥Ή‘”ΎCSDNΘ§”…ΜπΝζΙϊ»μΦΰAlice±ύΦ≠ΓΔΆΤΦωΓΘ |

|

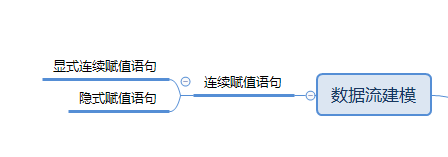

“Μ. ΐΨίΝςΫ®ΡΘΖΫ Ϋ

‘ΎΉιΚœ¬ΏΦ≠Βγ¬Ζ÷–Θ§ ΐΨί≤ΜΜα¥φ¥ΔΘ§“ρ¥Υ δ»κ–≈Κ≈Ψ≠ΙΐΒγ¬Ζ±δΈΣ δ≥ω–≈Κ≈άύΥΤ”Ύ ΐΨίΝςΕ·ΓΘΩ…“‘Ά®ΙΐΝ§–χΗ≥÷Β”οΨδ’β÷÷ΧΊ–‘Ϋχ––Ϋ®ΡΘΘ§’β÷÷Ϋ®ΡΘΖΫ ΫΆ®≥Θ±Μ≥ΤΈΣ ΐΨίΝςΫ®ΡΘΓΘ

Ν§–χΗ≥÷Β”οΨδ÷ΜΡή”Οά¥Ε‘Ν§œΏ–Ά±δΝΩΫχ––«ΐΕ·Θ§ΥϋΩ…“‘≤…»Γœ‘ ΫΝ§–χΗ≥÷Β”οΨδΚΆ“ΰ ΫΝ§–χΗ≥÷Β”οΨδΝΫ÷÷Η≥÷ΒΖΫ ΫΓΘ

1.œ‘ ΫΝ§–χΗ≥÷Β”οΨδ

”…ΝΫΧθ”οΨδΙΙ≥…ΘΚ

Ηώ ΫΘΚ

<Ν§–χ–Ά±δΝΩάύ–Ά><ΈΜΩμ><±δΝΩΟϊ>; // Ε‘Ν§œΏ–Ά±δΝΩΫχ––άύ–ΆΥΒΟς

assign #<―”≥Ό><±δΝΩΟϊ>=Η≥÷Β”οΨδΘΜ // Ε‘’βΗωΝ§œΏ–Ά±δΝΩΫχ––Ν§–χΗ≥÷ΒΒΡΗ≥÷Β”οΨδ

2.“ΰ ΫΝ§–χΗ≥÷Β”οΨδ

Ηώ ΫΘΚ

<Ν§–χ–Ά±δΝΩάύ–Ά><Η≥÷Β«ΐΕ·«ΩΕ»><ΈΜΩμ>#<―”≥Ό><±δΝΩΟϊ>=Η≥÷Β”οΨδΘΜ

ΉΔ“βΘΚ

a. Ν§–χ–Ά±δΝΩάύ–ΆΡ§»œΈΣwireΘΜ

b.ΈΜΩμΡ§»œ1ΈΜΘΜ

c.«ΐΕ·«ΩΕ»÷Μ¥φ‘Ύ”Ύ“ΰ ΫΝ§–χΗ≥÷Β”οΨδΘ§Ρ§»œΘ®strong1Θ§strong0Θ©Θ§»τΝΫΗω«ΐΕ·«ΩΕ»“‘ΗΏ«ΐΕ·ΈΣ÷ςΘΜ

d.―”≥Ό#(delay1Θ§delay2Θ§delay3)Ζ÷±πΈΣ…œ…ΐ―ΊΘ§œ¬ΫΒ―ΊΘ§±δΈΣΗΏΉηΧ§ΒΡ―”≥ΌΘΜ

e.Ν§–χΗ≥÷Β”οΨδ≤ΜΡή≥ωœ÷‘ΎΙΐ≥ΧΩιάοΓΘ

f.ΕύΗωΝ§–χΗ≥÷Β”οΨδ÷°Φδ «≤Δ––ΙΊœΒΘ§“ρ¥Υ”κΈΜ÷ΟΥ≥–ρΈόΙΊΓΘ

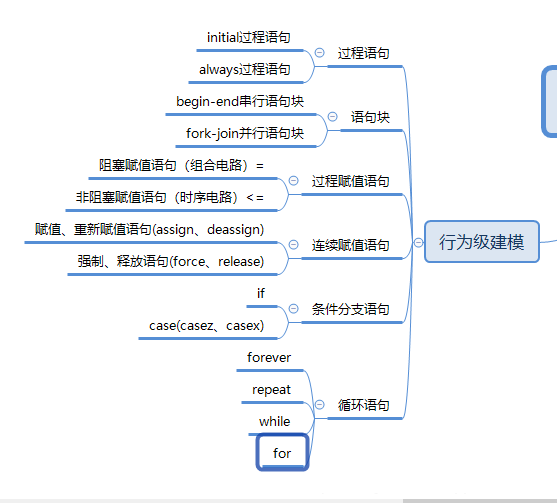

Εΰ.––ΈΣΦΕΫ®ΡΘ

¥”Βγ¬ΖΆβ≤Ω––ΈΣΒΡΫ«Ε»Ε‘ΤδΫχ––Οη ωΘ§“ρ¥Υ––ΈΣΦΕΫ®ΡΘ «¥”“ΜΗω≤ψ¥ΈΚήΗΏΒΡ≥ιœσΫ«Ε»ά¥±μ ΨΒγ¬ΖΒΡΓΘ––ΈΣΫ®ΡΘ“≤Ω…“‘”Οά¥…ζ≥…Ζ¬’φ≤β ‘–≈Κ≈ΓΘ

2.1 Ιΐ≥Χ”οΨδ

2.1.1Θ°initialΙΐ≥Χ”οΨδ initialΙΐ≥Χ”οΨδΒΡ”οΖ®Ηώ ΫΈΣΘΚ

initial

begin

”οΨδ1ΘΜ

”οΨδ2ΘΜ

Θ°Θ°Θ°

ΓΓΓΓ ”οΨδnΘΜ

ΓΓΓΓ end |

a.Ά®≥Θ”Ο”ΎΖ¬’φΡΘΩι÷–Ε‘ΦΛάχœρΝΩΟη ωΘ§Μρ”Ο”ΎΗχΦΡ¥φΤς±δΝΩΗ≥≥θ÷ΒΓΘ

b.Ζ¬’φ ±¥”ΡΘΡβ0 ±ΩΧΩΣ Φ÷¥––Θ§Εχ«“÷Μ÷¥––“Μ¥ΈΓΘ

c.»τΕύΗωinitialΙΐ≥ΧΩιΘ§‘ρΆ§ ±¥”0 ±ΩΧΩΣ Φ≤Δ––÷¥––ΒΡΓΘ

2.1.2Θ°alwaysΙΐ≥Χ”οΨδ

”οΖ®Ηώ Ϋ «ΘΚ always@(<ΟτΗ– ¬ΦΰΝ–±μ>) ”οΨδΩι;

a.œύΕ‘”ΎinitialΙΐ≥Χ”οΨδΘ§alwaysΙΐ≥Χ”οΨδ÷Μ“Σ¬ζΉψalwaysΚσΟφΒΡΟτΗ– ¬ΦΰΝ–±μΘ§ΨΆ÷¥––”οΨδΩιΓΘ

b.posedgeΚΆnegedgeΟη ω–≈Κ≈ΒΡ…œ…ΐ―ΊΚΆœ¬ΫΒ―ΊΓΘ

ΉΔ“β;

a.‘ΎΙΐ≥Χ”οΨδ(initialΚΆalways)÷–Θ§±ΜΗ≥÷Β–≈Κ≈±Ί–κΕ®“εΈΣΓΑregΓ±άύ–ΆΓΘ

b.ΉιΚœΒγ¬ΖΫχ––Οη ω ±Θ§–η“ΣΑ―»Ϊ≤ΩΒΡ δ»κ–≈Κ≈Ν–»κΟτΗ––≈Κ≈Ν–±μ

c. ±–ρΒγ¬ΖΫχ––Οη ω ±Θ§–η“ΣΑ― ±Φδ–≈Κ≈ΚΆ≤ΩΖ÷ δ»κ–≈Κ≈Ν–»κΟτΗ––≈Κ≈Ν–±μΓΘ

2.2 ”οΨδΩι

Β±”οΨδ ΐ≥§Ιΐ“ΜΧθ ±Θ§–η“Σ≤…”Ο”οΨδΩιΓΘ

”οΨδΩι”…Ωι±ξ ΕΖϊbegin-endΜρfork-joinΫγΕ®ΒΡ“ΜΉι––ΈΣΟη ω”οΨδΓΘ

2.2.1. ¥°––”οΨδΩι

begin-endΘ§Ω…“‘”Ο”ΎΩ…ΉέΚœΒγ¬Ζ≥Χ–ρΚΆΖ¬’φ≤β ‘≥Χ–ρΓΘ

a. ¥°––”οΨδΩι÷–ΒΡΟΩΧθ”οΨδ÷πΧθ÷¥––ΓΘ―”≥Ό ±ΦδœύΕ‘”Ύ«Α“ΜΧθ”οΨδ÷¥––Ϋα χ ±ΦδΓΘ

b. ¥°––”οΨδΩιΒΡΤπ Φ÷¥–– ±ΦδΨΆ «¥°––”οΨδΩι÷–ΒΎ“ΜΧθ”οΨδΩΣ Φ÷¥––ΒΡ ±ΦδΘΜ¥°––”οΨδΩιΒΡΫα χ ±ΦδΨΆ «Ωι÷–ΉνΚσ“ΜΧθ”οΨδ÷¥––Ϋα χΒΡ ±ΦδΓΘ

2.2.2. ≤Δ––”οΨδΩι

fork--join,÷ΜΡή”Ο”ΎΖ¬’φ≤β ‘≥Χ–ρ

≤Δ––”οΨδΩιΒΡΧΊΒψΘΚ a. ΩιΡΎ”οΨδ «Ά§ ±÷¥––ΒΡΘ§Φ¥≥Χ–ρΝς≥ΧΩΊ÷Τ“ΜΫχ»κΒΫΗΟ≤Δ––”οΨδΩιΘ§ΩιΡΎ”οΨδ‘ρΆ§ ±ΩΣ Φ÷¥––ΓΘ

b.ΩιΡΎΟΩΧθ”οΨδΒΡ―”≥Ό ±Φδ «œύΕ‘”Ύ≥Χ–ρΝς≥ΧΩΊ÷ΤΫχ»κΒΫΩιΡΎΒΡΖ¬’φ ±ΦδΒΡΓΘ

1) ≤…”Ο¥°––”οΨδΩιΘΚ

module wave_tb1;

reg wave;

ΓΓ parameter T=10;

ΓΓ initial

ΓΓ begin

ΓΓΓΓ wave=0;

ΓΓΓΓ #T wave=1;

ΓΓΓΓ #T wave=0;

#T wave=1;

ΓΓΓΓ #T wave=0;

ΓΓΓΓ #T wave=1;

ΓΓ end

endmodule |

(2) ≤…”Ο≤Δ––”οΨδΩιΘΚ

module wave_tb2;

ΓΓΓΓreg wave;

ΓΓΓΓparameter T=10;

ΓΓΓΓinitial

fork

ΓΓΓΓ wave=0;

ΓΓΓΓ #T wave=1;

ΓΓΓΓ #(2*T) wave=0;

ΓΓΓΓ #(3*T) wave=1;

ΓΓΓΓ #(4*T) wave=0;

ΓΓΓΓ #(5*T) wave=1;

ΓΓΓΓ join

ΓΓΓΓendmodule |

2.3 Ιΐ≥ΧΗ≥÷Β”οΨδ

Ιΐ≥ΧΩι÷–ΒΡΗ≥÷Β”οΨδ≥ΤΈΣΙΐ≥ΧΗ≥÷Β”οΨδΓΘ

Ιΐ≥Χ–‘Η≥÷Β «‘Ύinitial”οΨδΜρalways”οΨδΡΎΒΡΗ≥÷ΒΘ§Υϋ÷ΜΡήΕ‘ΦΡ¥φΤς ΐΨίάύ–ΆΒΡ±δΝΩΗ≥÷ΒΓΘ

Ιΐ≥ΧΗ≥÷Β”οΨδ”–Ήη»ϊΗ≥÷Β”οΨδΚΆΖ«Ήη»ϊΗ≥÷Β”οΨδΝΫ÷÷ΓΘ

2.3.1. Ήη»ϊΗ≥÷Β”οΨδ

Ήη»ϊΗ≥÷Β”οΨδΒΡ≤ΌΉςΖϊΚ≈ΈΣΓΑ=Γ±Θ§Τδ”οΖ®Ηώ Ϋ «ΘΚ ±δΝΩ?=?±μ¥ο ΫΘΜ

άΐ»γΘΚΓΓb = a;

Β±“ΜΗω”οΨδΩι÷–”–ΕύΧθΉη»ϊΗ≥÷Β”οΨδ ±Θ§»γΙϊ«ΑΟφΒΡΗ≥÷Β”οΨδΟΜ”–Άξ≥…Θ§‘ρΚσΟφΒΡ”οΨδΨΆ≤ΜΡή±Μ÷¥––Θ§Ζ¬Ζπ±ΜΉη»ϊΝΥ“Μ―υΘ§“ρ¥Υ≥ΤΈΣΉη»ϊΗ≥÷ΒΖΫ ΫΓΘ

Ήη»ϊΗ≥÷Β”οΨδΒΡΧΊΒψΘΚ

(1) ‘Ύ¥°––”οΨδΩι÷–Θ§Υ≥–ρ÷¥––ΘΜ‘Ύ≤Δ––”οΨδΩι÷–,Ά§ ±÷¥––Θ§ΟΜ”–œ»Κσ÷°Ζ÷ΓΘ

(2) ÷¥––Ήη»ϊΗ≥÷Β”οΨδΒΡΥ≥–ρ «Θ§œ»ΦΤΥψΒ»Κ≈”“ΕΥ±μ¥ο ΫΒΡ÷ΒΘ§»ΜΚσΝΔΩΧΫΪΦΤΥψΒΡ÷ΒΗ≥ΗχΉσ±ΏΒΡ±δΝΩΘ§”κΖ¬’φ ±ΦδΈόΙΊΓΘ

2.3.2. Ζ«Ήη»ϊΗ≥÷Β”οΨδ

Ζ«Ήη»ϊΗ≥÷Β”οΨδΒΡ≤ΌΉςΖϊΚ≈ΈΣΓΑ<=Γ±Θ§Τδ”οΖ®Ηώ Ϋ «ΘΚ

±δΝΩ<=±μ¥ο ΫΘΜ

άΐ»γΘΚb?<= a;

»γΙϊ‘Ύ“ΜΗω”οΨδΩι÷–”–ΕύΧθΖ«Ήη»ϊΗ≥÷Β”οΨδΘ§‘ρΚσΟφ”οΨδΒΡ÷¥––≤ΜΜα ήΒΫ«ΑΟφ”οΨδΒΡœό÷ΤΘ§“ρ¥Υ≥ΤΈΣΖ«Ήη»ϊΗ≥÷ΒΖΫ ΫΓΘ

Ζ«Ήη»ϊΗ≥÷Β”οΨδΒΡΧΊΒψΘΚ

(1) ‘Ύ¥°––”οΨδΩι÷–Θ§÷¥––ΟΜ”–œ»Κσ÷°Ζ÷,ΗςΧθ”οΨδ≤Δ––÷¥––ΓΘ

(2) ÷¥––Ζ«Ήη»ϊΗ≥÷Β”οΨδΒΡΥ≥–ρ «Θ§œ»ΦΤΥψ”“ΕΥ±μ¥ο ΫΒΡ÷ΒΘ§»ΜΚσΒ»¥ΐ―”≥Ό ±ΦδΒΡΫα χΘ§‘ΌΫΪΦΤΥψΒΡ÷ΒΗ≥ΗχΉσ±ΏΒΡ±δΝΩ

“ΜΑψ«ιΩωœ¬ΉιΚœ¬ΏΦ≠Βγ¬Ζ”ΟΉη»ϊΗ≥÷ΒΘ§ ±–ρ¬ΏΦ≠Βγ¬Ζ”ΟΖ«Ήη»ϊΗ≥÷ΒΓΘ

άΐΧβΘΚ

a.≥Χ–ρ1

module block1(din,clk,out1,out2);ΓΓΓΓ

input din,clk;ΓΓΓΓ

output out1,out2;ΓΓΓΓ

reg out1,out2;ΓΓΓΓ

always@(posedge clk)ΓΓΓΓ

begin

out1=din;ΓΓΓΓ

out2=out1;ΓΓΓΓ

end

endmodule |

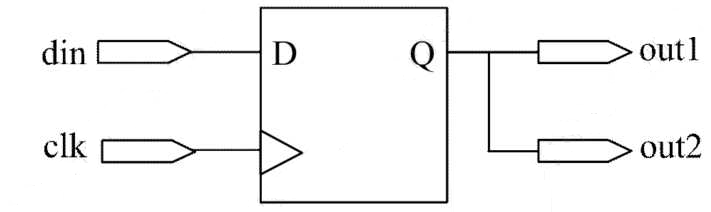

≥Χ–ρ1ΒΡΒγ¬ΖΫαΙΙ:

b.≥Χ–ρ2

module non_block1(din,clk,out1,out2);ΓΓΓΓ

input din,clk;ΓΓΓΓ

output out1,out2;ΓΓΓΓ

reg out1,out2;

always@(posedge clk)ΓΓΓΓ

beginΓΓΓΓ

out1<=din;ΓΓΓΓ

out2<=out1;ΓΓΓΓ

end

endmodule |

ΉΔ“βΘΚ¥Υ¥ΠΒΡout2ΈΣout1…œ“ΜΫΉΕΈΒΡ÷ΒΘ§≤Μ «¥Υ¥Πout1ΒΡ÷ΒΓΘ

≥Χ–ρ2ΒΡΒγ¬ΖΫαΙΙ :

c.ΫΪ≥Χ–ρΘ®2Θ©ΗΡΈΣΉη»ϊΗ≥÷Β”οΨδ

module block2(din,clk,out1,out2);ΓΓΓΓ

input din,clk;ΓΓΓΓ

output out1,out2;ΓΓΓΓ

reg out1,out2;ΓΓΓΓ

always@(posedge clk)ΓΓΓΓ

beginΓΓΓΓ

out2=out1;

out1=din;ΓΓΓΓ

endΓΓ

endmodule |

2.4 Ιΐ≥ΧΝ§–χΗ≥÷Β”οΨδΘ®ΝΥΫβΘ©

Ιΐ≥ΧΝ§–χΗ≥÷Β”οΨδΩ…“‘‘ΎalwaysΚΆinitialΙΐ≥Χ”οΨδ÷–Ε‘Ν§œΏ–ΆΚΆΦΡ¥φΤς–Ά±δΝΩάύ–ΆΫχ––Η≥÷Β≤ΌΉςΓΘ

Ιΐ≥ΧΝ§–χΗ≥÷Β≤ΜΡήΙΜΕ‘ΦΡ¥φΤς–Ά±δΝΩΫχ––ΈΜ≤ΌΉςΘ§÷ΜΡή’ϊΧεΗ≥÷ΒΓΘ

‘ΎVerilog HDL÷–Θ§Ιΐ≥ΧΝ§–χΗ≥÷Β”οΨδ”–ΝΫ÷÷άύ–ΆΘΚΗ≥÷ΒΓΔ÷Ί–¬Η≥÷Β”οΨδ(assignΓΔdeassign)ΚΆ«Ω÷ΤΓΔ ΆΖ≈”οΨδ(forceΓΔrelease)ΓΘ

a.Η≥÷Β”οΨδΚΆ÷Ί–¬Η≥÷Β”οΨδ assignΚΆdeassign”οΨδΙΙ≥…ΝΥ“ΜάύΙΐ≥Χ–‘Ν§–χΗ≥÷Β”οΨδΘ§÷ΜΡή”Ο”ΎΕ‘ΦΡ¥φΤςάύ–Ά±δΝΩΒΡΝ§–χΗ≥÷Β≤ΌΉς.

b.«Ω÷Τ”οΨδΚΆ ΆΖ≈”οΨδ

forceΚΆrelease”οΨδ”κassignΚΆdeassign”οΨδάύΥΤΘ§“≤ «“Μ÷÷Ιΐ≥ΧΝ§–χΗ≥÷Β”οΨδΓΘΡήΕ‘ΦΡ¥φΤςάύ–Ά±δΝΩΚΆœΏΆχάύ–Ά ΐΨίΫχ––≤ΌΉςΓΘ÷ς“Σ”Ο”ΎΖ¬’φ≤β ‘Θ§±ψ”ΎΕ‘Ρ≥÷÷–≈Κ≈Ϋχ––ΝΌ ±–‘ΒΡΗ≥÷ΒΚΆ≤β ‘ΓΘ

ΉΔ“βΘΚΝ§–χΗ≥÷Β”οΨδΈΣ ΐΨίΝςΫ®ΡΘΘ§Ζ÷ΈΣœ‘ ΫΚΆ“ΰ ΫΝ§–χΗ≥÷ΒΓΘ

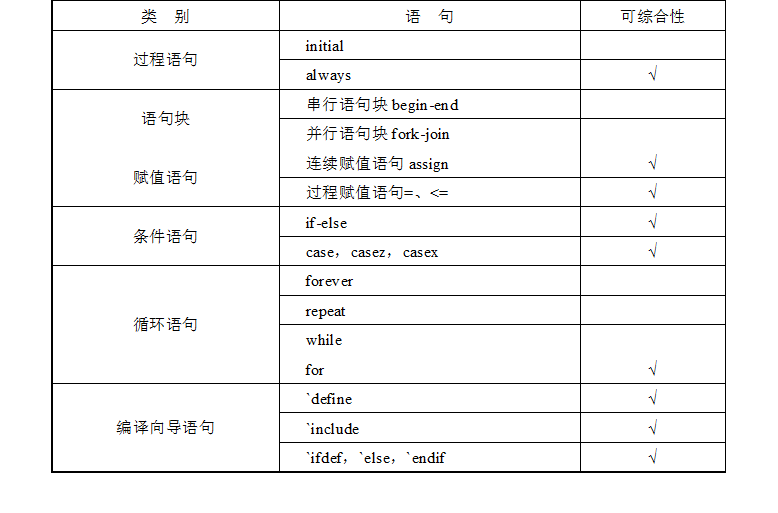

2.5 ΧθΦΰΖ÷÷ß”οΨδ Verilog HDLΒΡΧθΦΰΖ÷÷ß”οΨδ”–ΝΫ÷÷ΘΚifΧθΦΰΖ÷÷ß”οΨδΚΆcaseΧθΦΰΖ÷÷ß”οΨδΓΘ

1Θ°ifΧθΦΰΖ÷÷ß”οΨδ

ΧθΦΰ”οΨδ÷ΜΡή‘ΎinitialΚΆalways”οΨδ“ΐΒΦΒΡ”οΨδΩι(begin-end)÷– Ι”ΟΘ§ΡΘΩιΒΡΤδΥϋ≤ΩΖ÷ΕΦ≤ΜΡή Ι”ΟΓΘ

ΉΔ“βΘΚ

»τΈΣ0ΓΔxΓΔzΘ§‘ρΑ¥ΓΑΦΌΓ±¥ΠάμΘΜ»τΈΣ1Θ§‘ρΑ¥ΓΑ’φΓ±¥ΠάμΘ§÷¥––÷ΗΕ®ΒΡ”οΨδΩιΓΘ

άΐ»γΘΚ

if(a) Β»Φέ”Ύ if(a==1)

if(!a) Β»Φέ”Ύ if(a!=1)

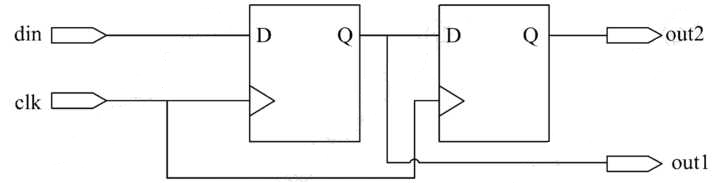

2Θ°caseΧθΦΰΖ÷÷ß”οΨδ

œύΕ‘”Ύif”οΨδ÷Μ”–ΝΫΗωΖ÷÷ßΕχ―‘Θ§case”οΨδ «“Μ÷÷Ω… Βœ÷Εύ¬ΖΖ÷÷ß―Γ‘ώΩΊ÷ΤΒΡ”οΨδΓΘ

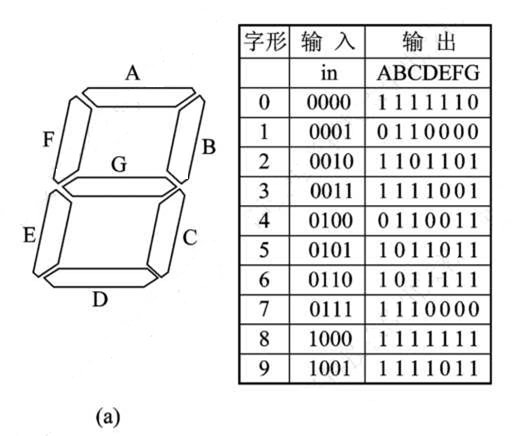

“ΜΑψΒΡΘ§case”οΨδΕύ”Ο”ΎΕύΧθΦΰ“κ¬κΒγ¬Ζ…ηΦΤΘ§»γΟη ω“κ¬κΤςΓΔ ΐΨί―Γ‘ώΤςΓΔΉ¥Χ§ΜζΦΑΈΔ¥ΠάμΤςΒΡ÷ΗΝν“κ¬κΒ»ΓΘ

Β±”Οcase”οΨδΕ‘ΩΊ÷Τ±μ¥ο ΫΚΆΤδΚσΒΡ÷ΒΫχ––±»Ϋœ ±Θ§±Ί–κ «“Μ÷÷»ΪΒ»±»ΫœΘ§±Ί–κ±Θ÷ΛΝΫ’ΏΒΡΕ‘”ΠΈΜ»ΪΒ»ΓΘ

’φ÷Β±μΘΚ

ΉΔ“βΘΚ

Θ®1Θ©default―ΓœνœύΒ±”Ύif-else”οΨδ÷–ΒΡelse≤ΩΖ÷Θ§“ΜΑψ“Σ”–ΓΘ

(2)case”οΨδΒΡΥυ”–±μ¥ο ΫΒΡ÷ΒΒΡΈΜΩμ±Ί–κœύΒ»ΓΘ

άΐΧβΘΚ”Οcase”οΨδΟη ωBCD ΐ¬κΙή“κ¬κΓΘ

module BCD_decoder(out,in);ΓΓΓΓ

output[6:0]out;ΓΓΓΓ

input[3:0]in;ΓΓΓΓ

reg [6:0]out;ΓΓΓΓ

always@(in)ΓΓΓΓ

beginΓΓΓΓ

case(in)ΓΓΓΓ

4'd0:out=7'b1111110; //4'd0±μ Ψ4ΈΜ °Ϋχ÷ΤΘ§ ΐ÷ΒΈΣ0

4'd1:out=7'b0110000;ΓΓΓΓ

4'd2:out=7'b1101101;ΓΓΓΓ

4'd3:out=7'b1111001;ΓΓΓΓΓΓ

4'd4:out=7'b0110011;ΓΓΓΓ

4'd5:out=7'b1011011;

4'd6:out=7'b1011111;ΓΓΓΓ

4'd7:out=7'b1110000;ΓΓΓΓ

4'd8:out=7'b1111111;ΓΓΓΓ

4'd9:out=7'b1111011;

default:out=7'bx;ΓΓΓΓ

endcaseΓΓ

endendmodule |

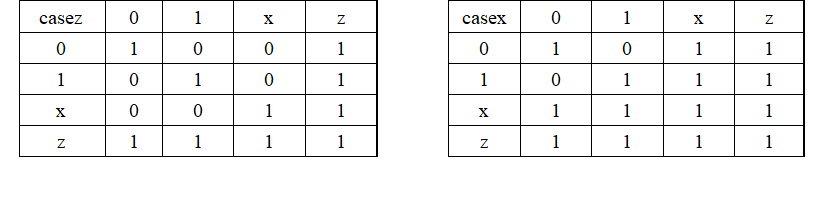

≥ΐΝΥcaseΖ÷÷ß”οΨδ“‘ΆβΘ§ΜΙ”–casezΓΔcasex’βΝΫ÷÷ΙΠΡήάύΥΤΒΡΧθΦΰΖ÷÷ß”οΨδ.Τδ’φ÷Β±μΘΚ

‘Ύcasez”οΨδ÷–Θ§”–“ΜΈΜΒΡ÷Β «zΘ§Φ¥»œΈΣ’β“ΜΈΜΒΡ±»ΫœΫαΙϊ”ά‘Ε «’φΓΘ

Εχ‘Ύcasex”οΨδ÷–Θ§‘ρΑ―’β÷÷¥ΠάμΖΫ ΫΫχ“Μ≤Ϋά©’ΙΒΫΕ‘xΒΡ¥ΠάμΘ§Φ¥»γΙϊ±»ΫœΒΡΥΪΖΫ(ΩΊ÷Τ±μ¥ο Ϋ”κ÷Βœν)”–“Μ±ΏΒΡΡ≥“ΜΈΜΒΡ÷Β «zΜρxΘ§Ρ«Ο¥’β“ΜΈΜΒΡ±»ΫœΨΆ≤Μ”ηΩΦ¬«ΓΘ

2.6 ―≠ΜΖ”οΨδ

Verilog HDL÷–ΙφΕ®ΝΥΥΡ÷÷―≠ΜΖ”οΨδΘ§Ζ÷±π «foreverΓΔrepeatΓΔwhileΚΆfor―≠ΜΖ”οΨδΓΘΕύ”Ο”Ύ≤β ‘Ζ¬’φ≥Χ–ρ…ηΦΤΓΘ

1Θ°forever―≠ΜΖ”οΨδ

forever”οΨδΒΡ”οΖ®Ηώ Ϋ «ΘΚ

forever ”οΨδΜρ”οΨδΩιΘΜ

forever―≠ΜΖ”οΨδΝ§–χ≤ΜΕœΒΊ÷¥––ΚσΟφΒΡ”οΨδΜρ”οΨδΩιΘ§≥Θ”Οά¥≤ζ…ζ÷ήΤΎ–‘ΒΡ≤®–ΈΘ§ΉςΈΣΖ¬’φΦΛάχ–≈Κ≈ΓΘ

always”οΨδΩ…ΕάΝΔ–¥‘Ύ≥Χ–ρ÷–ΓΘ

ΒΪforever‘Ύ”Ύ≤ΜΡήΕάΝΔ–¥‘Ύ≥Χ–ρ÷–ΓΘ“ΜΑψ”Ο‘ΎinitialΙΐ≥Χ”οΨδ÷–Θ§»γΙϊ‘Ύforever”οΨδ÷–ΟΜ”–Φ”»κ ±―”ΩΊ÷ΤΘ§forever”οΨδΫΪ‘Ύ0 ±―”ΚσΈόœό―≠ΜΖœ¬»ΞΓΘ

//”Ο forever”οΨδ≤ζ…ζ ±÷”–≈Κ≈ΓΘ

module forever_tb;ΓΓΓΓ

reg clock;ΓΓΓΓ

initialΓΓΓΓ

beginΓΓΓΓ

clock=0;ΓΓΓΓ

forever #50 clock=~clock;ΓΓΓΓ

end

endmodule |

2Θ°repeat―≠ΜΖ”οΨδ

”οΖ®Ηώ Ϋ «ΘΚ repeat(―≠ΜΖ¥Έ ΐ±μ¥ο Ϋ) ”οΨδΜρ”οΨδΩι(―≠ΜΖΧε)ΘΜ

Τδ÷–Θ§ΓΑ―≠ΜΖ¥Έ ΐ±μ¥ο ΫΓ±”Ο”Ύ÷ΗΕ®―≠ΜΖ¥Έ ΐΘ§Υϋ±Ί–κ «“ΜΗω≥Θ ΐΓΔ“ΜΗω±δΝΩΜρ’Ώ“ΜΗω–≈Κ≈ΓΘ

»γΙϊ―≠ΜΖ¥Έ ΐ «±δΝΩΜρ’Ώ–≈Κ≈Θ§‘ρ―≠ΜΖ¥Έ ΐ «―≠ΜΖΩΣ Φ÷¥–– ±±δΝΩΜρ’Ώ–≈Κ≈ΒΡ÷ΒΘ§Εχ≤Μ «―≠ΜΖ÷¥––ΤΎΦδΒΡ÷ΒΓΘ

// Ι”Οrepeat―≠ΜΖ”οΨδ≤ζ…ζΙΧΕ®÷ήΤΎ ΐΒΡ ±÷”–≈Κ≈ΓΘΓΓ

module repeat_tb;ΓΓΓΓ

reg clock;ΓΓΓΓ

initialΓΓΓΓ

beginΓΓΓΓ

clock=0;ΓΓΓΓ

repeat(8) clock=~clock;ΓΓΓΓ

endΓΓ

endmodule |

3Θ°while―≠ΜΖ”οΨδ

”οΖ®Ηώ Ϋ «ΘΚ

while(ΧθΦΰ±μ¥ο Ϋ) ”οΨδΜρ”οΨδΩιΘΜ

Τδ÷–Θ§ΓΑΧθΦΰ±μ¥ο ΫΓ±±μ Ψ―≠ΜΖΧεΒΟ“‘ΦΧ–χ÷ΊΗ¥÷¥–– ±±Ί–κ¬ζΉψΒΡΧθΦΰΘ§Υϋ≥Θ≥Θ «“ΜΗω¬ΏΦ≠±μ¥ο ΫΓΘ‘ΎΟΩ“Μ¥Έ÷¥––―≠ΜΖΧε÷°«ΑΕΦ“ΣΕ‘’βΗωΧθΦΰ±μ¥ο Ϋ «Ζώ≥…ΝΔΫχ––≈–ΕœΓΘ

// Ι”Οwhile”οΨδ≤ζ…ζ ±÷”–≈Κ≈ΓΘ

module while_tb;

ΓΓΓΓ reg clock;

ΓΓΓΓ initial

ΓΓΓΓ beginΓΓΓΓ

clock=0;ΓΓΓΓ

while(1)ΓΓΓΓ

#50 clock=~clock;ΓΓΓΓ

end

endmodule |

4Θ°for―≠ΜΖ”οΨδ

”οΖ®Ηώ Ϋ «ΘΚ

for(―≠ΜΖ±δΝΩΗ≥≥θ÷ΒΘΜ―≠ΜΖΫα χΧθΦΰΘΜ―≠ΜΖ±δΝΩ‘ω÷Β)

”οΨδΩιΘΜΓΓΓΓ

for”οΨδΒΡ÷¥––Ιΐ≥Χ «ΘΚœ»ΗχΓΑ―≠ΜΖ±δΝΩΗ≥≥θ÷ΒΓ±Θ§»ΜΚσ≈–ΕœΓΑ―≠ΜΖΫα χΧθΦΰΓ±Θ§»τΤδ÷ΒΈΣ’φΘ§‘ρ÷¥––for―≠ΜΖ”οΨδ÷–÷ΗΕ®ΒΡ”οΨδΩιΘ§»ΜΚσΫχ––ΓΑ―≠ΜΖ±δΝΩ‘ω÷ΒΓ±≤ΌΉςΘ§’β“ΜΙΐ≥ΧΫχ––ΒΫ―≠ΜΖΫα χΧθΦΰ¬ζΉψ ±Θ§for―≠ΜΖ”οΨδΫα χΓΘ

// Ι”Οfor”οΨδ≤ζ…ζ ±÷”–≈Κ≈ΓΘ

module for_clk;

ΓΓΓΓreg clk;

ΓΓΓΓinteger i;

ΓΓΓΓinitialΓΓΓΓ

begin

ΓΓΓΓ clk=0;

ΓΓΓΓ for(i=0;i>=0;i=i+1)ΓΓΓΓ

#50 clk=~clk;ΓΓΓΓ

end

endmodule |

―≠ΜΖ”οΨδ“≤Ω…“‘”Ο”ΎΩ…ΉέΚœΒγ¬ΖΒΡ…ηΦΤΘ§Β±≤…”Ο―≠ΜΖ”οΨδΫχ––ΦΤΥψΚΆΗ≥÷ΒΒΡΟη ω ±Θ§Ω…“‘ΉέΚœΒΟΒΫ¬ΏΦ≠Βγ¬ΖΓΘ

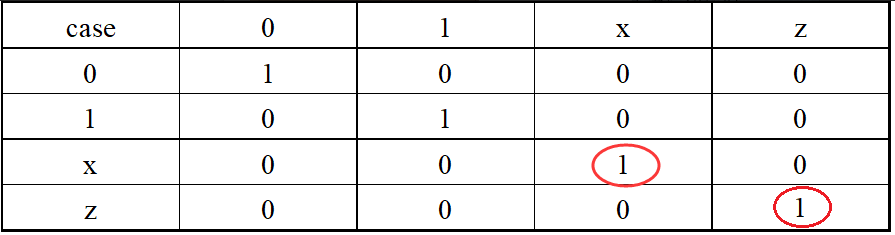

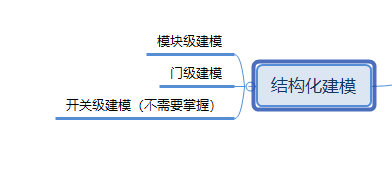

»ΐ.ΫαΙΙΜ·Ϋ®ΡΘ

ΫαΙΙΟη ωΖΫ ΫΨΆ «ΫΪ”≤ΦΰΒγ¬ΖΟη ω≥…“ΜΗωΖ÷ΦΕΉ”ΡΘΩιœΒΆ≥Θ§Ά®Ιΐ÷π≤ψΒς”Ο’β–©Ή”ΡΘΩιΙΙ≥…ΙΠΡήΗ¥‘”ΒΡ ΐΉ÷¬ΏΦ≠Βγ¬ΖΚΆœΒΆ≥ΒΡ“Μ÷÷Οη ωΖΫ ΫΓΘ

ΫαΙΙΟη ωΖΫ ΫΒΡΟη ωΡΩ±ξ «Βγ¬ΖΒΡ≤ψ¥ΈΫαΙΙΘ§Ήι≥…”≤ΦΰΒγ¬ΖΒΡΗς≤ψΙΠΡήΒΞ‘ΣΫΪ±ΜΟη ω≥…ΗςΗωΦΕ±πΒΡΉ”ΡΘΩιΓΘ

ΗυΨίΥυΒς”ΟΉ”ΡΘΩιΒΡ≤ΜΆ§≥ιœσΦΕ±πΘ§Ω…“‘ΫΪΡΘΩιΒΡΫαΙΙΟη ωΖΫ ΫΖ÷≥…»γœ¬»ΐάύΘΚ

(1) ΡΘΩιΦΕΫ®ΡΘΘΚΆ®ΙΐΒς”Ο”…”ΟΜß…ηΦΤ…ζ≥…ΒΡΒΆΦΕΉ”ΡΘΩιά¥Ε‘”≤ΦΰΒγ¬ΖΫαΙΙΫχ––ΥΒΟςΘ§’β÷÷«ιΩωœ¬ΒΡΡΘΩι”…ΒΆΦΕΡΘΩιΒΡ ΒάΐΉι≥…ΓΘ

(2) Ο≈ΦΕΫ®ΡΘΘΚΆ®ΙΐΒς”ΟVerilog HDLΡΎ≤ΩΒΡΜυ±ΨΟ≈ΦΕ‘ΣΦΰά¥Ε‘”≤ΦΰΒγ¬ΖΒΡΫαΙΙΫχ––ΥΒΟςΘ§’β÷÷«ιΩωœ¬ΒΡΡΘΩι”…Μυ±ΨΟ≈ΦΕ‘ΣΦΰΒΡ ΒάΐΉι≥…ΓΘ

(3) ΩΣΙΊΦΕΫ®ΡΘΘΚΆ®ΙΐΒς”ΟVerilog HDLΡΎ≤ΩΒΡΜυ±ΨΩΣΙΊ‘ΣΦΰά¥Ε‘”≤ΦΰΒγ¬ΖΒΡΫαΙΙΫχ––ΥΒΟςΘ§’β÷÷«ιΩωœ¬ΒΡΡΘΩι”…Μυ±ΨΩΣΙΊΦΕ‘ΣΦΰΒΡ ΒάΐΉι≥…ΓΘ

3.1 ΡΘΩιΦΕΫ®ΡΘ

»γΙϊΒ±«ΑΡΘΩι≤Μ‘Ό±ΜΤδΥϋΡΘΩιΥυΒς”ΟΘ§Ρ«Ο¥’βΗωΡΘΩι“ΜΕ® «ΥυΈΫΒΡΕΞ≤ψΡΘΩιΓΘ‘ΎΕ‘“ΜΗω”≤ΦΰœΒΆ≥ΒΡΟη ω÷–Θ§±ΊΕ®”–Εχ«“÷ΜΡή”–“ΜΗωΕΞ≤ψΡΘΩιΓΘ

1Θ°ΡΘΩιΒς”ΟΖΫ Ϋ

ΡΘΩιΒς”ΟΒΡΜυ±Ψ”οΖ®Ηώ Ϋ «ΘΚ

ΡΘΩιΟϊ<≤Έ ΐ÷ΒΝ–±μ> ΒάΐΟϊ(ΕΥΩΎΟϊΝ–±μ)ΘΜ

//“ΜΗωΦρΒΞΒΡΡΘΩιΒς”ΟΒΡάΐΉ”ΓΘ

module and_2(a,b,c); //2 δ»κ”κΟ≈ΡΘΩιΓΓΓΓ

input a,b;ΓΓΓΓ

output c;ΓΓΓΓ

assign c=a&b;

endmodule

module logic(in1,in2,q); //ΕΞ≤ψΡΘΩιΓΓΓΓ

input in1,in2;ΓΓΓΓ

output q;ΓΓΓΓ

and_2 U1(in1,in2,q); //ΡΘΩιΒΡΒς”Ο

endmodule |

2Θ°ΡΘΩιΕΥΩΎΕ‘”ΠΖΫ Ϋ

1) ΕΥΩΎΈΜ÷ΟΕ‘”ΠΖΫ Ϋ

ΕΥΩΎΈΜ÷ΟΕ‘”ΠΖΫ Ϋ «±ΜΒς”ΟΒΡΡΘΩιΑ¥’’“ΜΕ®ΒΡΥ≥–ρ≥ωœ÷‘ΎΕΥΩΎΝ§Ϋ”±μ÷–ΒΡ“Μ÷÷ΡΘΩιΒς”ΟΖΫ ΫΘ§Τδ”οΖ®Ηώ Ϋ «ΘΚ

ΡΘΩιΟϊ<≤Έ ΐ÷ΒΝ–±μ> ΒάΐΟϊ(<–≈Κ≈Οϊ1>Θ§<–≈Κ≈Οϊ2>Θ§Γ≠Θ§<–≈Κ≈Οϊn>)ΘΜ

2) ΕΥΩΎΟϊΕ‘”ΠΖΫ Ϋ

”οΖ®Ηώ Ϋ»γœ¬ΘΚ

ΡΘΩιΟϊ <≤Έ ΐ÷ΒΝ–±μ> ΒάΐΟϊ(.ΕΥΩΎΟϊ1<–≈Κ≈Οϊ1>Θ§.ΕΥΩΎΟϊ2<–≈Κ≈Οϊ2>Θ§Γ≠Θ§.ΕΥΩΎΟϊn<–≈Κ≈Οϊn>)ΘΜ

3.2 Ο≈ΦΕΫ®ΡΘ

3.3 ΩΣΙΊΦΕΫ®ΡΘ

|