| ±ύΦ≠ΆΤΦω: |

±ΨΈΡ÷ς“ΣΫ≤ΫβΝΥVerilog

”οΖ®ΒΡΜυ¥ΓΗ≈ΡνΘΚVerilogΡΘΩιΘ§Verilog”Ο”ΎΡΘΩιΒΡ≤β ‘Θ§VerilogΒΡΜυ±Ψ”οΖ®ΘΚΡΘΩιΒΡΫαΙΙΘ§Verilog ΐΨίάύ–ΆΒ»ΡΎ»ίΓΘ

±ΨΈΡά¥Ή‘”ΎΫώ»’ΆΖΧθΘ§”…ΜπΝζΙϊ»μΦΰAnna±ύΦ≠ΓΔΆΤΦωΓΘ |

|

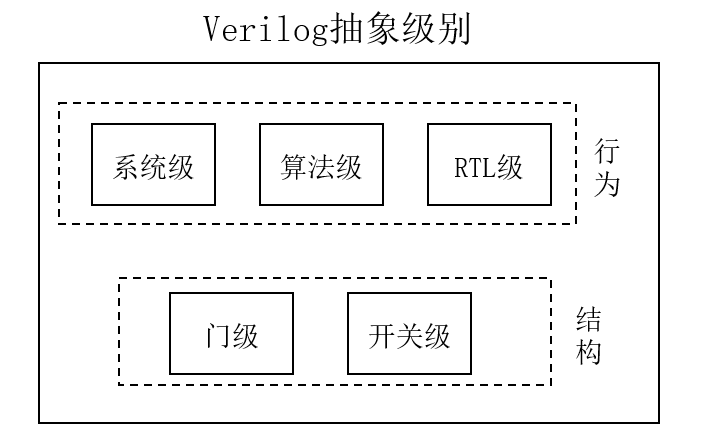

1. Verilog ”οΖ®ΒΡΜυ¥ΓΗ≈Ρν

Verilog HDL «“Μ÷÷”≤ΦΰΟη ω”ο―‘Θ§Τδ÷–HDL‘ρ «Hardware Description LanguageΒΡΥθ–¥ΓΘ“ρ¥ΥΘ§άϊ”ΟVerilog±ύ–¥ΒΡ≥Χ–ρΉν÷’ΜαΆ®ΙΐΙΛΨΏΉΣΜΜΈΣΨΏΧεΒΡΒγ¬ΖΡΘΩιΓΘ¥ΥΆβΘ§άϊ”ΟVerilog±ύ–¥ΒΡΡΘ–ΆΩ…“‘ « ΒΦ Βγ¬ΖΒΡ≤ΜΆ§ΦΕ±πΒΡ≥ιœσΘ§Ά®≥Θ«ιΩωœ¬Θ§Έ“Ο«ΫΪ’β÷÷≥ιœσΦΕ±πΖ÷ΈΣ“‘œ¬ΈεάύΘΚ

(1)œΒΆ≥ΦΕ(system-level)ΘΚ”Ο”ο―‘ΧαΙ©ΒΡΗΏΦΕΫαΙΙΡήΙΜ Βœ÷¥ΐ…ηΦΤΡΘΩιΒΡΆβ≤Ω–‘ΡήΒΡΡΘ–ΆΓΘ

(2)ΥψΖ®ΦΕ(algorithm-level)ΘΚ”Ο”ο―‘ΧαΙ©ΒΡΗΏΦΕΫαΙΙΡήΙΜ Βœ÷ΥψΖ®‘Υ––ΒΡΡΘ–ΆΓΘ

(3)RTLΦΕ(register transfer level)ΘΚΟη ω ΐΨί‘ΎΦΡ¥φΤς÷°ΦδΒΡΝςΕ·ΚΆ»γΚΈ¥ΠάμΓΔΩΊ÷Τ’β–© ΐΨίΝςΕ·ΒΡΡΘ–ΆΓΘ

(4)Ο≈ΦΕ(gate level)ΘΚΟη ω¬ΏΦ≠Ο≈“‘ΦΑ¬ΏΦ≠Ο≈÷°ΦδΝ§Ϋ”ΒΡΡΘ–ΆΓΘ

(4)ΩΣΙΊΦΕ(switch level)ΘΚΟη ωΤςΦΰ÷–»ΐΦΪΙήΚΆ¥φ¥ΔΫαΒψ“‘ΦΑΥϋΟ«÷°ΦδΝ§Ϋ”ΒΡΡΘ–ΆΓΘ

Τδ÷–Θ§«Α»ΐ÷÷≥ιœσΦΕ±πΈΣ––ΈΣΦΕ≥ιœσΘ§Υϋ≤ύ÷Ί”Ύ”ΎΟη ωΒγ¬ΖΒΡΙΠΡήΘΜΟ≈ΦΕΚΆΩΣΙΊΦΕ τ”ΎΫαΙΙΦΕ±π≥ιœσΘ§≤ύ÷Ί”ΎΡΘΩιΡΎ≤ΩΫαΙΙ Βœ÷ΒΡΨΏΧεΟη ωΓΘΙΊœΒΆΦ»γœ¬ΘΚ

1.1 VerilogΡΘΩιΒΡΜυ±ΨΗ≈Ρν

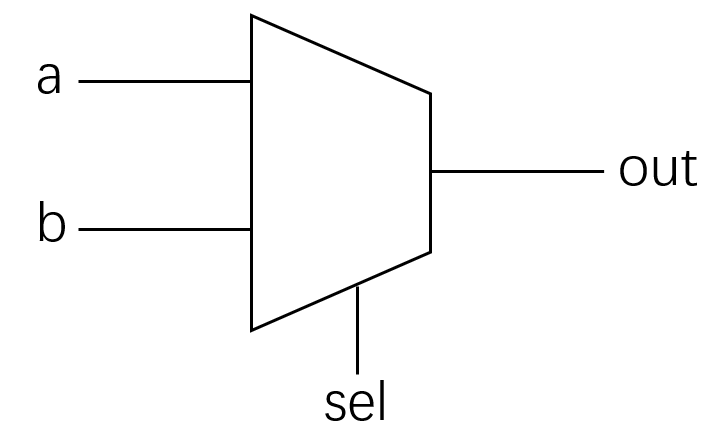

”…”ΎVerilog «“ΜΟ≈”≤ΦΰΟη ω”ο―‘Θ§“ρ¥Υ‘Ύ±ύ–¥≥Χ–ρΒΡ ±ΚρΆυΆυ «Ά®ΙΐΡΘΩιΒΡ–Έ Ϋά¥Ϋχ––Ήι÷·Θ§’βάοΒΡΡΘΩιΩ…“‘Ω¥ΉωΤδΥϊ±ύ≥Χ”ο―‘÷–ΒΡΚ· ΐΘ§Υϋ”Ο”ΎΟη ω“ΜΗωΧΊΕ®ΙΠΡήΒΡΡΘΩιΓΘΆ®ΙΐΫΪΕύΗωΡΘΩιΝΣΚœΤπά¥Ήν÷’Ω…“‘–Έ≥…Έ“Ο«ΒΡ…ηΦΤΡΘ–ΆΓΘ

œ¬Οφ¥”ΦΗΗωΦρΒΞΡΘΩιΒΡΖ÷Έωά¥–Έ≥…Ε‘ΡΘΩιΒΡΜυ±Ψ»œ ΕΘΚ

άΐ1ΘΚœ¬Οφ «“ΜΗωΕΰ―Γ“ΜΕύ¬Ζ―Γ‘ώΤςΒΡVerilog HDL≥Χ–ρΘΚ

module muxtwo(out,

a, b, sl);

input a, b, sl;

output out;

reg out;

always @ (sl or a or b)

if(!sl) out = a;

eles out = b;

endmodule |

ΤδΕ‘”ΠΒΡΒγ¬ΖΆΦ»γœ¬ΆΦΥυ ΨΘΚ

¥”¥ζ¬κ÷–Ω…“‘Ω¥≥ωΘ§“ΜΗωΡΘΩι «“ΜΕΈ“‘module-endmoduleΑϋΚ§ΒΡ¥ζ¬κΕΈΙΙ≥…ΓΘΫτΗζ‘ΎΙΊΦϋΉ÷module÷°ΚσΒΡ «ΡΘΩιΟϊmuxtwo“‘ΦΑΕΥΩΎΝ–±μ(out,

a, b, sel)Θ§’βάοΑϋΚ§ΝΥΥΡΗωΕΥΩΎΘ§“ά¥ΈΈΣ δ≥ωΕΥΩΎoutΓΔ–≈Κ≈ΕΥΩΎaΓΔ–≈Κ≈ΕΥΩΎb“‘ΦΑ―Γ‘ώΕΥΩΎselΓΘ

‘ΎΡΘΩιΡΎ≤ΩΘ§ΒΎ2ΓΔ3–– «I/OΥΒΟςΘ§ΥΒΟςΝΥΕΥΩΎΝ–±μ÷–ΕΥΩΎΒΡ δ»κ δ≥ωΖΫœρ“‘ΦΑΕΥΩΎΒΡΈΜ ΐΘΜΒΎ4–– «ΡΎ≤Ω–≈Κ≈…υΟςΘ§Ά®≥ΘΑϋά®regΚΆwireΝΫ÷÷ΘΜΉνΚσΒΡalwaysΩι «ΡΘΩιΒΡΙΠΡήΕ®“εΘ§Οη ωΒΡ «ΡΘΩιΒΡΚΥ–ΡΙΠΡήΓΘ

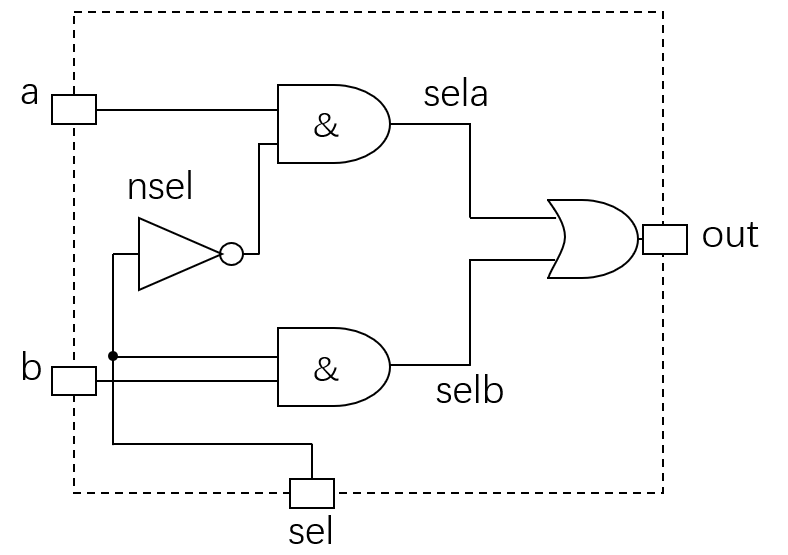

÷ΒΒΟΉΔ“βΒΡ «Θ§…œάΐ÷–ΒΡalways”οΨδ ΒΦ …œ“―Ψ≠ τ”Ύ––ΈΣΦΕ≥ιœσΝΥΘ§Υϋ÷ΜΙΊ–Ρ¬ΏΦ≠ΙΠΡήΕχ≤ΜΙΊ–ΡΤδΒγ¬ΖΫαΙΙΓΘœ¬ΟφΝΫΗω≥Χ–ρ «Ε‘…œΟφάΐΉ”÷–ΒΡΕΰ―Γ“ΜΕύ¬Ζ―Γ‘ώΤςΒΡΟ≈ΦΕΟη ωΖΫ ΫΘΚ

module muxtwo(out,

a, b, sel);

input a, b, sel;

output out;

wire nsel, sela, selb;

assign nsel = ~sel;

assign sela = a & nsel;

assign selb = b & sel;

assign out = sela | selb;

endmodule |

ΤδΕ‘”ΠΒΡΡΘΩι»γœ¬ΆΦΥυ ΨΘΚ

ΉΔ“βΘΚ…œΟφ≥Χ–ρ”ΟΒΫΝΥ&ΓΔ|ΓΔ~Β»¬ΏΦ≠‘ΥΥψΖϊά¥ Βœ÷Ο≈Βγ¬ΖΒΡΙΠΡήΘ§Έ“Ο«ΜΙΩ…“‘άϊ”ΟVerilog÷–ΒΡ¬ΏΦ≠‘ΣΦΰά¥ Βœ÷Ά§―υΒΡΙΠΡήΓΘ

module muxtwo(out,

a, b, sel);

input a, b, sel;

output out;

not u1(nsel, sl);

and #1 u2(sela, a, nsel);

and #1 u3(selb, b, sel);

or #1 u4(out, sela, selb);

endmodule |

ΉΔ“βΘΚ’βάοΒΡnotΓΔandΓΔorΕΦ «Verilog”ο―‘ΒΡ±ΘΝτΉ÷ΘΜu1ΓΔu2ΓΔu3ΓΔu4±μ Ψ¬ΏΦ≠‘ΣΦΰΒΡ ΒάΐΟϊ≥ΤΘΜ÷–ΦδΒΡ#1¥ζ±μΗΟΟ≈ δ»κΒΫ δ≥ωΒΡ―”≥ΌΈΣ1ΗωΒΞΈΜ ±ΦδΓΘ

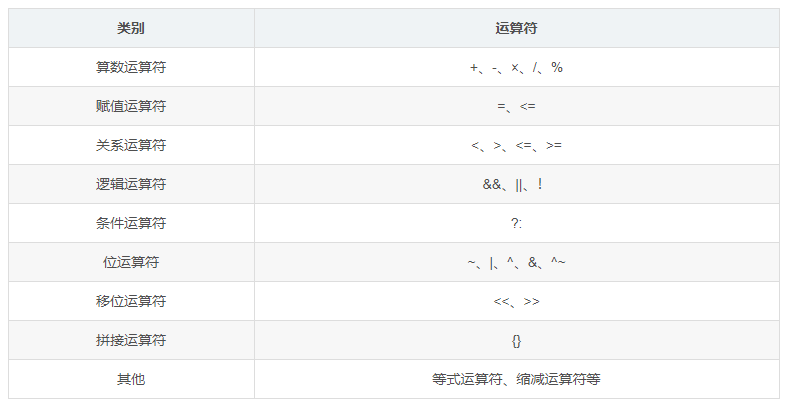

1.2 Verilog”Ο”ΎΡΘΩιΒΡ≤β ‘

VerilogΩ…”Ο”ΎΟη ω±δΜ·ΒΡ≤β ‘–≈Κ≈ΓΘΟη ω≤β ‘–≈Κ≈ΒΡ±δΜ·ΚΆ≤β ‘Ιΐ≥ΧΒΡΡΘΩι“≤Ϋ–Ήω≤β ‘ΤΫΧ®Θ§ΥϋΩ…Ε‘…œΟφΫι…ήΒΡΒγ¬ΖΡΘΩιΫχ––Ε·Χ§ΒΡ≤β ‘ΓΘΆ®ΙΐΙέ≤β±Μ≤β ‘ΡΘΩιΒΡ δ≥ω–≈Κ≈ «ΖώΖϊΚœ“Σ«σΓΘ

œ¬ΟφΩ¥“ΜΗωVerilogΒΡ≤β ‘ΡΘΩιΘ§ΥϋΕ‘…œΟφΒΡΕΰ―Γ“ΜΕύ¬Ζ―Γ‘ώΤςΫχ––≤β ‘ΘΚ

`include "muxtwo.v"

module t;

reg ain, bin, select;

reg clock;

wire outw;

initial

begin

ain = 0;

bin = 1;

select = 0;

clock = 0;

end

always #50 clock = ~clock;

always @ (posedge clock)

begin

#1 ain = {$ random} % 2;

#3 bin = {$ random} % 2;

end

always #1000 select = !select;

muxtwo m(.out(outw), .a(ain), .b(bin), .sel(select));

end module |

’βάοΕ®“εΝΥ“ΜΗωΡΘΩιt,ΥϋΟΜ”–ΕΥΩΎΝ–±μΚΆI/OΥΒΟςΘ§Τδ÷ς“ΣΑϋά®»ΐΗω≤ΩΖ÷ΘΚ–≈Κ≈≥θ ΦΜ·ΓΔ≤ζ…ζΦΛάχ–≈Κ≈ΓΔΡΘΩι≤β ‘ΓΘΤδ÷–Θ§ΡΘΩι≤β ‘≤ΩΖ÷÷Μ”–“Μ––¥ζ¬κΘ§ΨΆ «“ΐ”ΟΈ“Ο«÷°«ΑΥυ…ηΦΤΒΡmuxtwoΡΘΩιΘ§≤ΔΫΪ≤β ‘–≈Κ≈Νς¥ΪΫχ»ΞΓΘΈ“Ο«Ά®ΙΐΙέ≤λ δ»κ δ≥ωΒΡ–≈Κ≈ΝςΒΡ±δΜ·±ψΩ…“‘Ω¥ΒΫΡΘΩιΒΡ¬ΏΦ≠ΙΠΡή «Ζώ’ΐ»ΖΓΘ

’β÷÷≤β ‘Ω…“‘‘ΎΙΠΡήΘ®Φ¥––ΈΣΘ©ΦΕ…œΫχ––Θ§“≤Ω…“‘‘Ύ¬ΏΦ≠Άχ±μΘ®¬ΏΦ≠≤ΦΕϊ±μ¥ο ΫΘ©ΚΆΟ≈ΦΕΒγ¬Ζ…œΫχ––ΓΘΥϋΒΡΟϊ≥ΤΈΣΘ®RTLΘ©Ζ¬’φΓΔ¬ΏΦ≠Άχ±μΖ¬’φΚΆΟ≈ΦΕΖ¬’φΓΘ»γΙϊΟ≈ΦΕΫαΙΙΡΘΩι”κΨΏΧεΒΡΙΛ“’ΦΦ θΕ‘”ΠΤπά¥Θ§≤ΔΦ”…œ≤ΦΨ÷≤ΦœΏ“ΐ»κΒΡ―”≥ΌΡΘ–ΆΘ§¥Υ ±Ϋχ––ΒΡΖ¬’φ≥ΤΈΣ≤ΦœΏΚσΖ¬’φΘ§’β÷÷Ζ¬’φ”κ ΒΦ Βγ¬Ζ«ιΩωΖ«≥ΘΫ”ΫϋΓΘ

2. VerilogΒΡΜυ±Ψ”οΖ®

VerilogΒΡ”ο―‘ΚΆC”ο―‘ΒΡ”οΖ®ΚήάύΥΤΘ§ΒΪ”…”ΎVerilog «”≤ΦΰΟη ω”ο―‘Θ§“ρ¥Υ‘Ύ–μΕύΗ≈Ρν…œΚΆC”ο―‘ «Άξ»Ϊ≤ΜΆ§ΓΘ

2.1 ΡΘΩιΒΡΫαΙΙ

¥”…œΟφΒΡΕΰ―Γ“ΜΕύ¬Ζ―Γ‘ώΤςΒΡ¥ζ¬κΩ…“‘Ω¥≥ωΘ§“ΜΗωVerilogΡΘΩι“Μ÷¬ΑϋΚ§ΥΡΗω≤ΩΖ÷ΘΚΕΥΩΎΕ®“εΓΔI/OΥΒΟςΓΔΡΎ≤Ω–≈Κ≈…υΟςΚΆΙΠΡήΕ®“εΓΘ…œΟφ“―Ψ≠ΦρΒΞΫι…ήΝΥ’β“ΜΗω≤ΩΖ÷ΒΡΉς”ΟΘ§œ¬ΟφΕ‘’βΦΗΗω≤ΩΖ÷Ϋχ––œξœΗΒΡΉήΫαΘΚ

2.1.1 ΡΘΩιΒΡΕΥΩΎΕ®“ε

ΡΘΩιΒΡΕΥΩΎΕ®“εΚΆΡΘΩιΒΡC”ο―‘÷–Κ· ΐΒΡΕ®“εΖ«≥ΘΒΡœύΥΤΘ§≤ΜΙΐVerilog÷–ΡΘΩιΒΡ δ»κ δ≥ωΕΦΕ®“ε‘ΎΕΥΩΎΝ–±μ÷–Θ§≤ΜœώC”ο―‘Ρ«―υ”…ΖΒΜΊ÷ΒΓΘœ¬Οφ «Verilog÷–ΕΥΩΎΕ®“εΒΡ±ξΉΦ–Έ ΫΘΚ

| module name(port1,

port2, port3...); |

Τδ÷–Θ§ΕΥΩΎΝ–±μ÷–ΑϋΚ§ΝΥΡΘΩι÷–Υυ”–ΒΡ δ»κ δ≥ωΕΥΩΎΓΘ

2.1.2 ΡΘΩιΒΡI/OΥΒΟς

I/OΥΒΟςΒΡΉς”Ο «Ε‘ΕΥΩΎΝ–±μ÷–ΗςΗωΕΥΩΎΒΡ δ»κ δ≥ωΖΫœρ“‘ΦΑΕΥΩΎΒΡΈΜΩμΫχ––ΥΒΟςΘ§±ξΉΦ–Έ Ϋ»γœ¬ΘΚ

// δ»κΩΎ

input[width-1:0] port1;

input[width-1:0] port2;

...

input[width-1:0] porti;

// δ≥ωΩΎ

output[width-1:0] port1;

output[width-1:0] port2;

...

output[width-1:0] porj;

// δ»κ/ δ≥ωΩΎ

inout[width-1:0] port1;

inout[width-1:0] port2;

...

inout[width-1:0] pork; |

I/OΥΒΟς“≤Ω…“‘‘ΎΕΥΩΎΕ®“εΝ–±μ÷–…υΟςΘ§Ηώ Ϋ»γœ¬ΘΚ

module name(input

port1,

input port2,

...,

input porti,

output port1,

output port2,

...,

output portj); |

2.1.3 ΡΎ≤Ω–≈Κ≈ΥΒΟς

ΡΎ≤Ω–≈Κ≈ΥΒΟς÷ΗΒΡ «Ε‘ΡΘΩιΡΎ≤Ω–η“Σ”ΟΒΫΒΡregΚΆwireάύ–Ά±δΝΩΫχ––ΥΒΟςΘ§»γΘΚ

reg[width-1:0] variable1,

variable2, ...

wire[width-1:0] variable1, variable2, ... |

2.1.4 ΙΠΡήΕ®“ε

VerilogΡΘΩι÷–Ήν÷Ί“ΣΒΡ≤ΩΖ÷ΨΆ «ΡΘΩιΒΡΙΠΡήΕ®“ε≤ΩΖ÷Θ§÷ς“Σ”…»ΐ÷÷ΖΫΖ®Ω…“‘‘ΎΡΘΩι÷–≤ζ…ζ¬ΏΦ≠ΘΚ

(1) ”Οassign…υΟς”οΨδΘ§»γΘΚ

’β÷÷ΖΫΖ® «ΉνΦρΒΞΒΡ“Μ÷÷ΖΫΖ®Θ§ΥϋΆ®Ιΐ"assign equation"ΒΡΗώ Ϋά¥…ζ≥…¬ΏΦ≠ΓΘ

(2) ”Ο Βάΐ‘ΣΦΰΘ§»γΘΚ

≤…”Ο Βάΐ‘ΣΦΰΒΡΖΫΖ®œώ‘ΎΒγ¬ΖΆΦ δ»κΖΫ Ϋœ¬Βς”ΟΩβ‘ΣΦΰ“Μ―υΘ§Φϋ»κ‘ΣΦΰΒΡΟϊΉ÷ΚΆœύΝ§ΒΡ“ΐΫ≈Φ¥Ω…ΓΘ

(3) ”ΟalwaysΩιΘ§»γΘΚ

always @(posedge clk or posedge

clr)

begin

if(clr) q <= 0;

else if(en) q <= d;

end |

≤…”Οassign ”οΨδ «Οη ωΉιΚœ¬ΏΦ≠Ήν≥Θ”ΟΒΡΖΫΖ®÷°“ΜΓΘΕχalwaysΩιΦ»Ω…”Ο”ΎΟη ωΉιΚœ¬ΏΦ≠Θ§“≤Ω…”ΟΟη ω ±–ρ¬ΏΦ≠ΓΘalwaysΩιΩ…”ΟΚήΕύ÷÷Οη ω ÷ΕΈά¥±μ¥ο¬ΏΦ≠Θ§άΐ»γ…œάΐ÷–ΨΆάϊ”ΟΝΥif...else”οΨδά¥Οη ω¬ΏΦ≠ΙΊœΒΓΘ»γΙϊΑ¥’’“ΜΕ®ΒΡΖγΗώά¥±ύ–¥alwaysΩιΘ§Ω…“‘Ά®ΙΐΉέΚœΙΛΨΏΑ―‘¥¥ζ¬κΉ‘Ε·ΉέΚœ≥…Ο≈ΦΕΫαΙΙ±μ ΨΒΡΉιΚœΜρ ±–ρ¬ΏΦ≠Βγ¬ΖΓΘ

÷ΒΒΟΥΒΟςΒΡ «Θ§VerilogΡΘΩι÷–ΒΡΥυ”–Ιΐ≥ΧΩι(»γΘΚinitialΩιΓΔalwaysΩι)ΓΔΝ§–χΗ≥÷Β”οΨδΓΔ Βάΐ“ΐ”ΟΕΦ «≤Δ––ΒΡΓΘΕχalwaysΩιΡΎ≤ΩΒΡ”οΨδ «Υ≥–ρ÷¥––ΒΡΘ§άΐ»γ…œΟφalwaysΩι÷–ΈΣ“ΜΗωif...elseΧθΦΰΖ÷÷ß”οΨδΘ§Υϋ÷Μ”–‘ΎΥ≥–ρ÷¥––ΒΡ«ιΩωœ¬≤≈ «”–“β“εΒΡΓΘ¥ΥΆβΘ§ΝΫΗωΜρΕύΗωalwaysΩι÷°Φδ «Ά§ ±÷¥––ΒΡΓΘ

2.2 Verilog ΐΨίάύ–Ά

Verilog HDL ÷–ΉήΙ≤”–19÷÷ ΐΨίάύ–ΆΓΘΥϋΟ«”Οά¥±μ Ψ ΐΉ÷Βγ¬Ζ”≤Φΰ÷–ΒΡ ΐΨί¥φ¥ΔΚΆ¥ΪΥΆ‘ΣΥΊΒΡΓΘΤδ÷–ΉνΜυ±ΨΒΡΥΡ÷÷ ΐΨίάύ–ΆΈΣΘΚreg–ΆΓΔwire–ΆΓΔinteger–ΆΚΆparameter–ΆΘ§ΤδΥϊΒΡ ΐΨί¥σΕύ ΐΕΦ”κΜυ±Ψ¬ΏΦ≠ΒΞ‘ΣΒΡΫ®Ωβ”–ΙΊΘ§”κœΒΆ≥…ηΦΤΟΜ”–Κή¥σΒΡΙΊœΒΘ§“ρ¥ΥΈ“Ο«Ω…“‘œ»≤Μ”ΟΙΊ–ΡΥϋΟ«ΒΡΨΏΧε”ΟΖ®ΓΘ

Ε‘”ΎΈ“Ο«“ΜΑψΒΡΩΣΖΔ’Ώά¥ΥΒΘ§¥σΕύ ΐ«ιΩωœ¬ Ϋάϊ”ΟVerilogΫχ––––ΈΣΦΕΟη ωΘ§“ρ¥Υ≤Μ±ΊΙΐΕύΒΊΙΊ–ΡΟ≈ΦΕΚΆΩΣΙΊΦΕΒΡVerilog

HDL ”οΖ®œ÷œσΓΘ

2.2.1 ≥ΘΝΩ

‘Ύ≥Χ–ρ‘Υ––Ιΐ≥Χ÷–Θ§Τδ÷Β≤ΜΡή±ΜΗΡ±δΒΡΝΩ≥ΤΈΣ≥ΘΝΩΓΘœ¬Οφœ»Ε‘Verilog HDL”ο―‘÷– Ι”ΟΒΡ ΐΉ÷ΚΆ±μ ΨΖΫ ΫΫχ––ΉήΫαΓΘ

(1) ΐΉ÷

‘ΎVerilog HDL÷–Θ§’ϊ–Ά≥ΘΝΩΦ¥’ϊ≥Θ ΐ÷Β”–“‘œ¬ΥΡ÷÷Ϋχ÷ΤΒΡ±μ Ψ–Έ ΫΘΚ

a. ΕΰΫχ÷Τ’ϊ ΐ(bΜρ B)

b. °Ϋχ÷Τ’ϊ ΐ(dΜρD)

c. ΑΥΫχ÷Τ’ϊ ΐ(oΜρO)

d. °ΝυΫχ÷Τ’ϊ ΐ(hΜρH)

ΨΌάΐ»γœ¬ΘΚ

…œΟφ±μ Ψ“ΜΗωΕΰΫχ÷Τ’ϊ ΐΘ§ΥϋΒΡ °Ϋχ÷Τ÷ΒΈΣ172Θ§ΤδΈΜΩμΈΣ8ΈΜΓΘΗΟάΐΉ”≤…”ΟΝΥ“Μ÷÷Κή»ΪΟφΒΡ±μ¥ο ΐΉ÷ΒΡΖΫ ΫΘ§Φ¥ΘΚ

<ΈΜΩμ><Ϋχ÷Τ>< ΐΉ÷>

<ΈΜΩμ><Ϋχ÷Τ>< ΐΉ÷>

ΒΡ±μ¥οΖΫ ΫΘ§Τδ÷–ΈΜΩμΚΆΫχ÷Τ «Ω…―ΓœνΘ§Β± Γ¬‘ΈΜΩμœν ±Θ§±μ Ψ≤…”ΟΡ§»œΈΜΩμ(”…ΨΏΧεΒΡΜζΤςœΒΆ≥ΨωΕ®Θ§÷Ν…Ό32ΈΜ)ΘΜΒ± Γ¬‘Ϋχ÷Τœν ±Θ§±μ¥ο≤…”ΟΡ§»œΒΡ °Ϋχ÷Τ±μ ΨΖΫ ΫΓΘ

¥ΥΆβΘ§‘ΎVerilog÷–Έ“Ο«Ω…“‘≤…”ΟxΚΆzά¥±μ Ψ≤ΜΕ®÷ΒΚΆΗΏΉη÷ΒΘ§’βΨ≠≥Θ”Ο”Ύ≈–Εœ”οΨδΚΆcase”οΨδ÷–Θ§“‘ΧαΗΏ≥Χ–ρΒΡΩ…ΕΝ–‘Θ§»γœ¬άΐΘΚ

4'b10x0 //ΈΜΩμΈΣ4ΒΡΕΰΫχ÷Τ ΐ¥”ΒΆΈΜ ΐΤπΒΎ2ΈΜΈΣ≤ΜΕ®÷Β

4'b101z //ΈΜΩμΈΣ4ΒΡΕΰΫχ÷Τ ΐ¥”ΒΆΈΜ ΐΤπΒΎ1ΈΜΈΣΗΏΉη÷Β

12'dz //ΈΜΩμΈΣ12ΒΡ °Ϋχ÷Τ ΐΘ§Τδ÷ΒΈΣΗΏΉη÷Β

12'd? //Ά§…œ

8'h4x //ΈΜΩμΈΣ8ΒΡ °ΝυΫχ÷Τ ΐΘ§ΤδΒΆ4ΈΜ÷ΒΈΣ≤ΜΕ®÷Β |

÷ΒΒΟΉΔ“βΒΡ «Θ§Β±≤…”Ο≤ΜΆ§Ϋχ÷Τ±μ Ψ ±Θ§xΚΆz±μ ΨΒΡΈΜ ΐ“≤≤ΜΆ§ΓΘ

Β±Έ“Ο«–η“Σ±μ ΨΗΚ ΐ ±Θ§÷Μ–η“Σ‘Ύ±μ¥ο ΫΒΡΉν«ΑΟφΦ”…œ“ΜΗωΦθΚ≈Φ¥Ω…Θ§»γΘΚ

ΉΔ“βΘΚ–¥≥…8'-d5ΚΆ8'd-5ΒΡ–Έ ΫΕΦ «¥μΈσΒΡΓΘ

ΉνΚσΘ§Ω…“‘”Οœ¬Μ°œΏά¥Ζ÷ΗτΩΣ ΐΒΡ±μ¥ο“‘ΧαΗΏ≥Χ–ρΒΡΩ…ΕΝ–‘Θ§»γΘΚ

(2) ≤Έ ΐ(parameter)–Ά

‘ΎVerilog HDL÷–”Οparameterά¥Ε®“ε≥ΘΝΩΘ§Φ¥”Οparameterά¥Ε®“ε“ΜΗω±ξ ΕΖϊ¥ζ±μ“ΜΗω≥ΘΝΩΘ§≥ΤΈΣΖϊΚ≈≥ΘΝΩΘ§Φ¥±ξ ΕΖϊ–Έ ΫΒΡ≥ΘΝΩΘ§≤…”Ο±ξ ΕΖϊ¥ζ±μΒΡ“ΜΗω≥ΘΝΩΩ…“‘ΧαΗΏ≥Χ–ρΒΡΩ…ΕΝ–‘ΚΆΩ…Έ§ΜΛ–‘ΓΘΗώ Ϋ»γœ¬ΘΚ

| parameter ≤Έ ΐΟϊ1 = ±μ¥ο ΫΘ§ ≤Έ ΐΟϊ2

= ±μ¥ο ΫΘ§ ≤Έ ΐΟϊ3 = ±μ¥ο Ϋ, ..., ≤Έ ΐΟϊn = ±μ¥ο ΫΘΜ |

Τδ÷–Θ§parameter «≤Έ ΐ–‘ ΐΨίΒΡ»Ζ»œΖϊΓΘ

÷ΒΒΟΉΔ“βΒΡ «Θ§±μ¥ο Ϋ÷–÷ΜΡήΑϋΚ§÷°«ΑΕ®“εΒΡ≤Έ ΐΜρ’Ώ≥ΘΝΩ ΐΉ÷Θ§»γœ¬άΐΘΚ

parameter msb = 7; //Ε®“ε≤Έ ΐmsbΈΣ≥ΘΝΩ7

parameter e = 25, f = 29; //Ε®“εΝΫΗω≥ΘΝΩ≤Έ ΐ

parameter r = 5.7; //…υΟςrΈΣ“ΜΗω Β–Ά≤Έ ΐ

parameter hyte_size = 8, byte_msb = byte_size

- 1; //”Ο≥Θ ΐ±μ¥ο ΫΗ≥÷Β

parameter average_delay = (r + f) / 2; //”Ο≥Θ ΐ±μ¥ο ΫΗ≥÷Β |

≤Έ ΐ–Ά≥ΘΝΩΨ≠≥Θ”Ο”ΎΕ®“ε―”≥Ό ±ΦδΚΆ±δΝΩΩμΕ»ΓΘ‘ΎΡΘΩιΜρ Βάΐ“ΐ”Ο ±Θ§Ω…Ά®Ιΐ≤Έ ΐ¥ΪΒίΗΡ±δ‘Ύ±π“ΐ”ΟΡΘΩιΜρ Βάΐ÷–“―Ε®“εΒΡ≤Έ ΐΓΘœ¬ΟφΒΡάΐΉ”ΥΒΟςΝΥ‘Ύ≤ψ¥ΈΒς”ΟΒΡΒγ¬Ζ÷–ΗΡ±δ≤Έ ΐ≥Θ”ΟΒΡ“Μ–©”ΟΖ®ΘΚ

module Decode(A, F);

parameter Width = 1, Polarity = 1;

...

endmodule

module Top;

wire[3:0] A4;

wire[4:0] A5;

wire[15:0] F16;

wire[31:0] F32;

Decode #(4, 0) D1(A4, F16);

Decode #(5) D2(A5, F32);

endmodule |

…œ ω≥Χ–ρ÷–Θ§ΕΞ≤ψΡΘΩιΈΣTopΡΘΩιΘ§‘ΎTopΡΘΩι÷–ΝΫ¥Έ“ΐ”ΟΝΥDecodeΡΘΩιΘ§≤ΔΆ®Ιΐ#()ΒΡΖΫ ΫΫΪ≤Έ ΐΒΡ÷Β¥ΪΒίΒΫΝΥD1ΚΆD2÷–ΓΘ“ρ¥ΥΘ§ ΒΦ …œ‘ΎTopΡΘΩι÷–ΒΡD1 «≤Έ ΐ(Width,

Polarity)=(4, 0)ΒΡDecodeΡΘΩιΘ§D2 «≤Έ ΐ(Width, Polarity)=(5,

1)ΒΡDecodeΡΘΩιΓΘ

»γΙϊœκ“Σ‘Ύ“ΜΗωΡΘΩι÷–ΗΡ±δΝμ“ΜΗωΡΘΩι÷–ΒΡparameter÷ΒΘ§Ω…“‘Ά®ΙΐdefparamΟϋΝν Βœ÷Θ§»γœ¬ΘΚ

module Test;

wire W;

Top T();

endmodule

module Top;

wire W;

Block B1();

Block B2();

endmodule

module Block;

parameter P = 0;

endmodule

module Annotate;

defparam

Test.T.B1.P = 2,

Test.T.B2.P = 3;

endmodule |

Τδ÷–Θ§AnnotateΡΘΩιΆ®ΙΐdefparamΟϋΝνΗΡ±δΝΥΕΞ≤ψΡΘΩιTop÷–“ΐ”ΟΒΡΝΫΗωBlockΡΘΩι÷–ΒΡ≤Έ ΐPΓΘ

2.2.2 ±δΝΩ

±δΝΩ «‘Ύ≥Χ–ρ‘Υ––Ιΐ≥Χ÷–Ω…“‘±δΜ·ΒΡΝΩΘ§‘ΎVerilog HDL÷–±δΝΩΒΡάύ–Ά”…ΚήΕύ÷÷Θ§’βάο÷ΜΫι…ήΉν≥Θ”ΟΒΡwireΓΔregΚΆmemory–ΆΓΘ

(1) wire–Ά

wire–Ά ΐΨί≥Θ”Οά¥±μ Ψ“‘assignΙΊΦϋΉ÷÷ΗΕ®ΒΡΉιΚœ¬ΏΦ≠–≈Κ≈ΓΘVerilog≥Χ–ρΡΘΩι÷– δ»κΓΔ δ≥ω–≈Κ≈άύ–ΆΡ§»œ ±Ή‘Ε·Ε®“εΈΣwire–ΆΓΘwire–Ά–≈Κ≈Ω…“‘”ΟΉω»ΈΚΈΖΫ≥Χ ΫΒΡ δ»κΘ§“≤Ω…“‘”ΟΉω"assign"”οΨδΜρ Βάΐ‘ΣΦΰΒΡ δ≥ωΓΘΤδΕ®“εΗώ Ϋ»γœ¬ΘΚ

wire a; //Ε®“ε“ΜΗω1ΈΜΒΡwire–Ά ΐΨί

wire[width-1:0] b; //Ε®“ε“ΜΗωwidthΈΜΒΡwire–Ά ΐΨί

|

(2) reg–Ά

ΦΡ¥φΤς « ΐΨί¥φ¥ΔΒΞ‘ΣΒΡ≥ιœσΓΘΦΡ¥φΤς ΐΨίάύ–ΆΒΡΙΊΦϋΉ÷ΈΣregΓΘΆ®ΙΐΗ≥÷Β”οΨδΩ…“‘ΗΡ±δΦΡ¥φΤς¥φ¥ΔΒΡ÷ΒΘ§ΤδΉς”Ο”ΎΗΡ±δ¥ΞΖΔΤς¥φ¥ΔΒΡ÷ΒœύΒ±ΓΘ

÷ΒΒΟΉΔ“βΒΡ «Θ§reg–Ά ΐΨί≥Θ”Οά¥±μ ΨalwaysΩι÷–ΒΡ÷ΗΕ®–≈Κ≈Θ§≥Θ¥ζ±μ¥ΞΖΔΤςΓΘ«“‘ΎalwaysΩι÷–±ΜΗ≥÷ΒΒΡΟΩ“ΜΗω–≈Κ≈ΕΦ±Ί–κΕ®“ε≥…reg–ΆΘΓ

reg–Ά ΐΨίΒΡΕ®“εΖΫ ΫΚΆwire–Ά ΐΨίΕ®“εΖΫ ΫœύΆ§Θ§»γœ¬ΘΚ

reg rega; //Ε®“εΝΥ“ΜΗω1ΈΜΒΡreg–Ά ΐΨί

reg[width-1:0] regb; //Ε®“εΝΥ“ΜΗωwidthΈΜΒΡreg–Ά ΐΨί

|

reg–Ά ΐΨίΒΡΡ§»œ≥θ Φ÷Β «≤ΜΕ®÷ΒΓΘreg–Ά ΐΨίΩ…“‘Η≥’ΐ÷ΒΘ§“≤Ω…“‘Η≥ΗΚ÷ΒΓΘΒΪΒ±“ΜΗωreg–Ά ΐΨί ±“ΜΗω±μ¥ο ΫΒΡ≤ΌΉς ΐ ±Θ§ΥϋΒΡ÷Β±ΜΒ±Ήω «ΈόΖϊΚ≈÷ΒΘ§Φ¥’ΐ÷ΒΓΘΦ¥Β±“ΜΗωΥΡΈΜreg–Ά ΐΨί±ΜΗ≥÷ΒΈΣ-1 ±Θ§»γΙϊΫΪΤδΉςΈΣ±μ¥ο ΫΒΡΦΤΥψ ±Θ§‘ρΤδ÷Β±Μ»œΈΣ «+15ΓΘ

¥ΥΆβΘ§reg–Ά ΐΨί÷Η±ξ «±ΜΕ®“εΒΡ–≈Κ≈ΫΪ”Ο‘Ύ"always"ΡΘΩιΡΎ’β“ΜΒψΖ«≥Θ÷Ί“ΣΓΘ≤Δ≤Μ «ΥΒreg–Ά–≈Κ≈“ΜΕ® «ΦΡ¥φΤςΜρ¥ΞΖΔΤςΒΡ δ≥ωΘ§Υδ»Μreg–Ά–≈Κ≈≥Θ≥Θ «ΦΡ¥φΤςΜρ¥ΞΖΔΤςΒΡ δ≥ωΘ§ΒΪ≤Δ≤Μ“ΜΕ®Ήή «’β―υΓΘ

(3) memory–Ά

Verilog HDL÷– ΒΦ …œ «ΟΜ”–Ή®Ο≈ΒΡmemoryάύ–Ά ΐΨίΒΡΘ§Υϋ «Ά®ΙΐΕ‘reg–Ά±δΝΩΫ®ΝΔ ΐΉιά¥Ε‘ΦΡ¥φΤςΫχ––Ϋ®ΡΘΘ§ΥϋάύΥΤ”ΎC”ο―‘÷–ΒΡΕΰΈ§ ΐΉιΓΘΤδΗώ Ϋ»γœ¬ΘΚ

reg[n-1:0] mem1[m-1:0];

reg[n-1:0] mem2[m:1]; |

ΨΏΧεΒΡάΐΉ”»γœ¬ΘΚ

ΗΟάΐΉ”Ε®“εΝΥ“ΜΗωΟϊΈΣmemaΒΡ¥φ¥ΔΤςΘ§ΗΟ¥φ¥ΔΤς”–256Ηω8ΈΜΒΡΦΡ¥φΤςΘ§ΒΊ÷ΖΖΕΈß «0-255ΓΘ

ΉΔ“βΘΚ‘ΎVerilog÷–Ε‘¥φ¥ΔΤςΫχ––ΒΊ÷ΖΥς“ΐΒΡ±μ¥ο Ϋ±Ί–κΈΣ≥Θ ΐ±μ¥ο ΫΘ§»γœ¬ΘΚ

parameter wordsize = 16,

memsize = 256;

reg[wordsize] mem[memsize-1:0]; |

ΗΟάΐΉ”Ε®“εΝΥ“ΜΗωΟϊΈΣmemΒΡ¥φ¥ΔΤςΘ§ΗΟ¥φ¥ΔΤς”–256Ηω16ΈΜΒΡΦΡ¥φΤςΓΘ

ΉνΚσΜΙ”–“ΜΒψ÷ΒΒΟΉΔ“βΒΡ «Θ§Έ“Ο«≤ΜΡήΕ‘¥φ¥ΔΤς’ϊΧεΫχ––Η≥÷ΒΘ§»γmem =

0”οΨδ «Ζ«Ζ®ΒΡΘ§»γΙϊΈ“Ο«“ΣΗΡ±δ¥φ¥ΔΤςΒΡ÷ΒΘ§”ΠΒ±÷ΗΕ®ΗΟΒΞ‘Σ‘Ύ¥φ¥ΔΤς÷–ΒΡΒΊ÷ΖΘ§»γœ¬ΘΚ

| mem[5] = 0; //ΫΪmem÷–ΒΡΒΎ5ΗωΒΞ‘ΣΗ≥÷ΒΈΣ0 |

2.3 ‘ΥΥψΖϊΦΑ±μ¥ο Ϋ

Verilog HDL ”ο―‘ΒΡ‘ΥΥψΖϊΚήΖαΗΜΘ§Α¥ΙΠΡήΖ÷Ω…Ζ÷ΈΣ“‘œ¬ΦΗάύΘΚ

2.3.1 Μυ±ΨΥψ ΐ‘ΥΥψΖϊ

‘ΎVerilog HDL÷–Θ§Υψ ΐ‘ΥΥψΖϊ”÷≥ΤΈΣΕΰΫχ÷Τ‘ΥΥψΖϊΘ§Τδ÷–Φ”Ζ®‘ΥΥψΖϊ”÷≥ΤΈΣ’ΐ÷Β‘ΥΥψΖϊΘ§ΦθΖ®‘ΥΥψΖϊ”–≥ΤΈΣΗΚ÷Β‘ΥΥψΖϊΓΘ‘Ύ≥ΐΖ®‘ΥΥψ÷–Θ§ΫαΙϊ÷Β“Σ¬‘»Ξ–Γ ΐ≤ΩΖ÷Θ§÷Μ»Γ’ϊ ΐ≤ΩΖ÷ΓΘΕχΫχ––»ΓΡΘ‘ΥΥψ ±Θ§ΫαΙϊ÷ΒΒΡΖϊΚ≈ΈΜ≤…”ΟΡΘ‘ΥΥψ ΫάοΒΡΒΎ“ΜΗω≤ΌΉς ΐΒΡΖϊΚ≈ΈΜΓΘ¥ΥΆβΘ§“Σ«σΫχ––ΡΘ‘ΥΥψΒΡΝΫΗωΝΩ±Ί–κΕΦ «’ϊ ΐΓΘ»γœ¬ΘΚ

10/3 //ΫαΙϊΈΣ3

10%3 //”ύ ΐΈΣ1

-10%3 //”ύ ΐΈΣ-1

10%-3 //”ύ ΐΈΣ1

12%3 //”ύ ΐΈΣ0 |

2.3.2 ΈΜ‘ΥΥψΖϊ

Veirlog HDLΉςΈΣ“Μ÷÷”≤ΦΰΟη ω”ο―‘Θ§ «’κΕ‘”≤ΦΰΒγ¬ΖΕχ―‘ΒΡΓΘ‘Ύ”≤ΦΰΒγ¬Ζ÷–”–4÷–Ή¥Χ§Θ§Φ¥1,0,x,zΓΘ‘ΎΒγ¬Ζ÷––≈Κ≈Ϋχ––”κΓΔΜρΓΔΖ« ±Θ§‘ΎVerilog

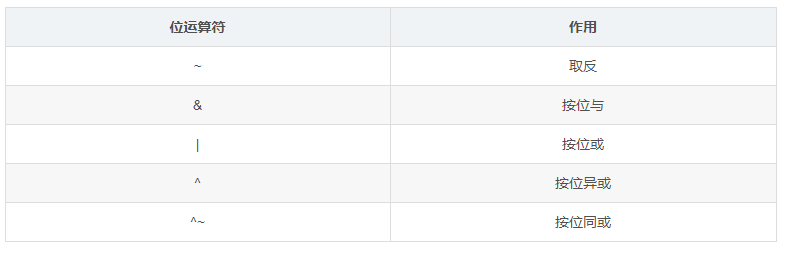

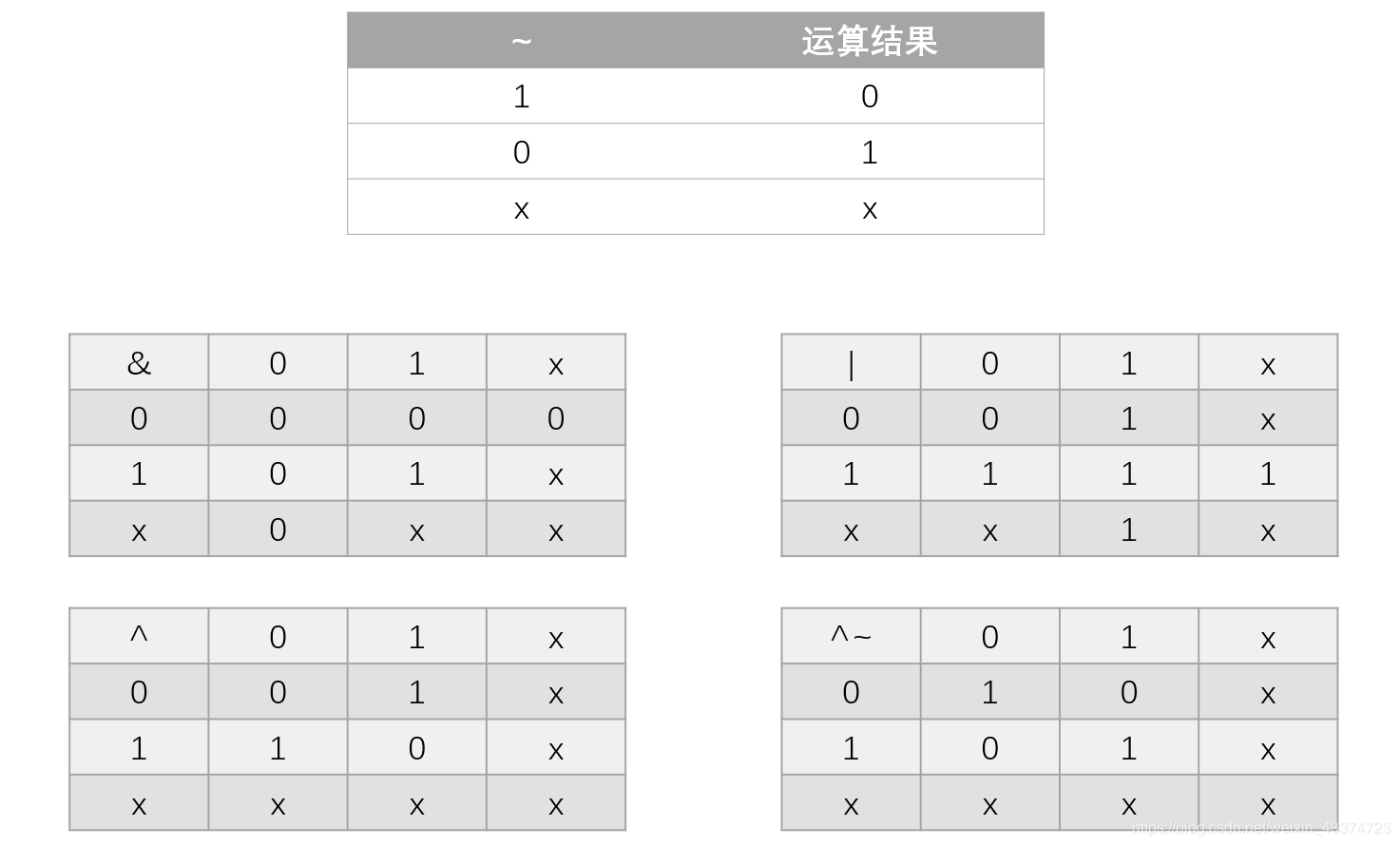

HDL÷–‘ρ «œλ”ΠΒΡ≤ΌΉς ΐΒΡΈΜ‘ΥΥψΓΘVerilogHDLΧαΙ©ΝΥ“‘œ¬5÷÷ΈΜ‘ΥΥψΖϊΓΘ

Τδ÷–Θ§≥ΐΝΥ~ «ΒΞΡΩ‘ΥΥψΖϊΆβΤδ”ύΕΦ «ΥΪΡΩ‘ΥΥψΖϊΓΘ

œ¬ΆΦΝ–≥ωΝΥΈε÷÷ΈΣ‘ΥΥψΖϊΒΡ‘ΥΥψΙφ‘ρΘΚ

÷ΒΒΟΧαΦΑΒΡ «Θ§Β±ΝΫΗω≥ΛΕ»≤ΜΆ§ΒΡ ΐΨίΫχ––ΈΣ‘ΥΥψ ±Θ§œΒΆ≥ΜαΉ‘Ε·ΒΎΫΪΝΫ’Ώ”“ΕΥΕ‘ΤκΘ§ΈΜ ΐ…ΌΒΡ≤ΌΉς ΐΜα‘Ύœύ”ΠΒΡΗΏΈΜ”Ο0Χν¬ζΘ§“‘ ΙΝΫΗω≤ΌΉς ΐΑ¥ΈΜΫχ––≤ΌΉςΓΘ

2.2.3 ¬ΏΦ≠‘ΥΥψΖϊ

Verilog HDL÷–”–»ΐ÷÷¬ΏΦ≠‘ΥΥψΖϊ

Θ®1Θ©&&¬ΏΦ≠”κ

Θ®2Θ©|| ¬ΏΦ≠Μρ

Θ®3Θ©ΘΓ¬ΏΦ≠Ζ«

ΥϋΟ«ΒΡ”ΟΖ®ΚΆΚ§“ε”κC”ο―‘÷–ΒΡάύΥΤΘ§“ρ¥Υ‘Ύ¥Υ≤ΜΉΗ ωΝΥΓΘ

2.3.4 ΙΊœΒ‘ΥΥψΖϊ

Verilog HDL÷–”–Ι≤ΥΡ÷÷ΙΊœΒ‘ΥΥψΖϊ

Θ®1Θ©a<b

Θ®2Θ©a>b

Θ®3Θ©a<=b

Θ®4Θ©a>=b

‘ΎΫχ––ΙΊœΒ‘ΥΥψ ±Θ§»γΙϊ…υΟςΒΡΙΊœΒ «ΦΌΒΡΘ§‘ρΖΒΜΊ÷ΒΈΣ0ΘΜ»γΙϊ…υΟςΒΡΙΊœΒ «’φΒΡΘ§‘ρΖΒΜΊ÷ΒΈΣ1ΘΜ»γΙϊΡ≥Ηω≤ΌΉς ΐΒΡ÷Β≤ΜΕ®Θ§ΖΒΜΊΒΡ «≤ΜΕ®÷ΒΓΘ

2.3.5 Β» Ϋ‘ΥΥψΖϊ

Verilog HDL÷–¥φ‘ΎΥΡ÷÷Β» Ϋ‘ΥΥψΖϊ

Θ®1Θ©==

Θ®2Θ©ΘΓ=

Θ®3Θ©===

Θ®4Θ©ΘΓ==

Τδ÷–”κC”ο―‘≤ΜΆ§ΒΡΒψ‘Ύ”Ύ===ΚΆ!==,œ¬ΟφΝ–≥ω===”κ==ΒΡ’φ÷Β±μΘΚ

2.3.6 “ΤΈΜ‘ΥΥψΖϊ

Verilog HDL÷–”–ΝΫ÷÷“ΤΈΜ‘ΥΥψΖϊΘ§Ζ÷±π «>>ΚΆ<<Θ§Τδ Ι”ΟΖΫΖ®»γœ¬ΘΚ

a>>nΜρa<<n

a>>nΜρa<<n

Τδ÷–n±μ Ψ“Σ“ΤΕ·ΒΡΈΜ ΐΘ§Verilog÷–”Ο0ά¥Χν≤Ι“Τ≥ωΒΡΩ’ΈΜΓΘ

4'h1001 << 1 //5'h10010

4'b1010 << 2 //6'b101000

1<<b //32'b1000000

4'b1001 >> 1 //4'b0100

4'b1001 >> 4 //4'b0000 |

2.3.7 ΈΜΤ¥Ϋ”‘ΥΥψΖϊ

ΈΜΤ¥Ϋ”‘ΥΥψΖϊ{} «Verilog HDL÷–ΧΊ βΒΡ‘ΥΥψΖϊΘ§άϊ”Ο’βΗω‘ΥΥψΖϊΩ…“‘Α―ΝΫΗωΜρΕύΗω–≈Κ≈ΒΡΡ≥–©ΈΜΤ¥Ϋ”Τπά¥Ϋχ––‘ΥΥψ≤ΌΉςΓΘ Ι”ΟΖΫΖ®»γœ¬ΘΚ

{–≈Κ≈1ΒΡΡ≥ΦΗΈΜΘ§–≈Κ≈2ΒΡΡ≥ΦΗΈΜΘ§...,–≈Κ≈nΒΡΡ≥ΦΗΈΜ}

{–≈Κ≈1ΒΡΡ≥ΦΗΈΜΘ§–≈Κ≈2ΒΡΡ≥ΦΗΈΜΘ§...,–≈Κ≈nΒΡΡ≥ΦΗΈΜ}

άΐ»γΘΚ

{a, b[3:0], w, 3'b101}

Μρ

{a, b[3], b[2], b[1], b[0], w, 1'b1, 1'b0, 1'b1} |

ΈΜΤ¥Ϋ”ΜΙΩ…“‘≤…”Ο÷ΊΗ¥ΖΔά¥ΦρΜ·±μ¥ο ΫΘ§»γ

2.3.8 ΥθΦθ‘ΥΥψΖϊ

ΥθΦθ‘ΥΥψΖϊ «ΒΞΡΩ‘ΥΥψΖϊΘ§ΥϋΒΡΉς”ΟœύΒ±”ΎΕ‘“ΜΗω ΐΒΡΥυ”–ΈΜΫχ––ΒίΆΤΈΜ‘ΥΥψΓΘ»γ

reg[3:0] B;

reg C

C = &B; |

œύΒ±”ΎΘΚ

|

C = ((B[0] & B[1]) & B[2]) & B[3] |

|