| БрМЭЦМі: |

| БОЮФРДздгкВЉПЭдАЃЌБОЮФжївЊЭЈЙ§ЭМР§ЖдЫГађжДаагяОфКЭВЂааДІРэгяОфзмНсЃЌЯЃЭћЖдФњЕФбЇЯАгаЫљАяжњЁЃ |

|

НсЙЙ

ОйР§

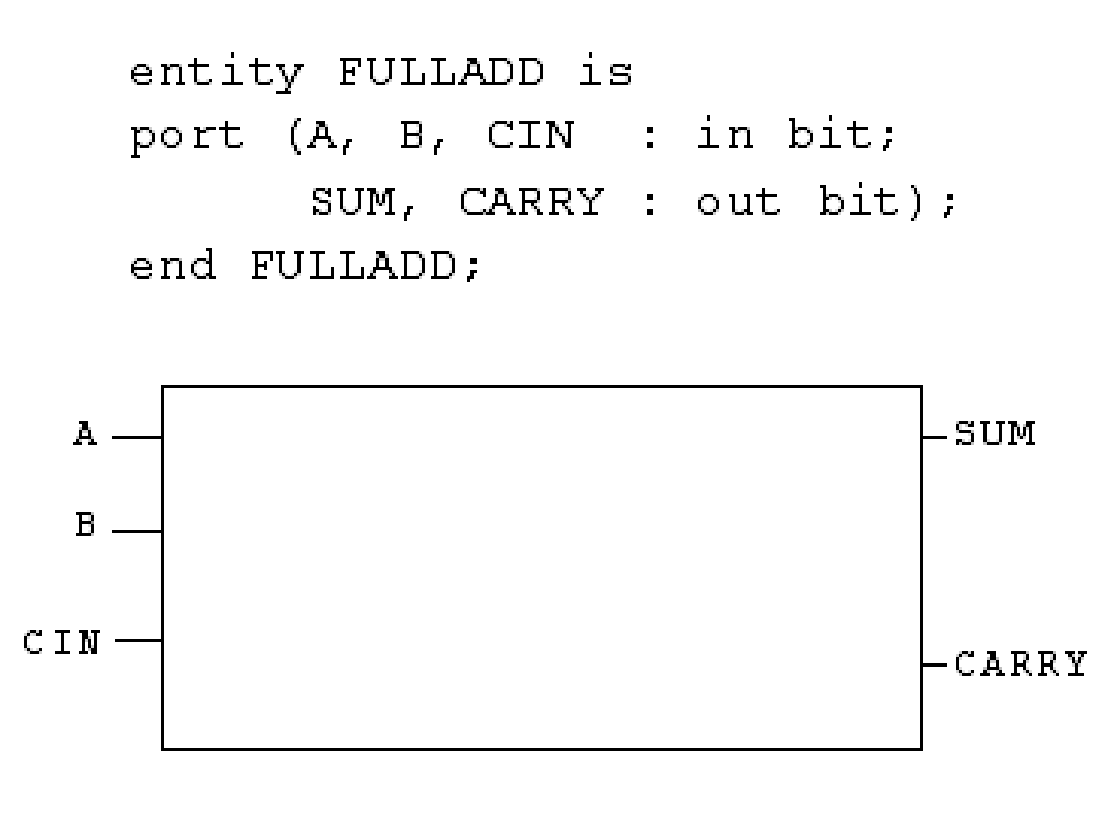

EntityЃЈЃЉЪЕЬх

Enitiy ЪЕЬхУћ is

PORT(ЖЫПкУћ1ЃЌЖЫПкУћNЃКЗНЯђЃКРраЭЃЉ

[ЖЫПкЫЕУї]

End Entity;

PortЕФЗНЯђга: IN , OUT, INOUT, BUFFER, LINKAGE

In аХКХжЛФмБЛв§гУ,ВЛФмБЛИГжЕЃЛВЛПЩвдГіЯждк<= Лђ : = ЕФзѓБп

out аХКХжЛФмБЛИГжЕ,ВЛФмБЛв§гУЃЛВЛПЩвдГіЯждк<= Лђ : = ЕФгвБп

buffer аХКХПЩвдБЛв§гУ,вВПЩвдБЛИГжЕЃЛПЩвдГіЯждк<= Лђ

: = ЕФСНБп

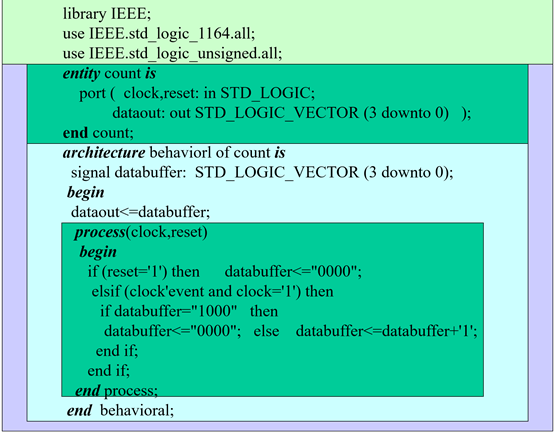

EntityЕФФкВПНсЙЙНЋгЩArchitectureРДУшЪі

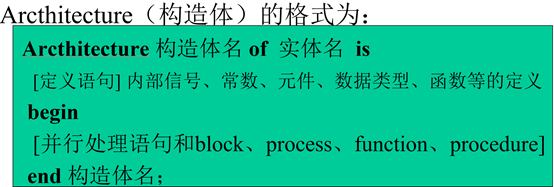

ArcthitectureЃЈЙЙдьЬхЃЉ

Arcthitecture ЙЙдьЬхУћ of ЪЕЬхУћ is

[ЖЈвхгяОф] ФкВПаХКХЁЂГЃЪ§ЁЂдЊМўЁЂЪ§ОнРраЭЁЂКЏЪ§ЕШЕФЖЈвх

begin

[ВЂааДІРэгяОфКЭblockЁЂprocessЁЂfunctionЁЂprocedure]

end ЙЙдьЬхУћЃЛ

Р§ШчЃК

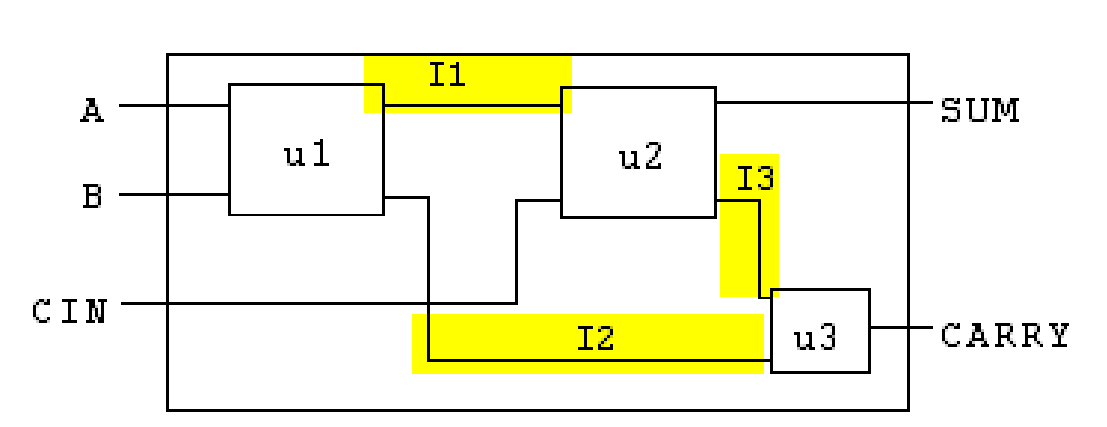

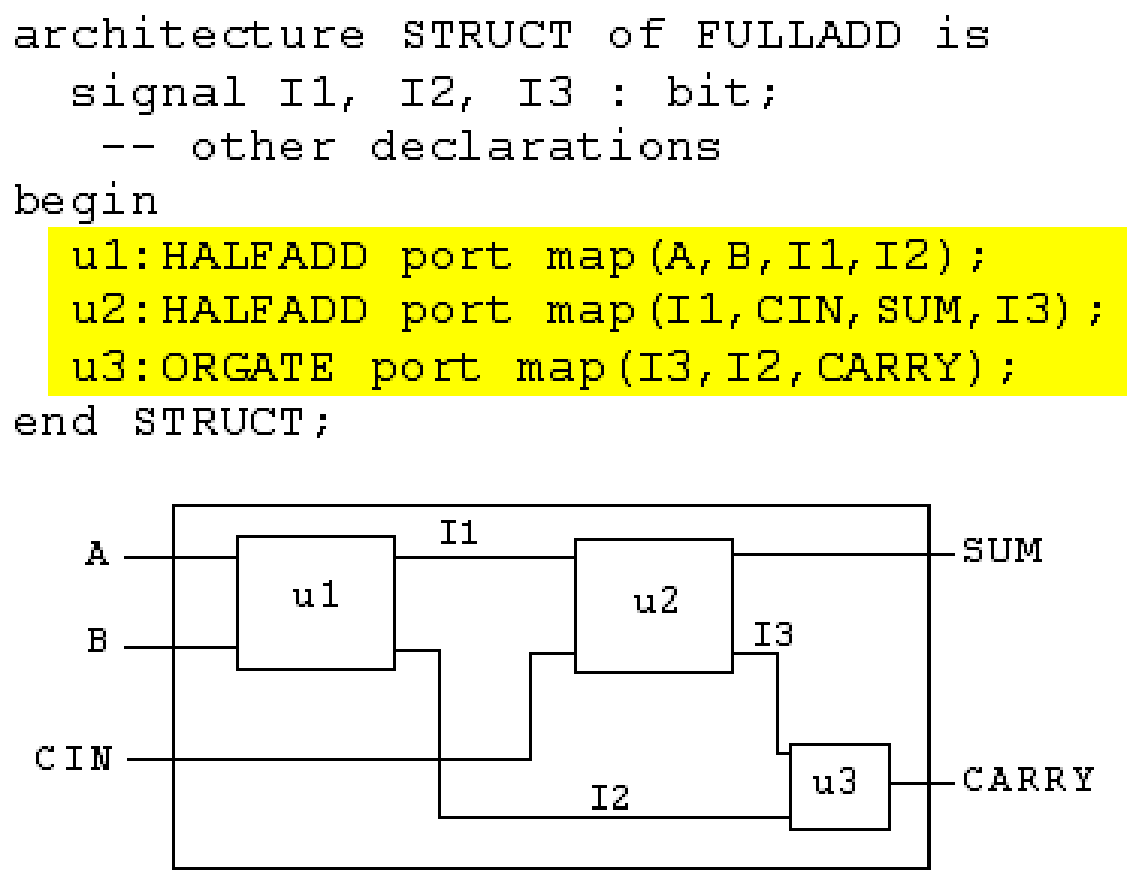

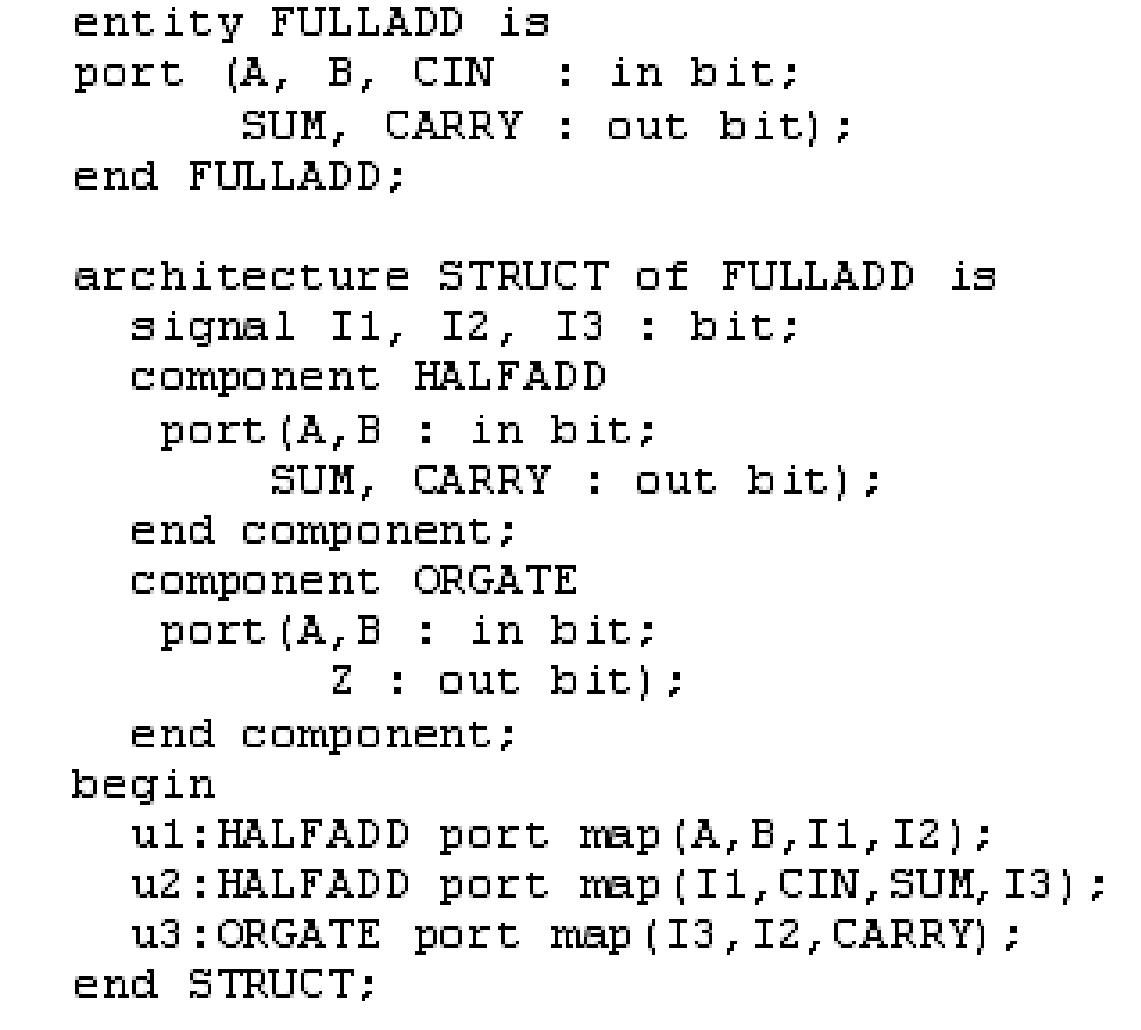

ЯТУцШУЮвУЧРДПДвЛПДШчКЮНЋвЛИіЪЕЬхЃЈFULLADDЃЉЙЙдьЮЊвЛИіФкВПФмЪЕ

ЯжЙІФмЕФЙЙдьЬхЃЈSTRUCTЃЉЃК

ЦфЫћЩшМЦЕЅдЊ

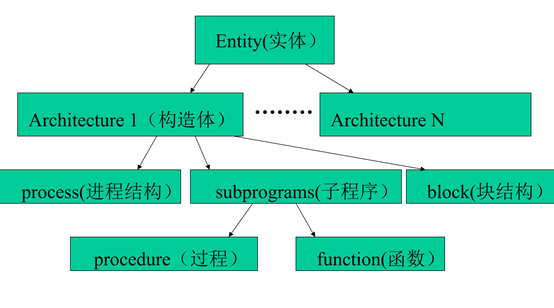

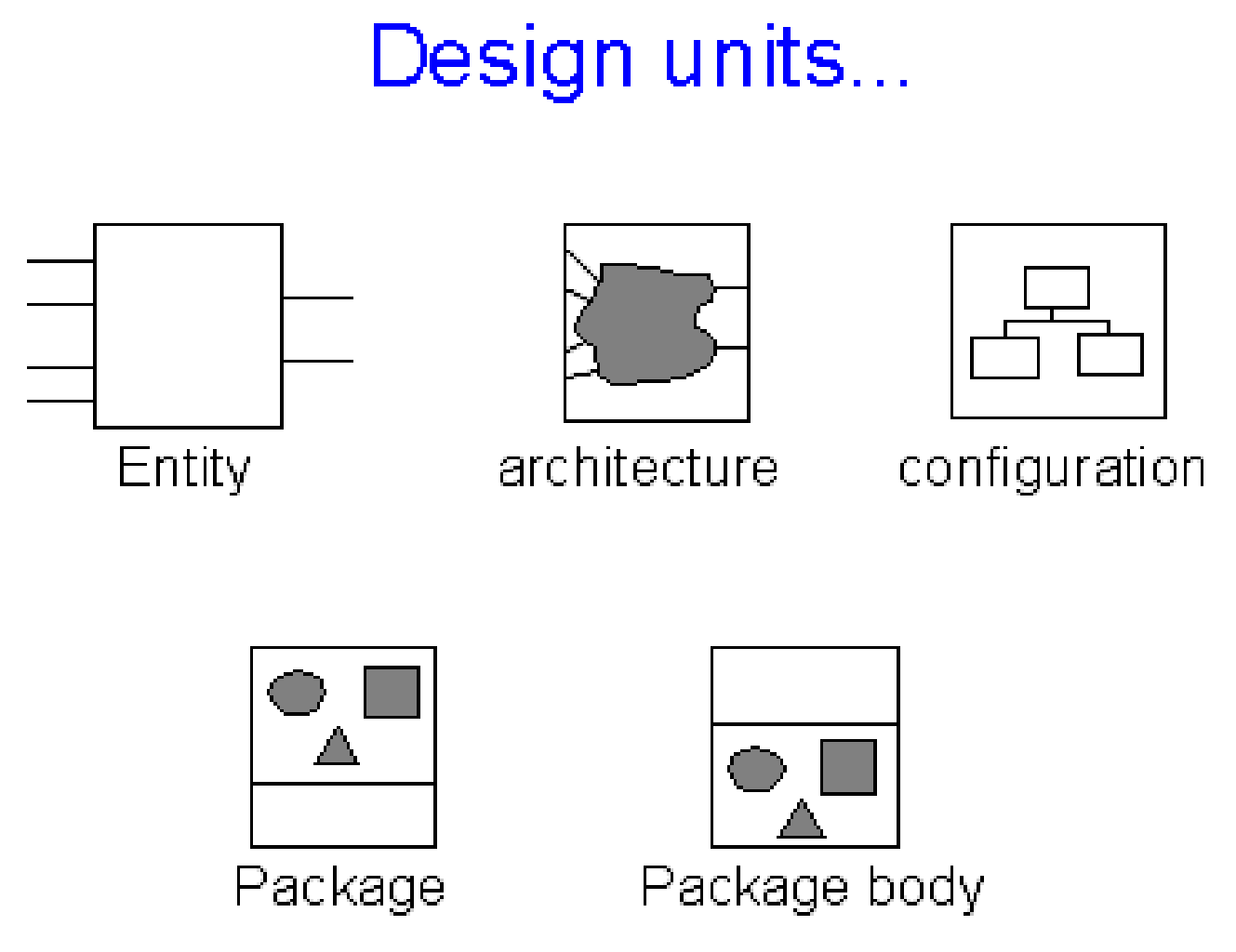

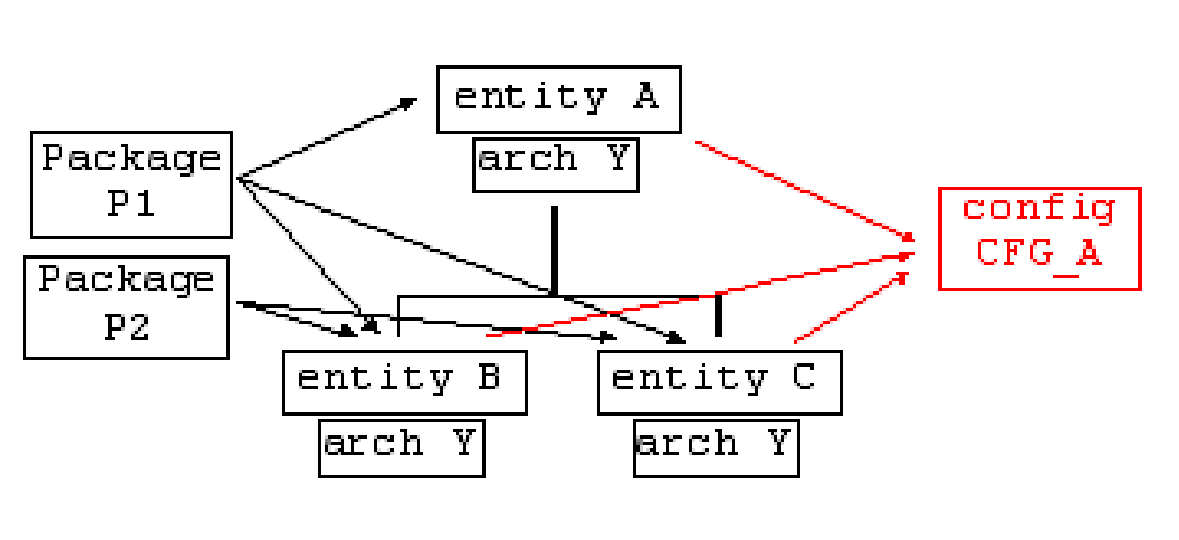

Г§СЫentity(ЪЕЬх)КЭarchitecture(ЙЙдьЬх)ЭтЛЙгаСэЭтШ§ИіПЩвдЖРСЂНјааБрвыЕФЩшМЦЕЅдЊ

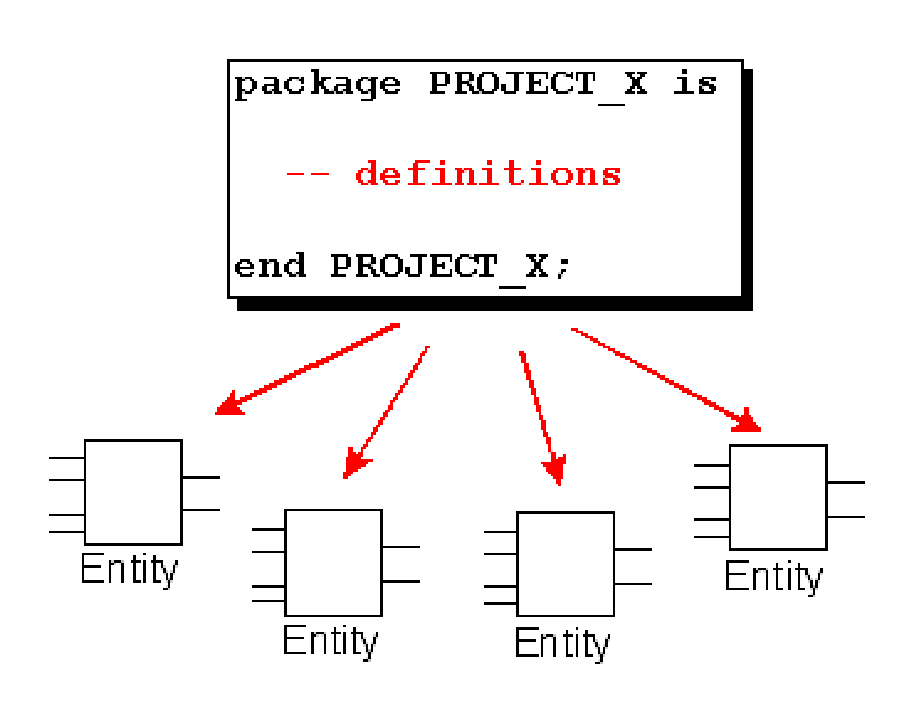

PackageЃЈАќМЏКЯЃЉЪєгкПтНсЙЙЕФвЛИіВуДЮЃЌДцЗХаХКХЖЈвхЁЂГЃЪ§ЖЈвхЁЂЪ§ОнРраЭЁЂдЊМўгяОфЁЂКЏЪ§ЖЈвхКЭЙ§ГЬЖЈвхЁЃ

Package BodyЃК ОпгаЖРСЂЖдЖЫПк(port)ЕФpackage

configurationЃЈХфжУЃЉУшЪіВугыВужЎМфЕФСЌНгЙиЯЕвдМАЪЕЬхгыЙЙдьЬхжЎМфЙиЯЕ

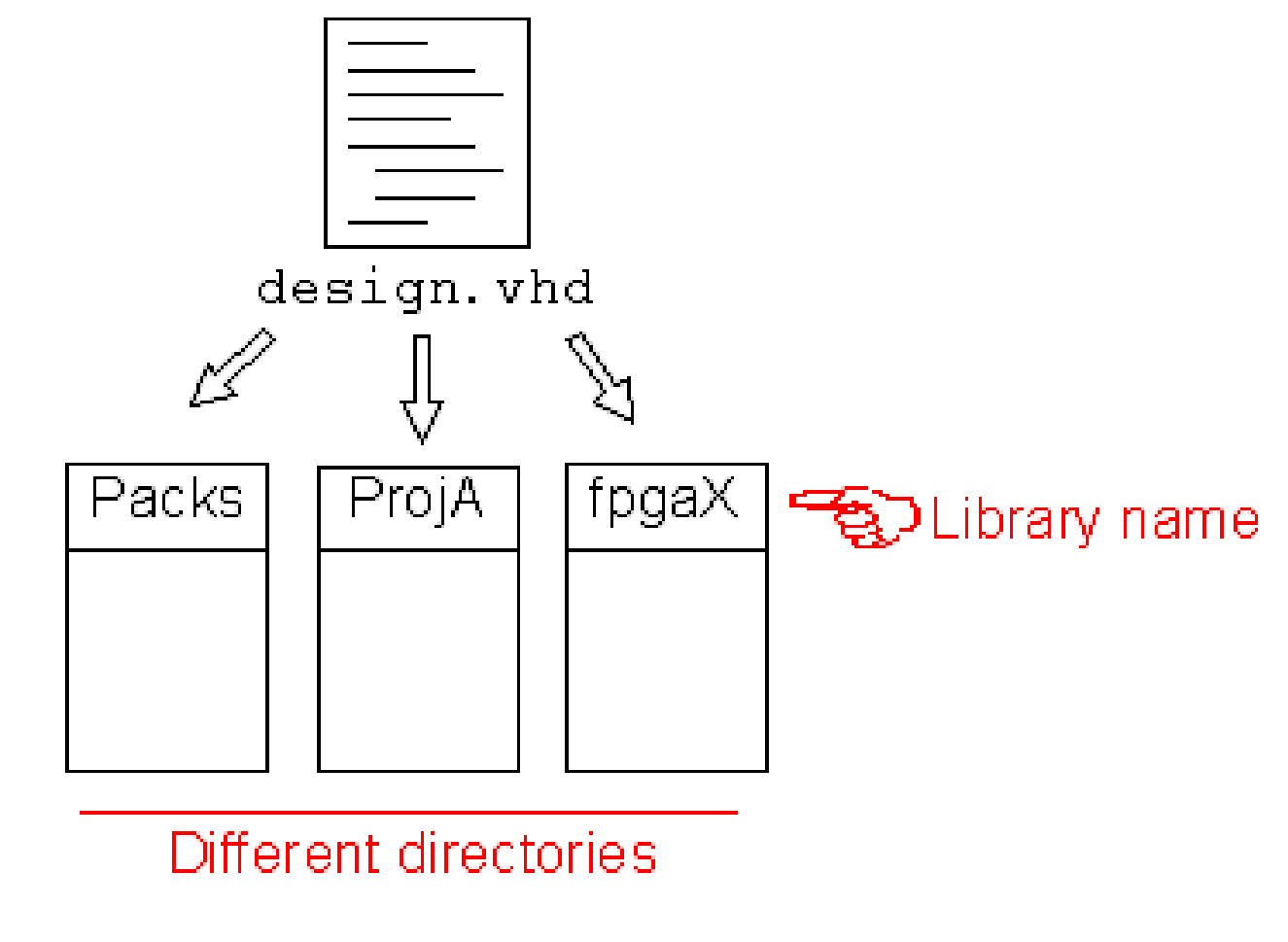

4ЁЂLibraryЃЈПтЃЉ

ПтЃК Ъ§ОнЕФМЏКЯЁЃФкКЌИїРрАќЖЈвхЁЂЪЕЬхЁЂЙЙдьЬхЕШ

STDПт --VHDLЕФБъзМПт

IEEEПт -- VHDLЕФБъзМПтЕФРЉеЙ

УцЯђASICЕФПт --ВЛЭЌЕФЙЄве

ВЛЭЌЙЋЫОздЖЈвхЕФПт

ЦеЭЈгУЛЇздМКЕФПт --ЕБVHDLЮФМўБЛБрвыКѓЃЌБрвыЕФНсЙћДЂДцдкЬиЖЈЕФФПТМЯТЃЌетИіФПТМЕФТпМУћГЦМДLibraryЃЌДЫФПТМЯТЕФФкШнврМДЪЧетИіLibraryЕФФкШнЁЃ

PackageЃЈАќЃЉ

етаЉНсЙЙжЎМфЕФЙиЯЕ

VHDLЖдЯѓЁЂВйзїЗћЁЂЪ§ОнРраЭ

1ЁЂVHDLжаЕФЖдЯѓЃЈЖдПЭЙлЪЕЬхЕФГщЯѓКЭИХРЈЃЉгаЃК

ConstantЃЈГЃСПЃЉдкГЬађжаВЛПЩвдБЛИГжЕ

VariableЃЈБфСПЃЉдкГЬађжаПЩвдБЛИГжЕ(гУ": =")ЃЌИГжЕКѓСЂМДБфЛЏЮЊаТжЕЁЃ

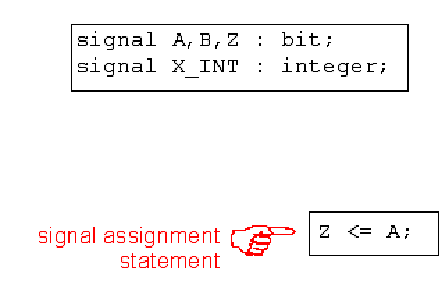

SignalЃЈаХКХЃЉдкГЬађжаПЩвдБЛИГжЕ(гУ"<=")

ЃЌЕЋВЛСЂМДИќаТЃЌЕБНјГЬЙвЦ№КѓЃЌВХПЊЪМИќаТЁЃ

Р§ШчЃК

variable

xЃЌyЃКintegerЃЛ--ЖЈвхСЫећЪ§аЭЕФБфСПЖдЯѓxЃЌy

constant

VccЃКrealЃЛ--ЖЈвхСЫЪЕЪ§аЭЕФГЃСПЖдЯѓVcc

signal

clkЃЌresetЃКbitЃЛ--ЖЈвхСЫЮЛРраЭЕФаХКХЖдЯѓclkЃЌreset

зЂвтЃК

1ЁЂvariableжЛФмЖЈвхдкprocessКЭsubprogramЃЈАќРЈfunctionКЭprocedureЃЉжаЃЌВЛПЩЖЈвддкЦфЭтВПЁЃ

2ЁЂsignalВЛФмЖЈвхдкprocessКЭsubprogramЃЈАќРЈfunctionКЭprocedureЃЉжаЃЌжЛПЩЖЈвддкЦфЭтВПЁЃ

ЖдЯѓЕФЪєадЃЈРрЫЦгкЦфЫќУцЯђЖдЯѓЕФБрГЬгябдШчVBЁЂVCЁЂDELPHIЃЉЃК

гУЗЈИёЪНЃКЖдЯѓ ' Ъєад

Р§згЃКclk'event --БэУїаХКХclkЕФeventЪєад

ГЃгУЕФЪєадЃК

Signal ЖдЯѓЕФГЃгУЪєадгаЃК

event ЃК ЗЕЛиbooleanжЕЃЌаХКХЗЂЩњБфЛЏЪБЗЕЛиtrue

last_valueЃКЗЕЛиаХКХЗЂЩњДЫДЮБфЛЏЧАЕФжЕ

last_eventЃКЗЕЛиЩЯвЛДЮаХКХЗЂЩњБфЛЏЕНЯждкБфЛЏЕФМфИєЪБМф

delayed[(ЪБбгжЕ)]: ЪЙаХКХВњЩњЙЬЖЈЪБМфЕФбгЪБВЂЗЕЛи

stable[(ЪБбгжЕ)]: ЗЕЛиboolean, аХКХдкЙцЖЈЪБМфФкУЛгаБфЛЏЗЕЛиtrue

transaction: ЗЕЛиbitРраЭЃЌаХКХУПЗЂЩњвЛДЮБфЛЏЃЌЗЕЛижЕЗзЊвЛДЮ

Р§згЃКA<=B'delayed(10 ns)ЃЛ --BбгЪБ10nsКѓИГИјAЃЛ

ifЃЈB'Stable(10 ns)ЃЉЃЛ --ХаЖЯBдк10nsжаЪЧЗёЗЂЩњБфЛЏ

гІгУЃК

аХКХЕФeventКЭlast_valueЪєадОГЃгУРДШЗЖЈаХКХЕФБпби

Р§згЃК

ХаЖЯclkЕФЩЯЩ§би

if ЃЈ (clk'event)and (clk='1') and(clk'last_value='0')ЃЉ

then

ХаЖЯclkЕФЯТНЕби

if ЃЈ (clk'event)and (clk='0') and(clk'last_value='1')ЃЉ

then

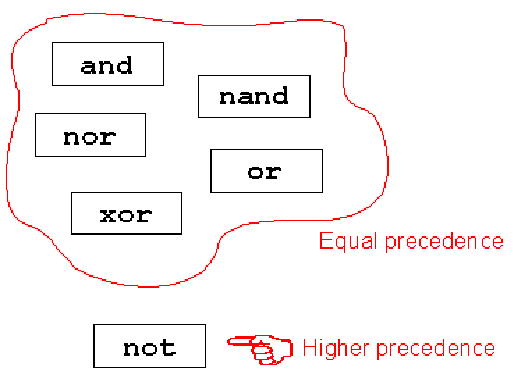

2ЁЂVHDLЕФЛљБОЃЈЪ§ОнЃЉРраЭ

bit(ЮЛ)ЃК `0` КЭ`1`

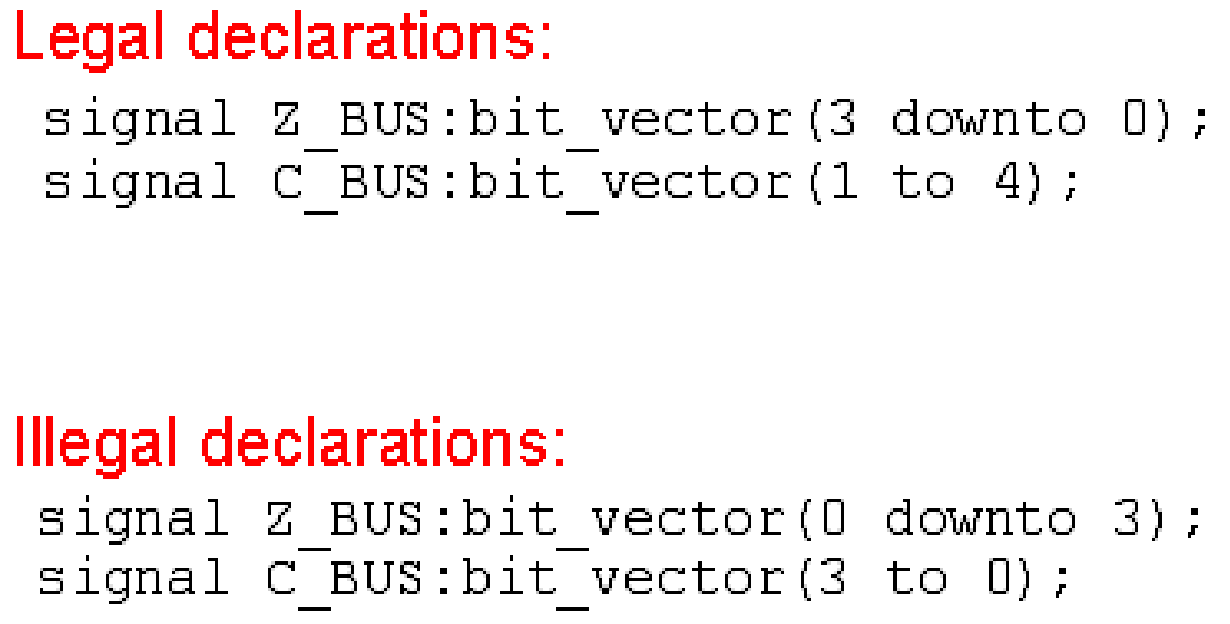

bit-Vector(ЮЛЪИСП)ЃК Р§ШчЃК``00110``

Boolean " ture"КЭ"false"

time Р§ШчЃК1 usЁЂ100 msЃЌ3 s

character Р§ШчЃК'a'ЁЂ'n'ЁЂ'1'ЁЂ '0'

string Р§ШчЃК"sdfsd"ЁЂ"my design"

integer 32ЮЛР§ШчЃК1ЁЂ234ЁЂ-2134234

real ЗЖЮЇ-1.0E38~+1.0E38 Р§ШчЃК1.0ЁЂ2.834ЁЂ3.14ЁЂ0.0

natural здШЛЪ§ КЭ positive е§ећЪ§

senverity level ЃЈГЃКЭassertгяОфХфКЯЪЙгУЃЉАќКЌгаЃКnoteЁЂwarningЁЂerrorЁЂfailure

вдЩЯЪЎжжРраЭЪЧVHDLжаЕФБъзМРраЭЃЌдкБрГЬжаПЩвджБНгЪЙгУЁЃЪЙгУетЪЎжжвдЭтЕФРраЭЃЌашвЊздааЖЈвхЛђжИУїЫљв§гУЕФLibrary(Пт)КЭPackage(Аќ)МЏКЯ

Р§згЃК

ЃЈ1ЃЉ

ЃЈ2ЃЉ

ЃЈ3ЃЉ

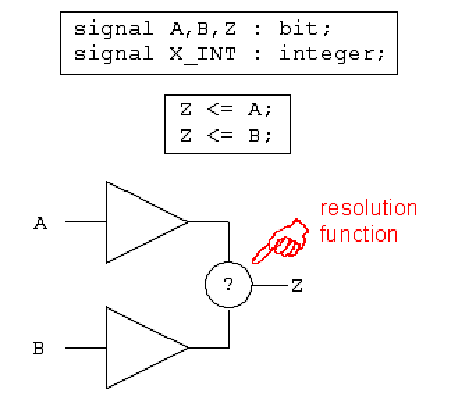

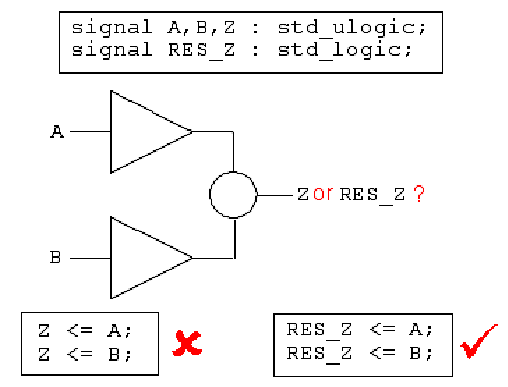

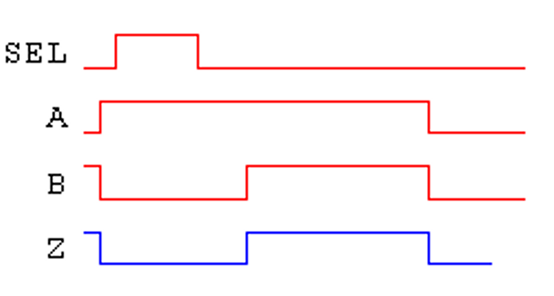

аХКХZгаСНИіЧ§ЖЏAКЭBЃЛZБиаыЖЈвхЮЊвЛжжаТЕФЪ§ОнРраЭЃЌЗёдђZНЋЮоЗЈОіЖЈШЁжЕЃЌгяОфЪгЮЊЗЧЗЈЁЃ

ЃЈ4ЃЉ

ЃЈ5ЃЉ

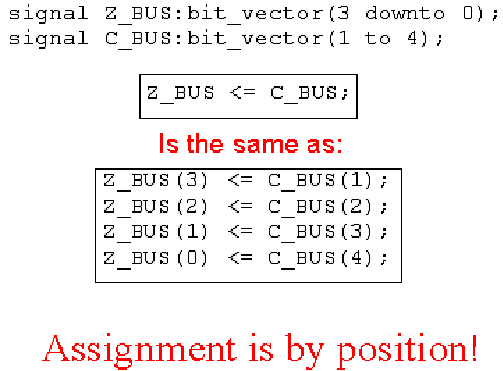

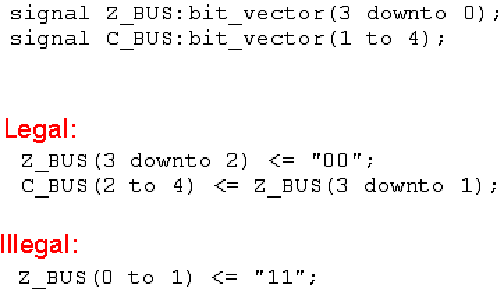

вЊЕуЃКИГжЕгяОфжаЕФЗНЯђгІКЭЩљУїжаЕФЗНЯђвЛбљ

3ЁЂГЃгУВйзї

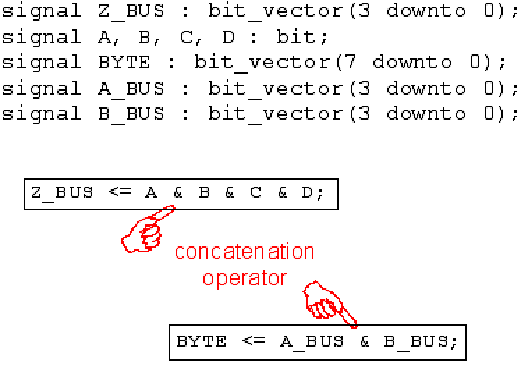

СЌНгВйзїЗћ---&

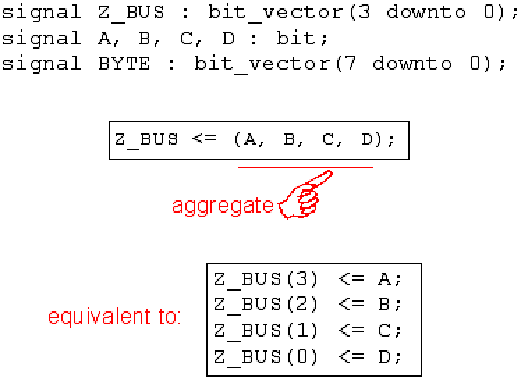

МЏКЯВйзї---ЃЈЃЉ

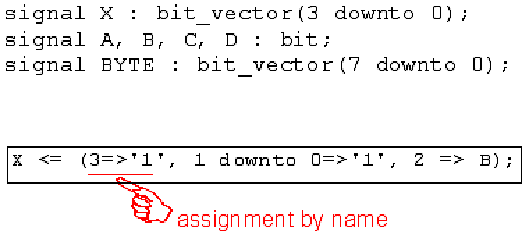

МЏКЯВйзї---ађКХ

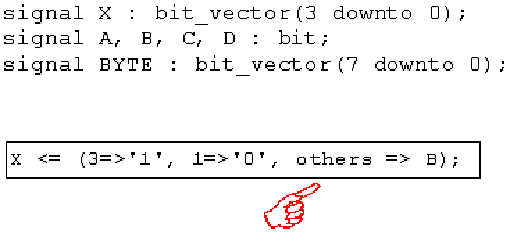

МЏКЯВйзї--ВЩгУothers

ЖЈвхздМКЕФРраЭ

ЭЈгУИёЪН

TYPE РраЭУћ IS Ъ§ОнРраЭЖЈвх

гУЛЇПЩвдЖЈвхЕФЪ§ОнРраЭЃК

УЖОйРраЭenumberatedЁЂећЪ§аЭintegerЁЂ

ЪЕЪ§аЭrealЁЂЪ§зщРраЭarrayЁЂ

МЭТМРраЭrecordЁЂЪБМфРраЭtimeЁЂ

ЮФМўРраЭfileЁЂДцШЁРраЭaccess

ЃЈ1ЃЉ

УЖОйРраЭenumberated

ИёЪН

type Ъ§ОнРраЭУћ is ЃЈдЊЫиЃЌдЊЫиЁ...ЃЉ;

Р§зг

type week is (sun,mon,tue,thu,fri,sat);

type std_logic is ('1','0','x','z');

ЃЈ2ЃЉ

ећЪ§РрintegerКЭЪЕЪ§Ррreal

ИёЪН

type Ъ§ОнРраЭУћ is Ъ§ОнРраЭЖЈвх дМЪјЗЖЮЇ;

Р§зг

type week is integer range 1 to 7;

type current is real range -1E4 to 1E4

ЃЈ3ЃЉ

Ъ§зщРраЭarray

ИёЪН

type Ъ§ОнРраЭУћ is array ЗЖЮЇ of дЊЪ§ОнРраЭУћ

Р§зг

type week is array (1 to 7) of integer;

type deweek is array (1 to 7) of week;

ЃЈ4ЃЉ

ЪБМфРраЭtime

ИёЪН

type Ъ§ОнРраЭУћ is ЗЖЮЇ

units ЛљБОЕЅЮЛ;

ЕЅЮЛ;

end units

Р§зг

type time is range -1E18 to 1E18

units

us;

ms=1000 us;

sec=1000 ms;

min=60 sec;

end units

зЂвтЃКв§гУЪБМфЪБЃЌгаЕФБрвыЦївЊЧѓСП гыЕЅЮЛ жЎМфгІгавЛИіПеИёШчЃК1 nsЃЛВЛФмаДЮЊ1ns

ЃЈ5ЃЉ

МЭТМРраЭrecord

ИёЪН

type Ъ§ОнРраЭУћ is record

дЊЫиУћ:Ъ§ОнРраЭУћ;

дЊЫиУћ:Ъ§ОнРраЭУћ;

Ё.

end record;

Р§зг

type order is record

id:integer;

date:string;

security:boolean;

end record;

в§гУ:signal flag:boolean;

signal order1:order;

order1<=(3423,"1999/07/07",true);

flag<=order1.security;

IEEE 1164жаЖЈвхЕФРраЭ

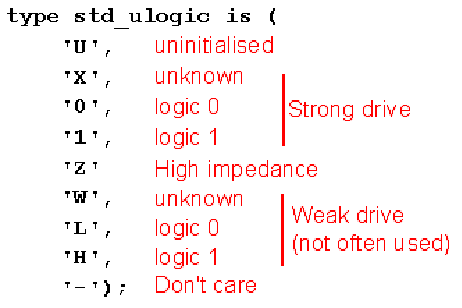

ЃЈ1ЃЉstd_ulogic ЪЧЖдЮЛ(bit)РраЭЕФРЉеЙ,жЛдЪаэвЛИіЧ§ЖЏдД

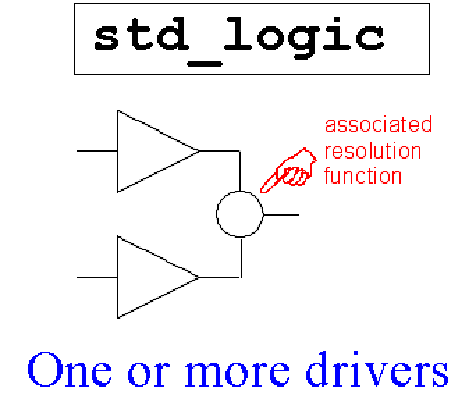

ЃЈ2ЃЉStd_logicЭЌstd_ulogic вЛбљгаОХИізДЬЌ,дЪаэвЛИіЛђЖрИіЧ§ЖЏдД

гыstd_ulogicЕФЧјБ№

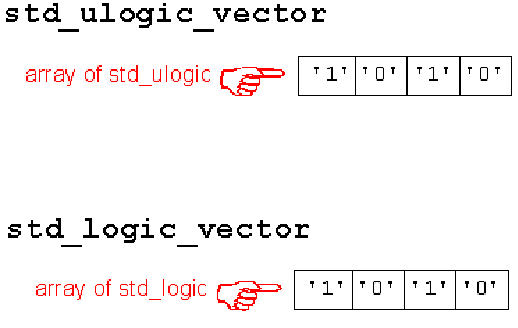

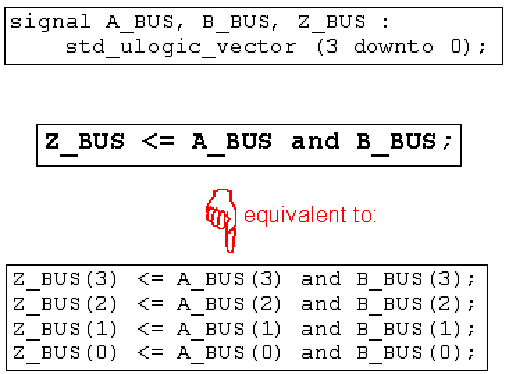

ЃЈ3ЃЉStd_unlogic_vectorКЭstd_logic_vector

Std_unlogicЁЂstd_ulogic_vector

std_logic_vectorКЭ std_unlogic_vector РраЭ

ОљЖЈвхдкpackage(Аќ) standard_logic_1164жа

дкЪЙгУетЫФжжРраЮЪБгІМгвдЫЕУї,

Р§Шч:library ieee;

use ieee.std_logic_1164.all;

VHDLжаЕФВйзїЗћ

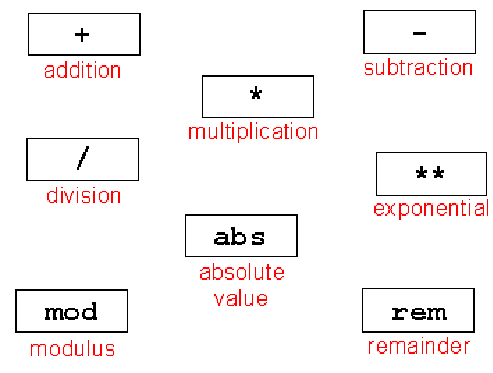

ЃЈ1ЃЉТпМВйзїЗћгаЃК

ЃЈ2ЃЉТпМВйзїЗћЕФгІгУР§зг

ЃЈ3ЃЉЙиЯЕдЫЫуЗћга

ЃЈ4ЃЉЙиЯЕдЫЫуЗћЕФгІгУ

ЃЈ5ЃЉЪ§бЇдЫЫуЗћ

зЂвт:ЩЯЪідЫЫуЗћгІгУгк integerЃЌrealЃЌtime РраЭЃЌВЛФмгУгкvector(ШчЙћЯЃЭћгУгкvector,ПЩвдЪЙгУПтIEEEЕФstd_logic_unsignedАќ,ЫќЖдЫуЪѕдЫЫуЗћНјааСЫРЉеЙ)

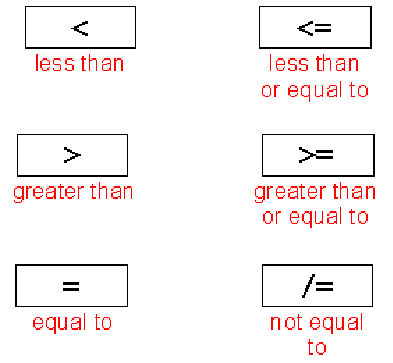

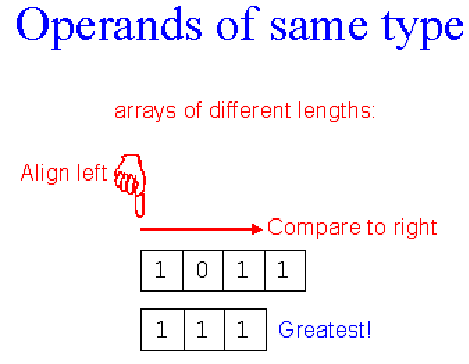

(6)VHDLжаЕФВйзїЗћгІгУвЊЕу

VHDLЪєгкЧПРраЭЃЌВЛЭЌРраЭжЎМфВЛФмНјаадЫЫуКЭИГжЕЃЌПЩвдНјааЪ§ОнРраЭзЊЛЛ

vectorВЛБэЪОnumber

array ВЛБэЪОnumber

VHDLжаЕФПижЦгяОфМАФЃПщ

ЛљБОИХФю

ВЂааДІРэЃЈconcurrentЃЉЃКгяОфЕФжДаагыЪщаДЫГађЮоЙиЃЌВЂааПщФкЕФгяОфЪБЭЌЪБжДааЕФ

ЫГађДІРэЃЈsequentialЃЉЃК гяОфЕФжДааАДЪщаДЕФЯШКѓДЮађЃЌДгЧАЕНКѓЫГађжДааЁЃетжжЗНЪНКЭЦфЫћЦеЭЈБрГЬгябд(ШчcЃЌpascal)ЪЧвЛбљЕФЁЃ

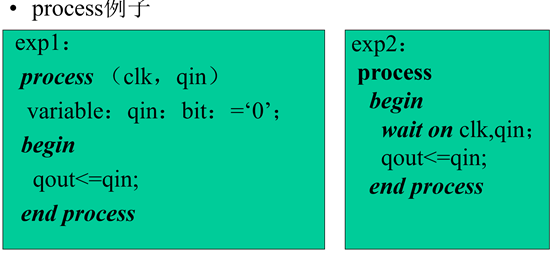

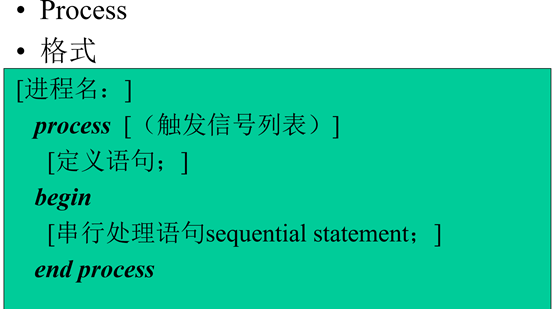

2ЁЂВЂааКЭЫГађДІРэдкvhdlжаЕФгІгУ

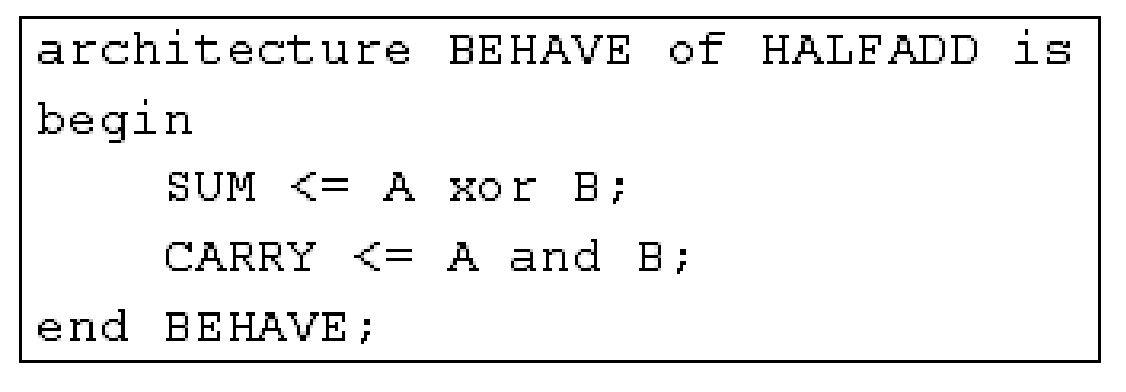

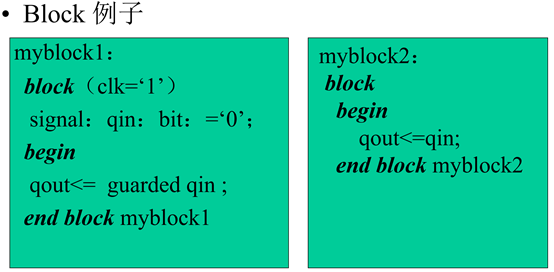

ЃЈ1ЃЉArchitecture жаЕФгяОфМАзгФЃПщжЎМфЪЧВЂааДІРэЕФ

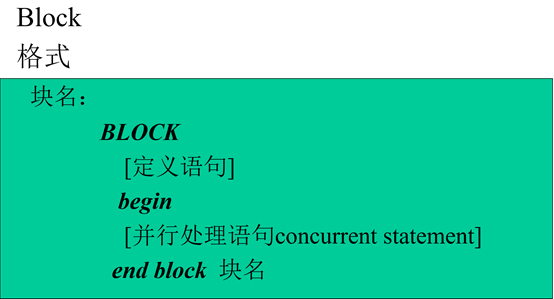

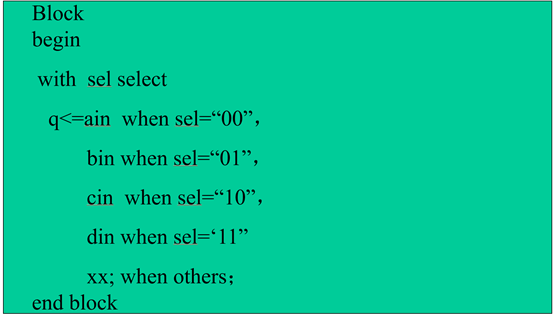

ЃЈ2ЃЉзгФЃПщblockжаЕФгяОфЪЧВЂааДІРэЕФ

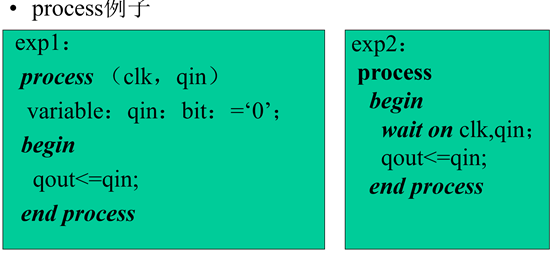

ЃЈ3ЃЉзгФЃПщprocessжаЕФгяОфЪЧЫГађДІРэЕФ

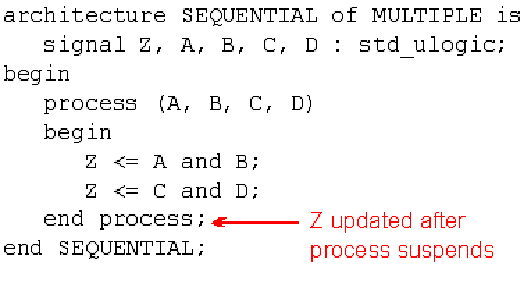

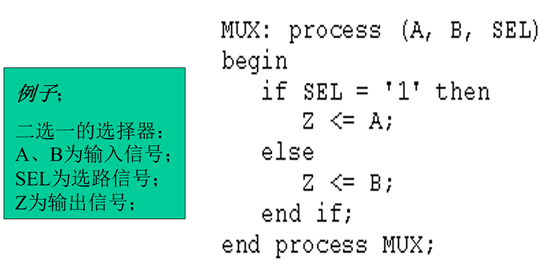

processР§зг-жЕЕФИќаТ

ЗжЮіЃК

ЕБAЁЂBЁЂCЁЂDжаШЮвЛаХКХЗЂЩњБфЛЏЪБЃЌНјГЬНЋПЊЪМжДааЃЌЕБжДаа Z <=

A and B Кѓ, Z ЕФжЕВЛЛсСЂМДБфЛЏ ЃЛЭЌРэжДаа Z <= C and D КѓZ ЕФжЕвВВЛЛсСЂМДБфЛЏЁЃЕБжДааend

processКѓЃЌ Z ЕФжЕВХПЊЪМИќаТЃЌЭЌЪБЯЕЭГЙвЦ№ПЊЪМЕШД§УєИааХКХЁЃ

ProcessжаУєИааХКХСаБэЕФЦеБщддђЪЧЃК

дкprocessжаЃЌЦфжЕБЛв§гУЕФаХКХгІЕБГіЯждкУєИааХКХСаБэжа

ЗДР§ЃК

ПЩМћВЛЗћКЭЩшМЦвЊЧѓ

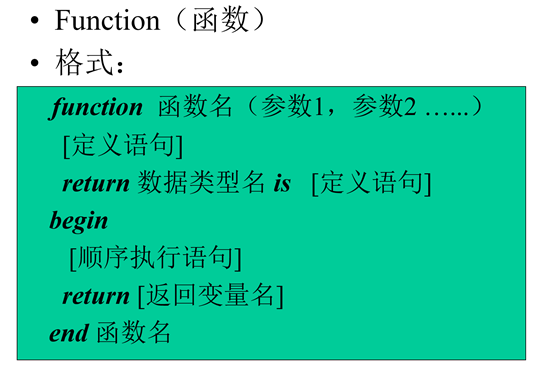

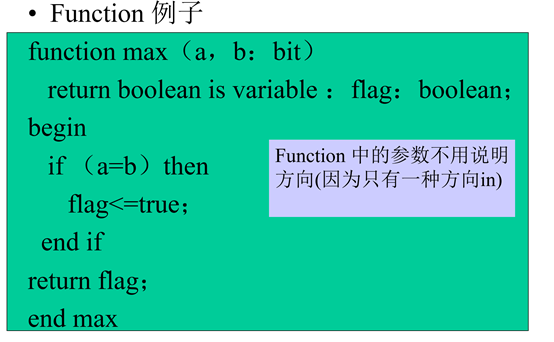

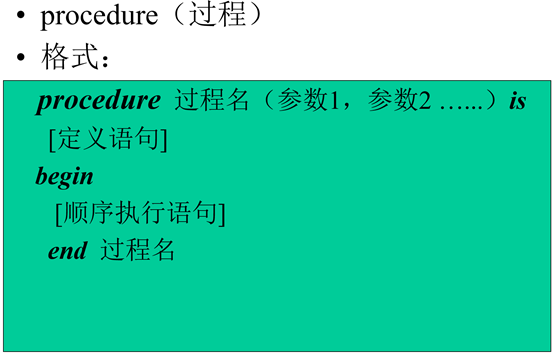

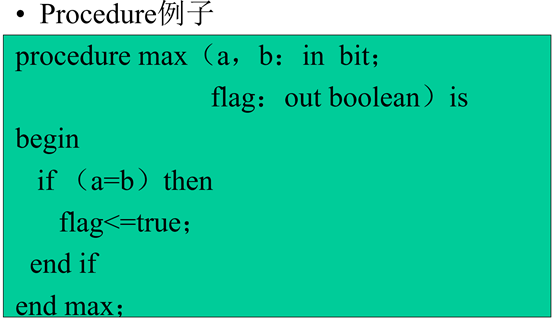

ЃЈ4ЃЉзгФЃПщsubprogramжаЕФfunctionКЭprocedureЪЧЫГађДІРэЕФ

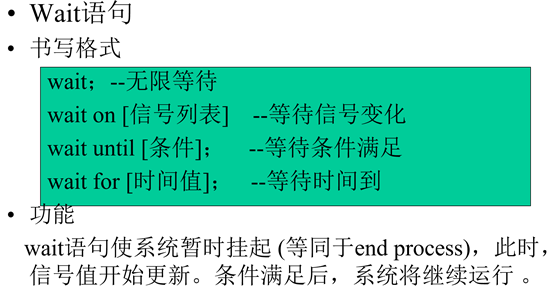

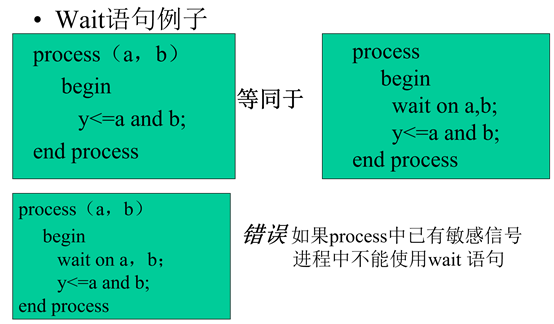

ЫГађжДаагяОфЃЈsequential statementЃЉ

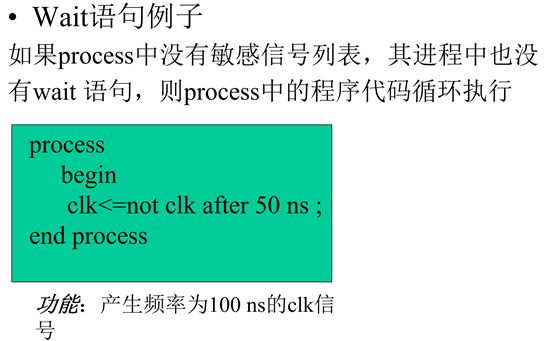

WaitгяОф

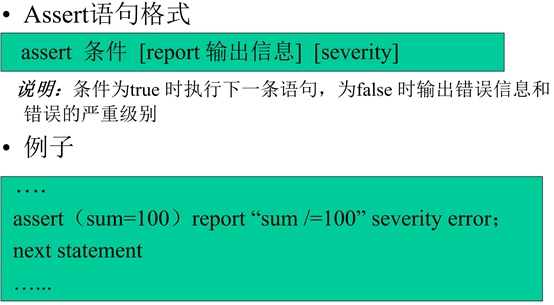

assertгяОф

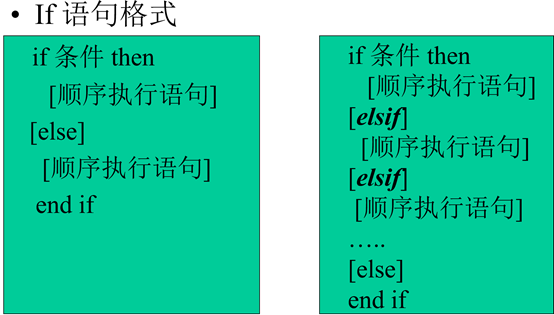

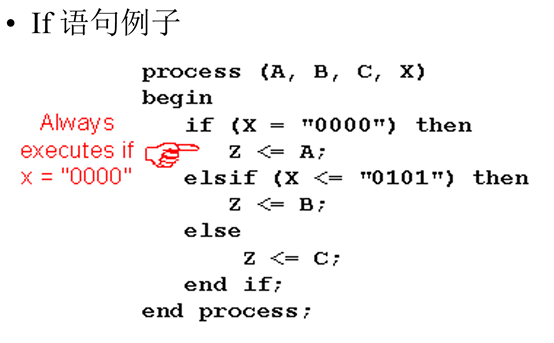

If гяОф

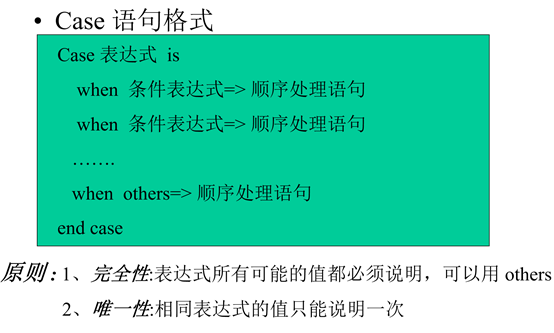

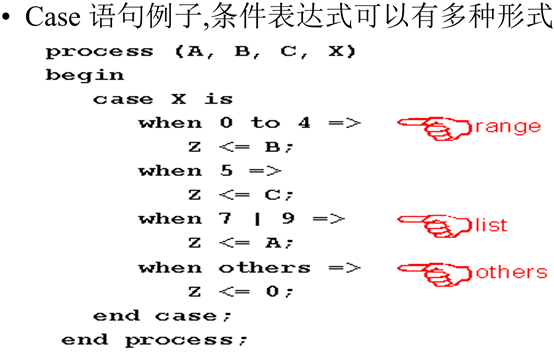

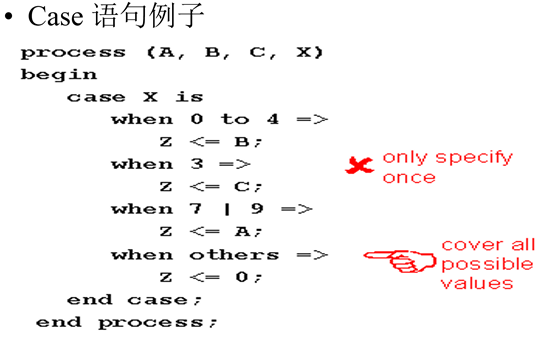

caseгяОф

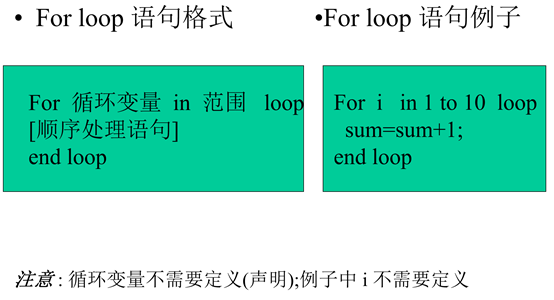

for loopгяОф

while гяОф

ВЂааДІРэгяОфЃЈconcurrent statementЃЉ

ВЂааВйзїжаЕФаХКХИГжЕ

аХКХИГжЕВйзї

ЗћКХ"<="НјаааХКХИГжЕВйзїЕФЃЌ

ЫќПЩвдгУдкЫГађжДаагяОфжаЃЌ

вВПЩвдгУдкВЂааДІРэгяОфжа

зЂвт

*гУдкВЂааДІРэгяОфжаЪБЃЌЗћКХ<=гвБпЕФжЕЪЧДЫЬѕгяОфЕФУєИааХКХЃЌМДЗћКХ<=гвБпЕФжЕЗЂЩњБфЛЏОЭЛсжиаТМЄЗЂДЫЬѕИГжЕгяОфЃЌвВМДЗћКХ<=гвБпЕФжЕВЛБфЛЏЪБЃЌДЫЬѕИГжЕгяОфОЭВЛЛсжДааЁЃШчЙћЗћКХ<=гвБпЪЧГЃЪ§дђИГжЕгяОфвЛжБжДааЁЃ

*гУдкЫГађжДаагяОфжаЪБЃЌУЛгавдЩЯЫЕЗЈЁЃ

бЁдёаХКХДјШыгяОфИёЪН

with БэДяЪН select

ФПЕФаХКХСП <= БэДяЪН1 when ЬѕМў1ЃЌ

БэДяЪН2 when ЬѕМў2ЃЌ

Ё..

БэДяЪНn when ЬѕМўnЃЛ

бЁдёаХКХДјШыгяОфР§зг

ЫГађжДаагяОфКЭВЂааДІРэгяОфзмНс

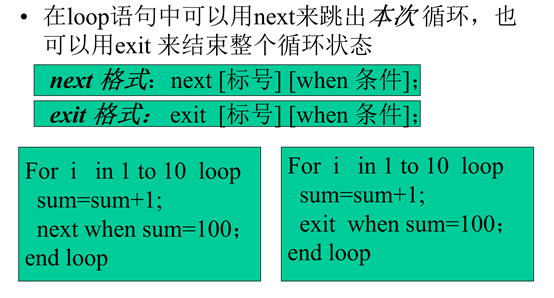

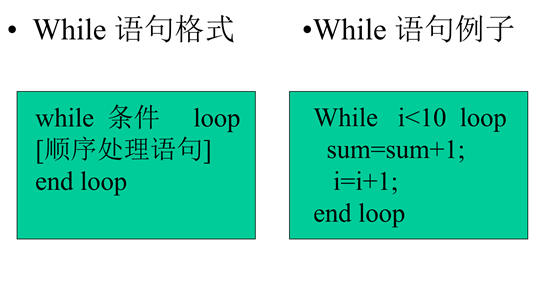

1ЁЂЫГађжДаагяОф waitЁЂassertЁЂif -else ЁЂcaseЁЂfor-loopЁЂwhileгяОфжЛФмгУдкprocessЁЂfunction

КЭ procedure жаЃЛ

2ЁЂВЂааДІРэгяОфЃЈЬѕМўаХКХДјШыКЭбЁдёаХКХДјШыЃЉжЛФмгУдкarchitectureЁЂblockжаЃЛ

ЦфЫќгяОф

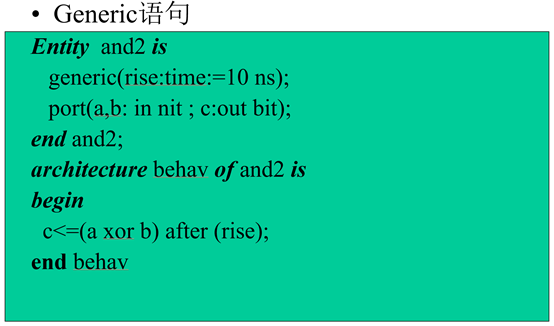

Р§згЃК

entity testand2 is

port(ain,bin: in nit ; cout:out bit);

end testand2;

architecture behav of testand2 is

component and2

generic(rise:time); port(a,b: in nit ; c:out bit);

end component;

begin

c<=(a xor b) after (rise);

u0:and2 generic map(20 ns) port map(ain,bin,cout);

end behav

|