| 编辑推荐: |

本文详细介绍了MIPI、eDP和OLDI/LVDS等汽车座舱系统的板内视频信号通信协议,希望对您的学习有所帮助。

本文来自于星辰汽车电子,由火龙果软件Linda编辑、推荐。 |

|

背景

在智能座舱的发展历程中,显示屏的个数越来越多,分辨率和显示屏的尺寸也越来越大。这已经是不可逆转的趋势。传统的座舱显示屏需要一颗主芯片支持一块屏幕,这在功能上和成本上都不是很好的做法。最新的智能座舱解决方案中,一芯多屏是必须要支持的功能,区别在于采用什么样的技术途径。

之前的文章介绍了远程视频信号传输协议GSML和FPD-LINK,这些信号主要用在ECU之间的信号传输。本文主要介绍板内视频信号传输协议MIPI、DP和OLDI/LVDS等信号的介绍。

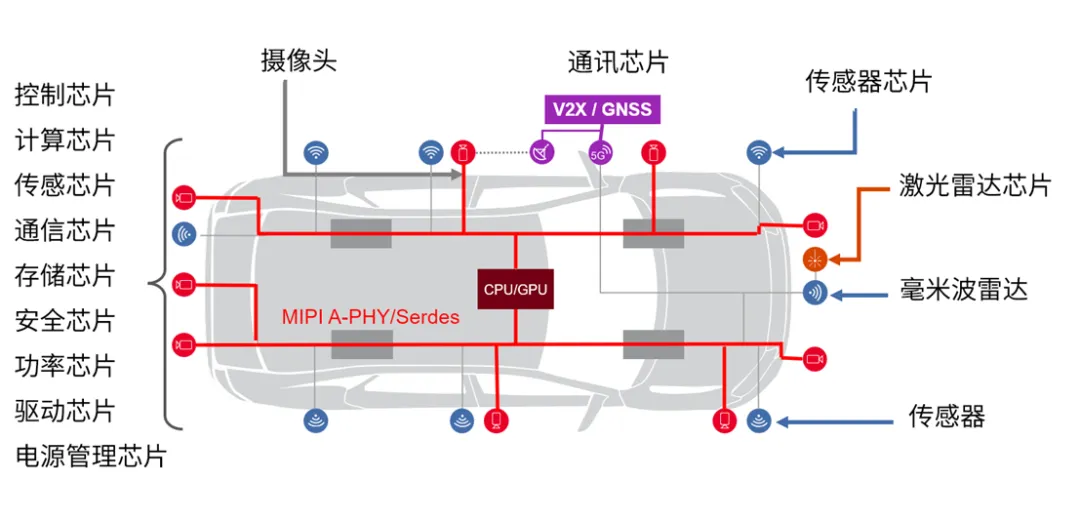

图1:ADAS系统与摄像头互联示意图

座舱视频架构

根据最新智能座舱发展的趋势来看,车载显示屏硬件技术需要支持一芯多屏。使用一颗CDC座舱芯片,要尽可能地满足如上所述多个显示屏的显示要求。这样一来,可以尽可能地节省成本和功耗。将原来需要多颗芯片才能支持的屏幕功能,尽量集成到一颗高性能的SOC芯片上来,是当前智能座舱发展的客观需求。

一种符合智能座舱CDC一芯多屏需求的车载显示屏的基本架构如下图所示:

图2:座舱视频总线示意图

MIPI(Mobile Industry Processor Interface)信号介绍

MIPI全称为:Mobile Industry Processor Interface,由MIPI联盟开发,是一种高性能、低功耗、低成本的串行通信接口,目的是把设备内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少设备设计的复杂程度和增加设计灵活性。统一接口标准的好处是厂商可根据需要灵活选择不同的芯片和模组,更改设计和功能非常快捷方便,MIPI主要用于移动设备和嵌入式设备中,比如手机、电脑、车载娱乐系统、可穿戴设备及物联网(IoT)设备等。

MIPI Alliance即移动产业处理器接口联盟(Mobile Industry Processor

Interface简称MIPI)。于2003 年由ARM,Nokia,ST,TI 等公司成立的为移动应用处理器制定的开放标准和一个规范,目前MIPI已经成为移动领域最主流的视频传输接口规范,应用最广泛的是MIPI

D-PHY和MIPI C-PHY两组协议簇,C-PHY中的许多模块借鉴于D-PHY,两种标准的接口可共用相同引脚实现双模。

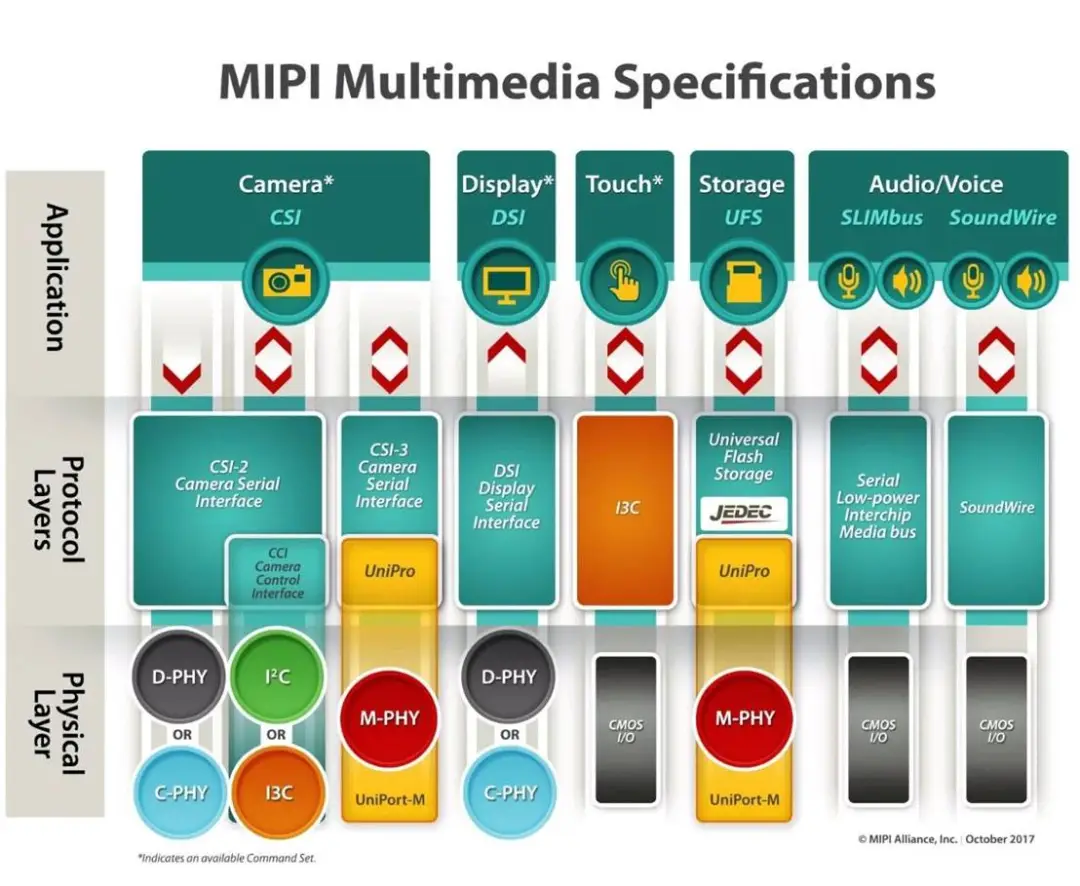

图3:MIPI总线框架图

MIPI总线框架,按照应用层、协议层、物理层三个部分划分。

应用层:功能模块使用MIPI总线进行数据传输,MIPI总线作为通信的功能模块如:摄像头、显示屏、触摸屏、存储、音频等。每个模块都会对在应用层对数据进行编码和解析。比如成熟的接口应用,MIPI-DSI(display

serial interface)用于显示屏,MIPI-CSI(camera serial interface)用于摄像头。

协议层:主要进行数据组包、按照规范增加包头/包尾、传输通道管理。

物理层:由PHY硬件模块组成,直接涉及到物理PIN连线。

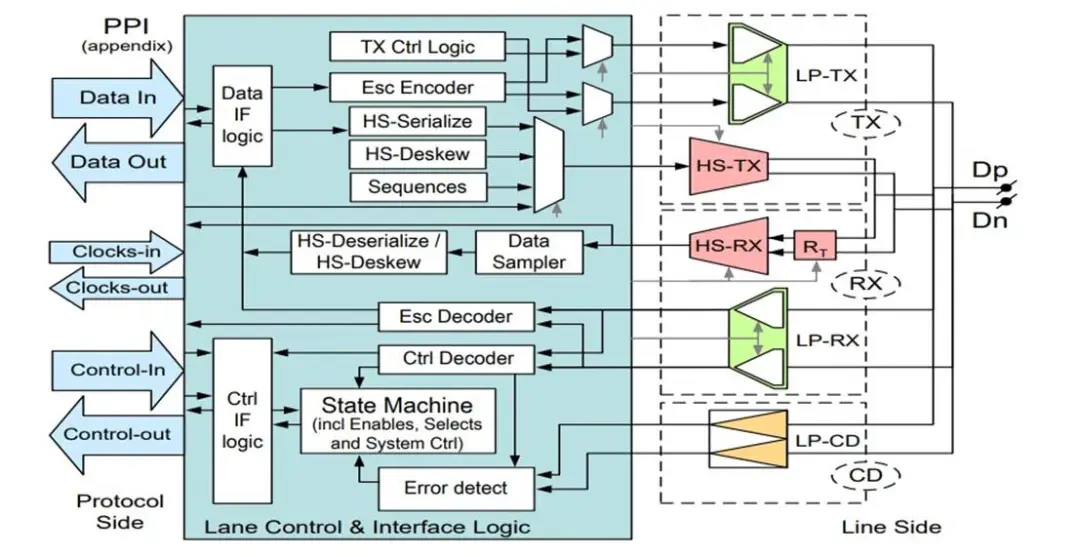

1. MIPI信号的物理PHY介绍

MIPI信号物理层的PHY类型D-PHY,C-PHY,M-PHY,最成熟应用最多的是D-PHY,D-PHY支持DSI和CSI。

- D-PHY:DDR源同步时钟双采样(上升沿和下降沿同时采样)、1组时钟lane、1~4组数据lane,1.0版本lane最大传输速度1Gbps。差分信号每组lane由2pin组成。

- C-PHY:内部时钟源、1~3组lane,lane最大传输速度5.7Gbps,每组lane由3pin组成。

- M-PHY:受限外围器件的发展速度,应用使用的比较少,最大传输速度11.6Gbps。

MIPI C-PHY和 D-PHY:这两种物理层接口标准定义了数据传输的物理层,支持高速的数据传输,D-PHY主要用于DSI和CSI接口,C-PHY则用于更高带宽的应用。MIPI

M-PHY适用于支持超高速存储与外设互联(如UFS、PCIe),适用于汽车与数据中心。

2. MIPI D-PHY(D-PHY协议)

协议概述

MIPI D-PHY是MIPI协议中的一种物理层接口,广泛应用于智能手机、汽车等领域的显示和相机系统。它支持高速的串行数据传输,传输速率最高可达到9

Gbps(标准通道)和11 Gbps(短通道)。D-PHY协议采用差分信号传输,以确保高效的数据传输和低功耗。

D-PHY协议的参数分析

传输速率:D-PHY v3.0标准的传输速率高达9 Gbps(标准通道)和11 Gbps(短通道)。这一速率能够支持现代高清显示和高分辨率图像传感器的需求。

功耗:D-PHY协议非常注重功耗管理,采用低功耗设计来延长设备的使用寿命。其功耗主要由传输数据的速率和传输的距离决定。

传输距离:D-PHY协议的最大传输距离与所选的线材、信号质量和速率有关。一般来说,短通道的传输距离较短,但能够支持更高的传输速率。

线数:D-PHY支持1到4个数据通道,根据不同的应用场景,可以选择不同数量的通道来满足带宽需求。

选型与应用

在选择D-PHY时,首先需要考虑应用的带宽需求、传输距离和功耗限制。例如,若设计需要支持高分辨率摄像头或显示屏,则应选择支持9

Gbps及以上速率的D-PHY;若应用对功耗要求较高,则需要考虑选择低功耗模式下的配置。

应用示例:

假设你正在设计一款汽车前视摄像头的系统,该系统需要支持高清视频传输。你可以选择D-PHY v3.0标准,配置4个数据通道,支持9

Gbps的传输速率,确保图像传输的稳定性和清晰度。同时,选择低功耗模式,以延长摄像头系统的电池寿命。

图4:通用总线结构图

3. MIPI C-PHY(C-PHY协议)

协议概述

MIPI C-PHY是另一种MIPI物理层接口标准,主要用于高带宽需求的应用,如高分辨率相机、显示器和汽车传感器。与D-PHY不同,C-PHY使用了三线差分信号传输,并采用符号率而非直接的数据率来表示传输速率。它的最大传输速率可以达到13.7

Gbps(标准通道)和16 Gbps(短通道)。

C-PHY协议的参数分析

符号率:C-PHY的符号率高达6 Gsps,等效的数据速率为13.7 Gbps(标准通道)和16

Gbps(短通道)。这种高符号率设计使得C-PHY在高分辨率图像传输方面具有显著优势。

信号传输方式:C-PHY采用三线差分信号传输,与D-PHY的两线差分信号相比,提供了更高的带宽和更好的抗干扰性能。

功耗:C-PHY在设计时考虑了低功耗,高效的数据传输是其关键优势之一,适合用于对功耗有严格要求的场合。

协议接口:C-PHY v2.1引入了64位PHY协议接口(PPI),为高性能应用提供了更大的数据总线,支持更高带宽的数据传输。

选型与应用

选择C-PHY时,主要需要考虑应用场景的带宽需求、传输距离和系统的功耗预算。如果需要支持4K或更高分辨率的显示或相机应用,则C-PHY无疑是一个更好的选择,因为它提供了更高的带宽,能够满足高分辨率和大带宽的要求。

应用示例:

如果你正在设计一款4K显示屏的接口系统,并且需要通过高速通道传输图像数据,C-PHY是更合适的选择。通过选择C-PHY

v2.1版本,可以支持高达13.7 Gbps的带宽,确保高清图像数据的稳定传输。同时,使用64位PHY协议接口(PPI)可以提高系统的带宽利用率,减少瓶颈。

图4:C-PHY /D-PHY总线对比图

4.MIPI M-PHY(M-PHY协议)

协议概述

MIPI M-PHY是一种高性能的物理层接口,通常用于需要极高带宽的应用,如高端显示、数据存储和车载传感器系统。M-PHY主要通过串行信号传输,支持不同速率的操作,并提供灵活的选择,能够满足高性能系统的需求。

M-PHY协议的参数分析

传输速率:M-PHY支持从几百Mbps到10 Gbps以上的传输速率,具体速率取决于不同的操作模式和应用场景。M-PHY还支持多通道配置,进一步提升数据传输能力。

协议模式:M-PHY提供多种操作模式,如低功耗模式和高速模式,适应不同的应用需求。高速模式下可以提供更高的带宽,而低功耗模式下则适用于功耗敏感的应用。

带宽和功耗:M-PHY设计时注重带宽和功耗的平衡,通过适配不同的操作模式来满足高带宽和低功耗的要求。

选型与应用

M-PHY特别适合需要高带宽、低延迟和大数据吞吐量的应用场景。选择M-PHY时,需要综合考虑带宽需求、功耗限制以及系统的复杂性。例如,对于车载高分辨率雷达传感器系统,M-PHY可以通过其高带宽支持大数据流的实时传输。

应用示例:

假设你设计了一款自动驾驶汽车的雷达传感器系统,需要将大量数据实时传输到车载计算平台。选择M-PHY能够提供足够的带宽,支持高达10

Gbps的高速数据传输,同时选择低功耗模式来确保车载系统在长时间运行下不会出现过度发热或电池消耗过快的问题。

eDP(Embedded DisplayPort)介绍

DisplayPort是由PC及芯片制造商联盟开发,由VESA(视频电子标准协会)所标准化发布的数字视频接口标准。该接口免认证、免授权金,主要用于视频源与显示器等设备的连接,并也支持携带音频、USB和其他形式的数据。

eDP(Embedded DisplayPort) 协议是针对DP(Display Port)应用在嵌入式方向架构和协议的拓展,所以eDP协议完全兼容DP协议。相对于DVI/HDMI来说,eDP具有高带宽、整合性好、相关产品设计简单,该接口已广泛应用于笔记本电脑、平板电脑、手机等其它集成显示面板和图像处理器的领域。

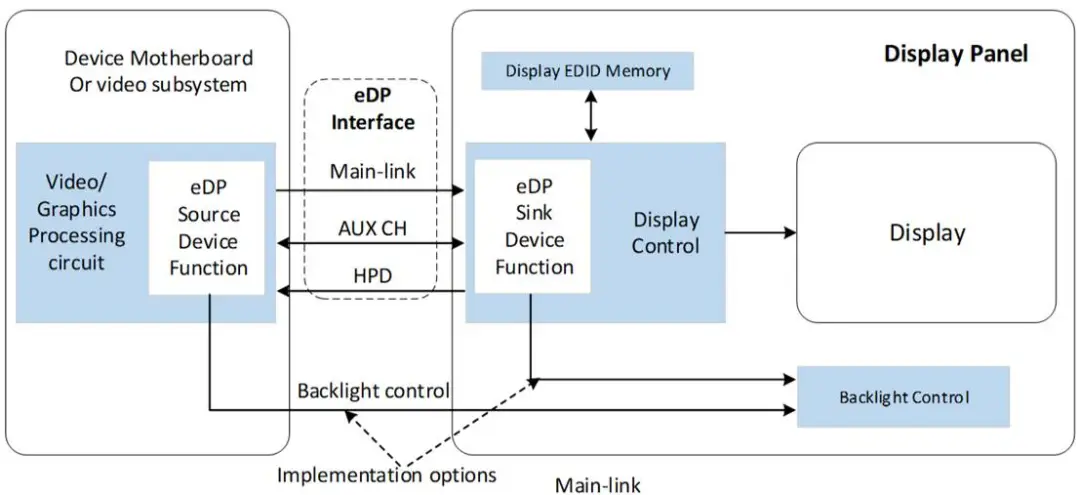

1. eDP的系统架构:

图5:eDP总线通信结构图

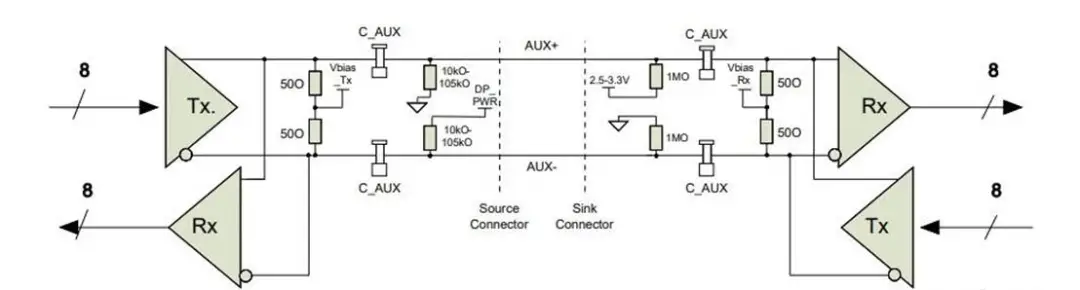

从系统架构图中可以看出,DP/eDP均需要包含3个主要信号:

Main-Link:

主链路是一个单向、高带宽、低延迟的信道,用以传输诸如未压缩的视频和音频的同步数据流。注意Main-Link可以为1

Lane,2 Lane或者4 Lane。其中每一lane是一对差分信号线。

每一条Lane上所传输的数据为8b10b编码,即8bit的数据源在TX端会被encoder,扩展为10bit,其中嵌入了时钟信息。在RX端进行decoder后,恢复为8bit编码的原始数据。因为这样的设计,在长距离的传输中,才能有更好的EMI电磁兼容性设计。同时,在数据Lane的传输中已经自带时钟信息,无需再额外使用一对时钟信号线。

由于Main link的这个特性,因此在每次启动DP传输之前,或者当检测到传输过程中发生错误之后,均需要启动一个Link

training的过程。这个training主要是对连接器以及线缆上的信号损失进行补偿,以确保无错误的数据传输。

Training的过程将通过AUX CH来进行,当Source端检测到HPD信号时,认为有sink插入,即会启动DP

training。

注:DP2.0协议时,将8b/10b编码改为了128b/132b编码,带宽利用率更高。

AUX CH:

辅助通道(AUX CH)是DisplayPort接口中的一个部分,它用一根特殊的线(差分对)来传输数据,这根线能双向传输信息,但同一时间只能一个方向传。AUX

CH用了一种叫做Manchester-II的编码方式来处理数据,而且它不需要单独的时钟线,时钟信号是从数据里自己提取出来的。

图6:AUX CH差分信号原理图

AUX CH在普通的电缆上能以1Mbps的速度传输数据,每次通信最多500 us,每次最多传16个字节的数据。这样设计是为了防止一个设备长时间占用通道,让其他设备也能用。

但是,如果用一种叫做高比特率(HBR)的特殊电缆,AUX CH就能以更快的速度(最高720Mbps)来传输数据,这种模式下叫做FAUX事务格式。

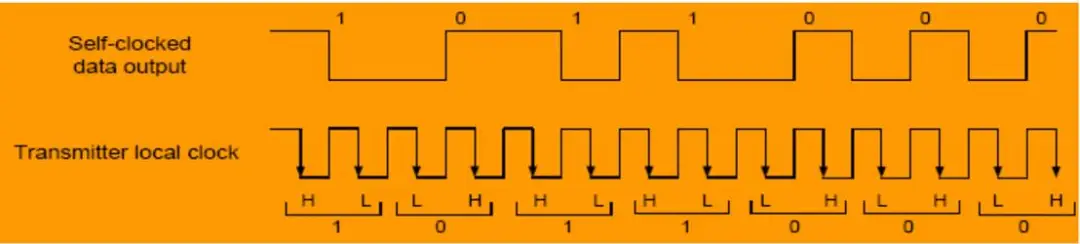

在Aux Channel 上传输的是自带时钟信号的曼切斯特编码,因此不需要传输时钟信号线。如下图所示:

图7:Manchester-II的通信时序图

从图上可见,第一个时钟周期检测到下降沿(从H到L),信号为1;第二个时钟周期检测到上升沿(从L到H),信号为0,以后类推。

HPD:

Hot Plug Detect,一根单独的信号线,用来从Sink端向Source端发出中断,通知Sink设备已经插入,可以进行通讯了。

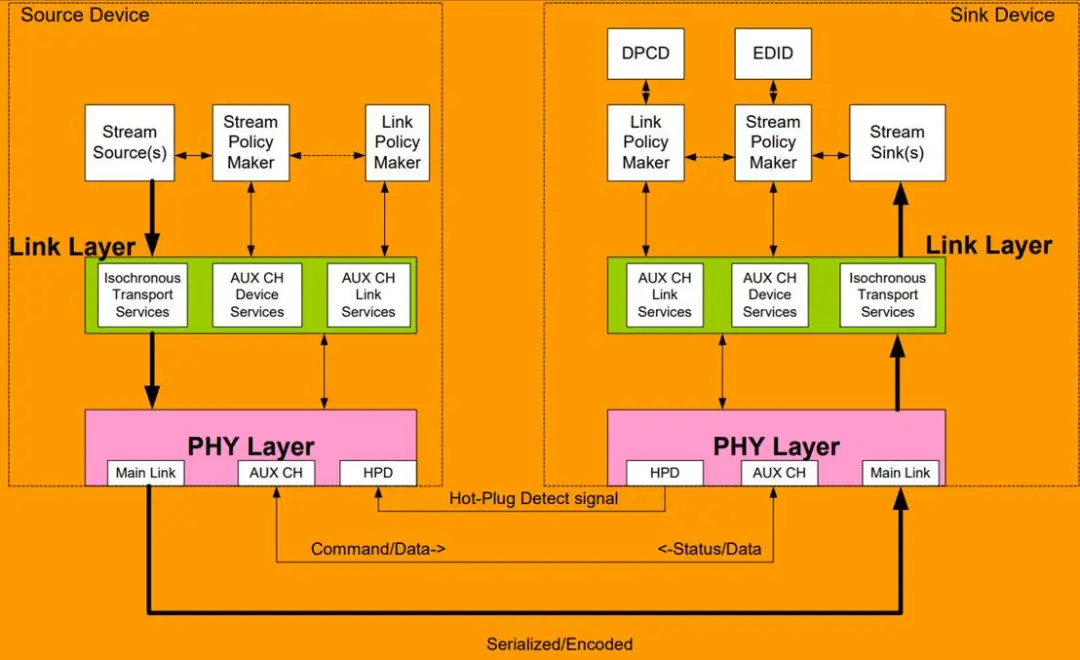

DP的传输协议

从DP传输分层架构来看,Link层提供三种服务分别是Isochronous Transport Services、AUX

CH Device Services和AUX CH Link Services,其中Isochronous

Transport Services主要是对于传输的音视频数据进行格式的打包填充,AUX CH Device

Services主要用来管理源端和接收端的设备,比如读取EDID信息。AUX CH Link Services主要是对链路的维护配置,保障链路的正确建立,确保接收端和发送端时钟同步,确保main

link上的数据准确传输。

这三种服务在Stream Policy Maker和Link Policy Maker的策略指挥下进行“服务”,受Policy

Maker的控制。

图8:DP传输分层架构图

PHY层主要负责发送/接收数据。

在接收端设备中,有着显示端口配置寄存器,里面的配置数据(DPCD)描述了DPRX的功能,就像EDID描述了接收端显示器的的功能一样。Link

and Stream Policy Makers分别管理Link和Stream。

DP的传输带宽

DP可以传输16,18,24bit R'G'B', YUV444, YUV422等格式的视频流信号。并且采用8b/10b的编码格式。因此在计算显示器所需的带宽速率时,需要考虑到这些因素的影响。同时还要考虑blanking的影响,采用Htotal*Vtotal来计算。下表是一个不同版本DP的理论物理带宽和有效带宽规格:

图9:DP各版本带宽

对于一个4K@60fps的视频传输要求,如果采用24bit的RGB格式传输,它所需要的带宽为:

- 分辨率: 3840×2160(Htotal=3920、Vtotal=2222)

- 刷新率: 60Hz

- 色彩深度: 8bit

- 色彩格式: RGB 24bit(RGB:8乘以3,YC422:8乘以2,YC420:8乘以1.5)

将以上四个相关参数乘起来,即可得到所需带宽:

3920 * 2222 * 60 * 8 * 3 = 12,542,745,600(12.543Gbps)

如果DP不能提供足够的带宽,也可以将24bit RGB转换为YUV422 色彩格式进行传输,此时所需要的带宽就变成:

3920 * 2222 * 60 * 8 * 2 = 8,361,830,400 (8.362Gbps)

Open LVDS Display Interface(OpenLDI)介绍

LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口,每一条通道输出的都是一对差分信号。它为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。LVDS是利用电压差(典型值为350

mV)进行编码信息。

OLDI传输方法介绍

OpenLDI,LVDS链使用了8对串行数据线(A0~A7)和两个采样时钟线(CLK1和CLK2)。实际使用的串行数据线依赖于像素格式,串行数据率为7倍采样时钟频率。CLK2信号在双像素模式下用于与FDP链(一种高速数字视频接口)接收端后向兼容。

- 传输18位单像素R'G'B'时,OpenLDI串行线的A0~A2用于传输。

- 传输24位单像素R'G'B'时,OpenLDI串行线的A0~A3用于传输。

- 传输18位双像素R'G'B'时,OpenLDI串行线的A0~A2,A4~A6用于传输。

- 传输24位双像素R'G'B'时,OpenLDI串行线的A0~A7用于传输。

对上面每种编码方式,物理层采用不同的结构,参见图10。

18位单像素格式采用一个时钟和 3 条通路(A): A0 ~ A2 数据通路和CLK1。双像素格式采用相同的通路和时钟,但增加了另一个时钟和另外3

条通路 (B):A4 ~ A6 和CLK2。

24位单像素格式采用一个时钟和 4 条通路(A):A0 ~ A3 及CLK。双像素格式额外增加了四条通路,有两个时钟和8

条通路 (B):除24 位单像素通路外,还使用A4 ~ A7 及CLK2。

图10:OpenLDI可以支持8条数据通路及最多2条时钟通路(CLK)

在传输显示数据时,OLDI实际上每一对差分线传输的是7bit的数据,因此一个时钟节拍内,4对差分线可以传输28bit的数据,其中包含24bit数据和3个bit的控制信号。如下图所示,D0+/-

~ D2+/-传输RGB666+DE+VS+HS,D3+/-传输剩下的6bit RGB。因此3对差分线可以传输18bit

RGB666,4对线可以传输RGB888。

总结

本文详细介绍了MIPI、eDP和OLDI/LVDS等汽车座舱系统的板内视频信号通信协议,主要应用场景是在Ser/Des之间的视频数字信号通信协议。后续有机会详细介绍各通信协议的内容。

|