| 编辑推荐: |

| 本文来自于csdn,文章主要介绍了FPGA是什么,FPGA设计流程以及最常见的FPGA架构组成等相关知识。 |

|

随着FPGA的制造工艺进步和计算需求的发展,一些资源丰富、性能强大的FPGA被用在越来越多的嵌入式处理领域。相对于GPU,FPGA的处理速度在相同的情况下,其功耗更低,体积更小,计算密度更大,价格更加能被普通的商业、工业场合应用。在机器人和工业检测等需要高速并行的视觉处理系统邻域,FPGA具有广泛的应用前景。

FPGA(现场可编程门阵列)是一种集成电路,由于其具有重配置性能,开发人员可以自行进行设计制造,按照功能需求,将硬件电路进行搭建,因此现场可编程。FPGA常使用VHDL或者Verilog

HDL硬件描述语言进行电路设计,也可以用电路图设计。FPGA是基于LUT结构,包含一组可编程逻辑块,以及可重构互连的层次结构,就像可以在不同配置中互连的许多逻辑门一样。逻辑块可以被配置为执行复杂组合功能,或者是简单的逻辑门,如AND门和XOR门[26]。在FPGA中,逻辑块还包括存储元件。大多数FPGA的配置容易丢失,需要在每次上电的时候,重新载入,而配置数据包含在对系统编程的配置文件中[27][28]。

可编程逻辑器件大致分为两种,一种是输出(“或”门)阵列被固定连接代替,每一个或门都有一个固定数量的与门与之连接,这就是可编程阵列逻辑(PAL),如图4.1左侧所示。这种结构都由EEPROM和Flash工艺制造,该技术使器件能被擦除,并进行简单的再编程而改变逻辑功能。另一种是固定其“与”的部分并且使用“或”部分成为可编程,如图4.1右侧所示。这种结构有效的产生了可编程只读存储器(PROM)和查找表(LUT)。FPGA就是基于查找表结构。

完整的FPGA设计流程包括设计输入,综合,转换,映射,布局布线,生成配置文件以及下载和调试等步骤[29]。FPGA的设计一直伴随着仿真,包括行为和功能仿真,门级仿真,时序仿真,系统内部验证等。如图4.3给出的设计流程图。

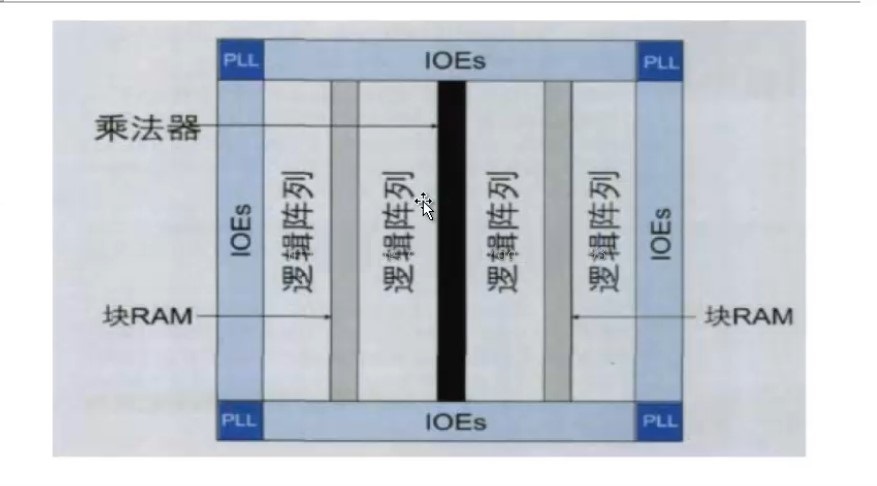

最常见的FPGA架构由一系列的用来实现应用程序的可配置逻辑块(LAB),I/O焊盘和路由通道组成。

I/O焊盘可以适应于阵列 宽度。逻辑块 由几个 单元组成,典型 是4输入LUT,如图4.2所示。FPGA内部

多是同步电路,需要一个全局时钟信号,驱动整个FPGA上的信号同步和操作的时序。一个复杂的设计包含多个时钟,因此需要内部全局时钟通过不同频率和相位的变换,产生单独的时钟域。这借助于PLL和(或)DLL实现。

设计输入包括使用硬件描述语言和原理图输入两种形式。HDL语言适用于自顶向下的设计,支持模块化编程,不随芯片的工艺布局变化而变化,程序的复用性和可移植性较好。而原理图输入在EDA软件上绘制特定功能的电路图实现,在顶层设计、手工优化电路方面有节省资源、图形界面强的特点。

功能仿真,对所设计电路进行逻辑功能的测试和模拟。不依赖器件的具体特性,是初步设计最好的验证手段。主要有测试文件输入和激励波形文件输入两种,一般采用的是测试文件输入(Test

Bench)。测试文件是用硬件描述语言编写测试程序,设定好输入信号,并且从某个进程或文本文件中读取所需的输入数据,将数据传入待测试的模块,并且将最后的结果和预期的数据进行比较来确定设计的功能是否正确[30]。通过功能仿真,调整时序和信号的延迟,这对于整个设计的信号同步很有必要。

综合,对指定的电路实现功能和产生实现电路的约束文件,其主要机制是将HDL语言的具体功能的设计输入翻译转换为与、或、非门以及查找表,触发器等基本逻辑单元组成的逻辑连接,然后进行速度、面积的优化,输出网表文件,供布局布线使用[31]。

映射布局布线,将综合阶段产生的逻辑网表文件适配到FPGA的具体电路中。布局指的是将逻辑网表中的硬件原语或底层单元适配到FPGA固有硬件结构上,布线指的是根据布局的拓扑结构,将所需要的逻辑块正确合理的连接,搭建具有特定功能的模块电路。

时序仿真和内部系统验证,称为后仿真,是具体在FPGA中实现时候,包含电路与逻辑门的延迟,以及布局布线的延迟,这是与FPGA实际执行功能的情况下进行比较,如果后仿真有问题,就需要返回设计输入,重新规划,这一步也确定了内部系统是否合理,验证设计正确性,确保FPGA设计稳定可靠。

配置和下载,将正确的FPGA设计,所生成的配置文件,一般是Bit文件转换为MCS文件,在经过外围电路,利用JTAG下载到FPGA的外围配置电路上,使得FPGA上电后能进行配置。

在本课题的设计中,遵循上述开发流程,对每一步都进行合理准确的设计和仿真。根据高速相机采集卡的驱动电路和配置文件,我们选择VHDL语言进行输入,在Xilinx的综合设计平台ISE14.7上进行设计,搭载Mentor

Graphics的ModelSim SE 10.1c仿真工具对设计电路进行时序和设计仿真,数据对比,通过

更改,最后 到FPGA 上。

FPGA的选型,根据所设计功能所需的数据存储容量,逻辑单元的数量,在应用场景的实际功耗,以及FPGA的I/O数量是否满足要求进行选择。著名的FPGA生产厂家是美国的Xilinx公司和Altera公司。在航空航天,自动驾驶,消费电子和能源产业中,均具有各类产品,能满足不同性能需求。Xilinx生产的Spartan系列和Virtex系列应用较为广泛,前者满足低成本设计,后者针对于高性能设计。本课题选择的是Spartan3系列的xc3s5000-4fg900芯片,采用的900球FBGA封装技术,90nm制造工艺,系统门级数量有5M,可用的逻辑单元66560个,4输入查找表66560,可配置逻辑块8320个,分布式RAM有520K,块RAM有1872K,专用乘法器104个,数字时钟管理器4个,最大可用引脚784个[32]。考虑到处理的图像是512×512大小,需要缓存的数据有5行,以及并行控制信号,在处理过程中所消耗的存储器容量和乘法器资源,而Spartan3片上RAM-18K有104个,所提供的乘法器为18位双输入二进制乘法器,缓存容量足够,提供算术操作的逻辑单元丰富,完全满足图像处理过程中的计算资源要求,因此采用本款芯片。

FPGA的设计中,时钟系统的设计极其重要,通常时钟信号会使用BUFG网络减少传输延迟,提高系统性能并增强系统的稳定性。

在实际使用中,经常会遇到需要将某个BUFG上的时钟信号通过FPGA的普通IO输出。如果直接从BUFG上连接到OBUF上,在编译器map的过程中就会出现错误,并提示规避错误的方法,就是在约束文件中加上一条约束,让编译器忽略时序约束的要求,直接通过普通逻辑资源连接。虽然这个约束能规避这个错误,但中间的时序将无法评估,因此可能会导致错误的发生。

Xilinx Spartan6对于这种应用给出的解决方案是通过ODDR2来连接,每个IO都有ODDR2资源,这些资源可以连接到BUFG网络上。

使用举例:

ODDR2#(

.DDR_ALIGNMENT("NONE"),// Sets

output alignment to "NONE", "C0"

or "C1"

.INIT(1'b0),// Sets initial state of

the Q outputto 1'b0 or 1'b1

.SRTYPE("SYNC")// Specifies "SYNC"

or "ASYNC" set/reset

) ODDR2_inst (

.Q(需要输出的时钟信号连线),// 1-bit DDR output data

.C0(BUFG上的时钟信号),// 1-bit clock input

.C1(BUFG上的时钟信号的180度反相信号),// 1-bit clock

input

.CE(1'b1), // 1-bit clock enable input

.D0(1'b1), // 1-bit data input (associatedwith

C0)

.D1(1'b0), // 1-bit data input (associatedwith

C1)

.R(1'b0),// 1-bit reset input

.S(1'b0)// 1-bit set input); |

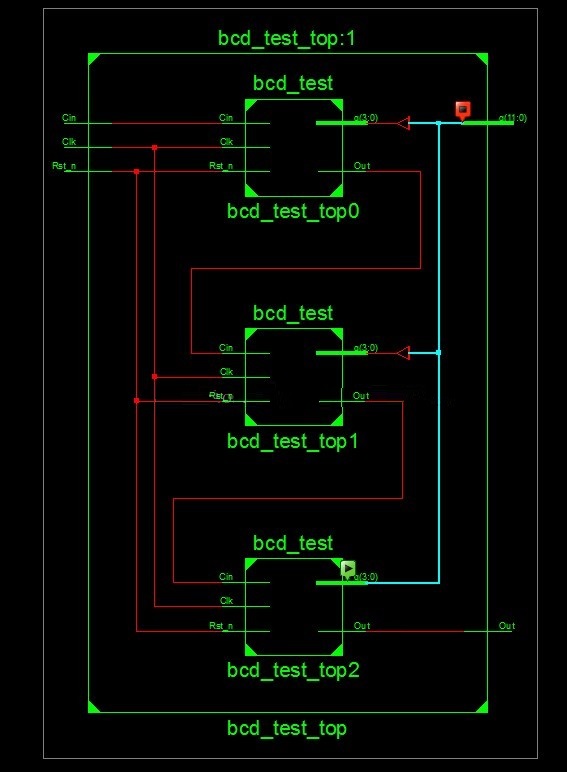

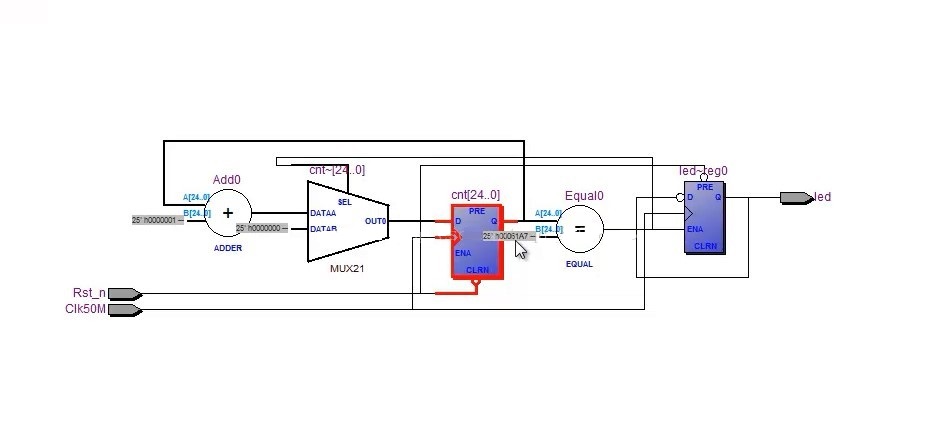

计算器原理图:

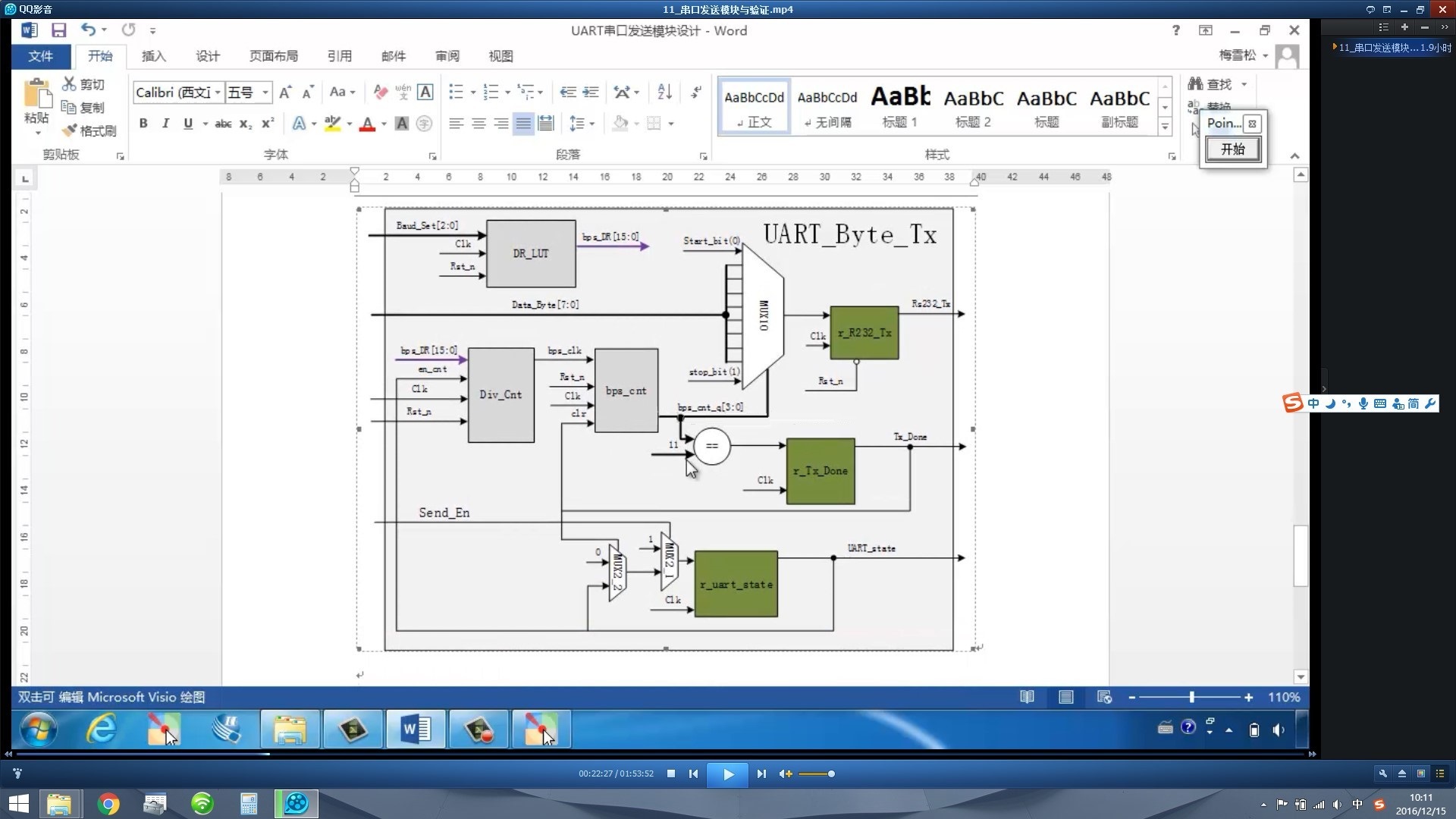

波特率设置:

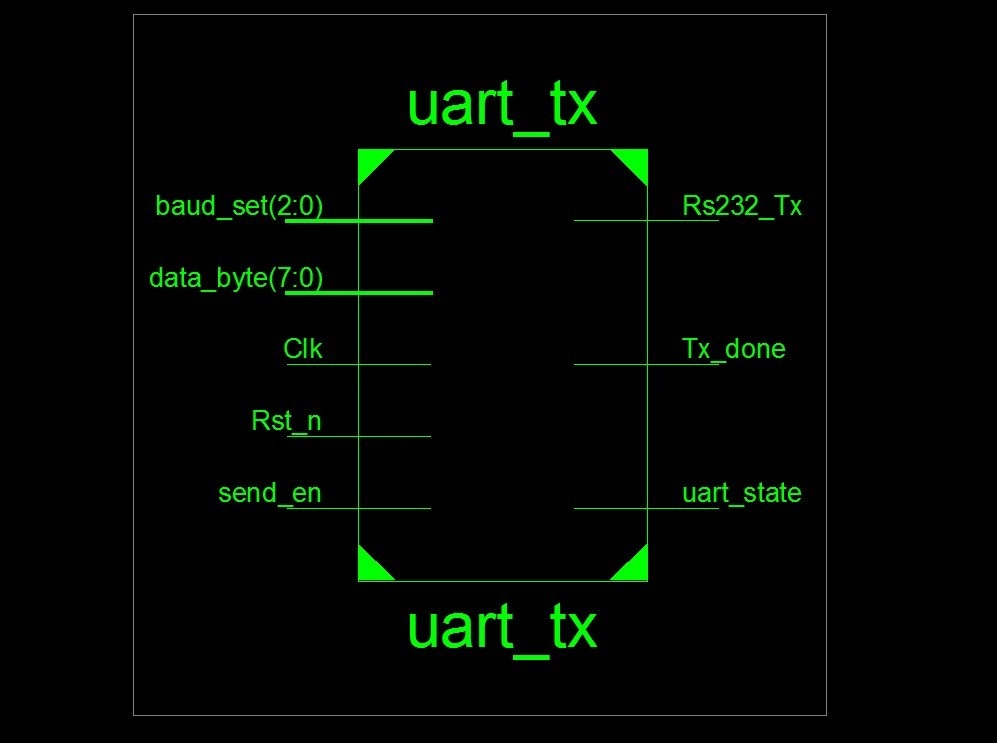

串口设置:

问题所在:

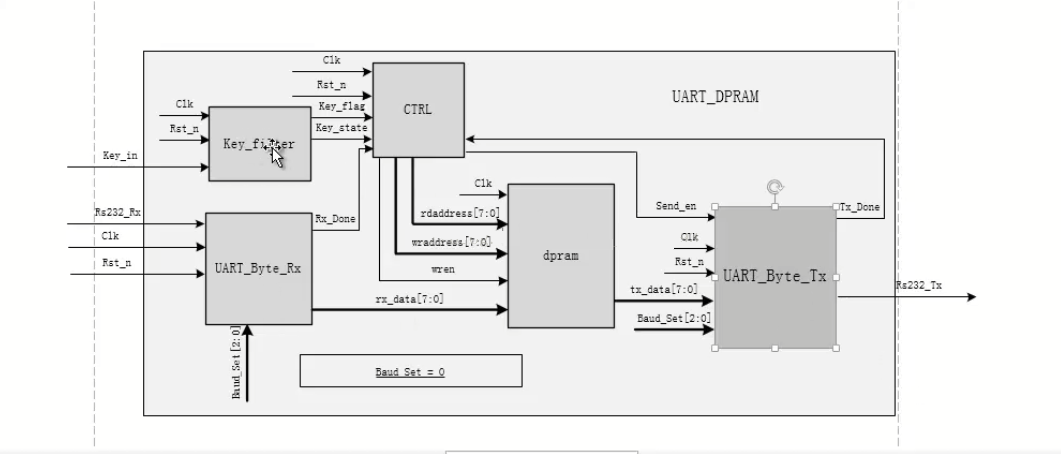

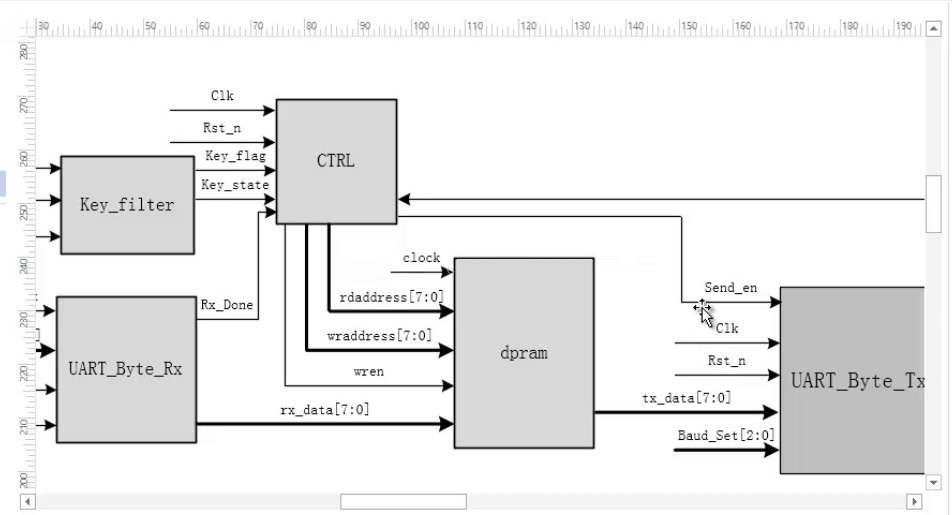

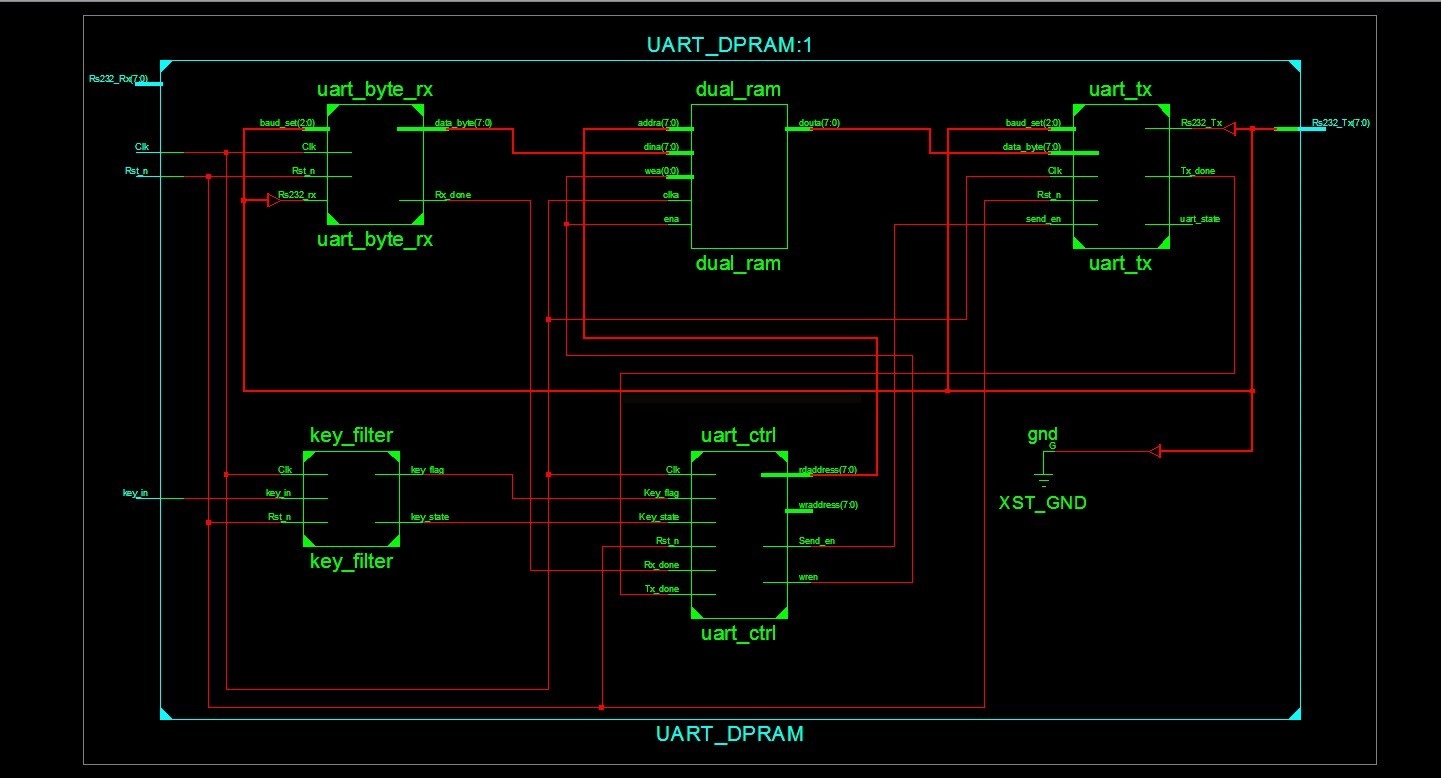

系统设计:

为了更好的观察时钟沿与地址、数据变化的过程,全编译后进行时序仿真。读数据时,可以看出第一个箭头时钟上升沿采到地址0;第二个时钟上升沿开始赋值,但是由于逻辑延迟(红框)后才开始赋值;因此第三个时钟上升沿的数据才是稳定的。

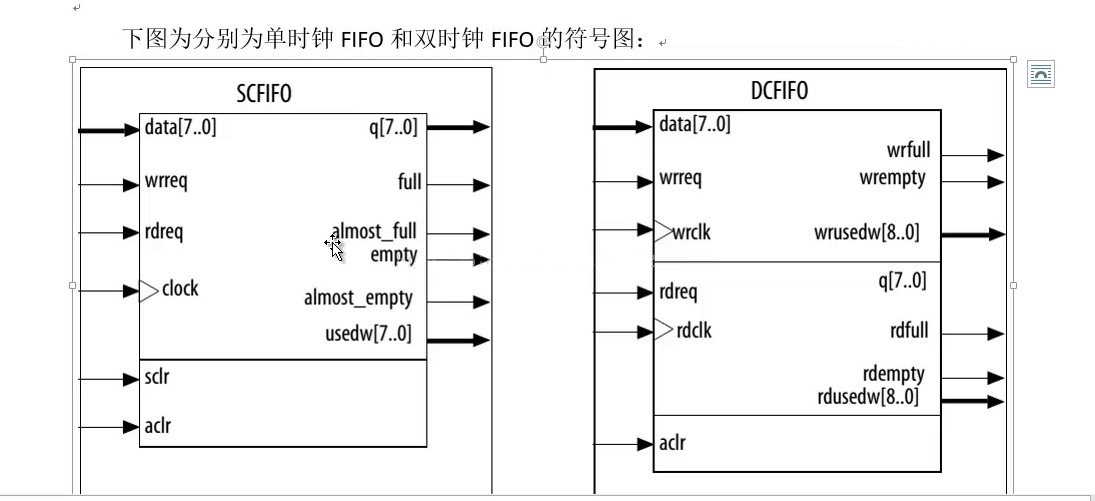

FIFO这一章:

|