| БрМЭЦМі: |

БОЮФРДздгкзїепErik

Luther,ЭЈЙ§НщЩмЭъећЕФДѓЙцФЃMIMOгІгУГЬађПђМмДѓЙцФЃЕФЖрЪфШыЖрЪфГіЃЈMIMOЃЉЪЧ5GЮоЯпЭЈбЖЁЃ |

|

ДѓЙцФЃЕФЖрЪфШыЖрЪфГіЃЈMIMOЃЉЪЧ5GЮоЯпЭЈбЖбаОПжавЛИіСюШЫаЫЗмЕФСьгђЁЃЖдЯТвЛДњЮоЯпЪ§ОнЭЈбЖЭјТчЃЌЫќНЋДјРДЯджјЕФНјВНЃЌгЕгадкИќИпЕФЪ§ОнЫйТЪЯТвдИќИпЕФПЩППадШнФЩИќЖргУЛЇЭЌЪБЯћКФИќЕЭЙІКФЕФФмСІЁЃЪЙгУNI

ДѓЙцФЃMIMOЕФгІгУГЬађПђМмЃЌбаОПепПЩвдПьЫйДюНЈ128ЬьЯпЕФMIMOВтЪдЦНЬЈЃЌВЩгУвЛСїЕФLabVIEWЯЕЭГМЖЩшМЦШэМўКЭЖЅМтЕФNI

USRP RIOШэМўЮоЯпЕчгВМўЃЌРДНјааДѓЙцФЃЬьЯпЯЕЭГЕФПьЫйдаЭПЊЗЂЁЃЪЙгУвЛЬзМђЕЅЧвПЩгІгУгкДДНЈЛљгкFPGAТпМКЭИпадФмДІРэгХЛЏВПЪ№ЕФЩшМЦСїГЬЃЌИУСьгђЕФбаЗЂепФмЙЛЪЙгУЭГвЛЕФШэМўКЭгВМўЩшМЦСїГЬРДТњзуетаЉИпЖШИДдгЯЕЭГЕФдаЭЩшМЦашЧѓЁЃ

ФкШн

ДѓЙцФЃMIMOВњЦЗдаЭИХЪі

ДѓЙцФЃMIMOЯЕЭГМмЙЙ

LabVIEWЯЕЭГЩшМЦЛЗОГ

ЛљеОЪеЗЂаХЛњ(BTS)ШэМўМмЙЙ

гУЛЇЩшБИ

ДѓЙцФЃЖрШыЖрГі(MIMO)МђНщ

ЫцзХвЦЖЏЩшБИЕФЪ§СПКЭШЫУЧЫљЪЙгУЕФЮоЯпЪ§ОнСїСПЕФжИЪ§МЖдіГЄЃЌЧ§ЪЙзХбаОПШЫдБЖдгкаТММЪѕКЭаТЗНЗЈЕФЬНОПвдНтОіетвЛШевцдіГЄЕФашЧѓЁЃЯТвЛДњЕФЮоЯпЪ§ОнЭјТчЃЌБЛГЦзїЕкЮхДњвЦЖЏЭЈбЖММЪѕЛђ5GЃЌБиаывЊНтОіШнСПЯожЦЃЌвдМАвЛаЉЯжгаЭЈаХЯЕЭГжаДцдкЕФЬєеНЃЌжюШчЭјТчЕФПЩППадЁЂИВИЧТЪЁЂФмаЇадЁЂКЭбгГйадЕШЁЃДѓЙцФЃMIMOзїЮЊ5GММЪѕЕФвЛжжЪЕЯжЗНАИЃЌЭЈЙ§дкЛљеОЪеЗЂаХЛњЃЈBTSЃЉЩЯЪЙгУДѓСПЕФЬьЯпЃЈГЌЙ§64ИљЃЉЪЕЯжСЫИќДѓЕФЮоЯпЪ§ОнСїСПКЭСЌНгПЩППадЁЃетжжЗНЪНДгИљБОЩЯИФБфСЫЯжгаБъзМЕФЛљеОЪеЗЂаХЛњМмЙЙЃЌЯжгаБъзМжЛЪЙгУСЫзюЖр8ИљЬьЯпзщГЩЕФЩШаЮЭиЦЫЁЃгЩгкгЕгаЪ§вдАйМЦЕФЬьЯпЕЅдЊЃЌДѓЙцФЃMIMOПЩвдЪЙгУдЄБрТыММЪѕМЏНЋФмСПМЏжаЕНФПБъвЦЖЏжеЖЫЩЯЃЌДгЖјНЕЕЭСЫЗјЩфЙІТЪЁЃЭЈЙ§АбЮоЯоФмСПжИЯђЕНЬиЖЈгУЛЇЃЌЗјЩфЙІТЪНЕЕЭЃЌЭЌЪБЖдгкЦфЫћгУЛЇЕФИЩШХвВНЕЕЭЁЃетвЛЬиадЖдгкФПЧАЪмИЩШХЯожЦЕФЗфЮбЭјТчРДЫЕЪЧЗЧГЃгаЮќв§СІЕФЁЃШчЙћДѓЙцФЃMIMOЕФЯыЗЈецЕФПЩвдЪЕЯжЃЌФЧУДЮДРДЕФ5GЭјТчвЛЖЈЛсБфЕУИќПьЃЌФмЙЛШнФЩИќЖрЕФгУЛЇЧвОпгаИќИпЕФПЩППадКЭИќИпЕФФмаЇЁЃ

гЩгкДѓЙцФЃMIMOЪЙгУСЫНЯЖрЕФЬьЯпЕЅдЊЃЌвђЖјУцСйСЫвЛаЉЯжгаЭјТчЮДгіЕНЙ§ЕФЯЕЭГЬєеНЁЃБШШчЫЕЃЌЕБЧАЛљгкLTEЛђLTE-AЕФЪ§ОнЭјТчЫљашЕФЕМЦЕПЊЯњЪЧгыЬьЯпЕФЪ§СПГЩБШР§ЕФЁЃЖјДѓЙцФЃMIMOЙмРэСЫДѓСПЪБЗжИДгУЕФЬьЯпЕФПЊЯњЃЌдкЩЯЯТаажЎМфОпгааХЕРЛЅвзадЁЃаХЕРЛЅвзадЪЙЕУЩЯааЕМЦЕЛёШЁЕФЭЈЕРзДЬЌаХЯЂПЩвддкЯТааСДТЗЕФдЄБрТыЦїжаБЛЪЙгУЁЃЦфЫћИќЖрЪЕЯжДѓЙцФЃЖрШыЖрГіЕФЬєеНЛЙАќРЈЃКдквЛИіЛђЖрИіЪ§СПМЖЯТРДШЗЖЈЪ§ОнзмЯпКЭНгПкЕФЙцФЃЃЛвдМАдкжкЖрЖРСЂЕФЩфЦЕЪеЗЂЦїжЎМфНјааЗжВМЪНЕФЭЌВНЁЃ

етаЉгаЙиЖЈЪБЁЂДІРэвдМАЪ§ОнЪеМЏЩЯЕФЬєеНЪЙЕУдаЭЛЏбщжЄБфЕУИќЮЊживЊЁЃЮЊСЫШУбаЗЂепФмЙЛжЄЪЕЖдгІРэТлЃЌетОЭвтЮЖзХашвЊАбРэТлЙЄзїзЊвЦЕНЪЕМЪЕФВтЪдЬЈЩЯЁЃЭЈЙ§ЪЙгУецЪЕгІгУГЁОАжаЕФЪЕМЪВЈаЮЃЌбаЗЂепПЊЗЂГіВњЦЗдаЭВЂШЗЖЈДѓЙцФЃMIMOЕФММЪѕПЩааадКЭЩЬвЕПЩааадЁЃОЭаТаЭЮоЯпБъзМКЭММЪѕРДЫЕЃЌАбИХФюзЊЛЏЮЊВњЦЗдаЭЕФЪБМфОЭжБНггАЯьЕНСЫЪЕМЪВПЪ№КЭЩЬвЕЛЏЕФНјГЬЁЃбаЗЂепФмдНПьЕиПЊЗЂГіВњЦЗдаЭЃЌОЭвтЮЖзХЩчЛсФмдНдчЕиЪмвцгкетЯюДДаТММЪѕЁЃ

ДѓЙцФЃMIMOВњЦЗдаЭИХЪі

ЯТУцЫљЪіЕФЪЧвЛИіЭъећЕФДѓЙцФЃMIMOгІгУГЬађПђМмЁЃЫќАќКЌСЫДюНЈЪРНчЩЯзюЭЈгУЕФЁЂСщЛюЕФЁЂПЩРЉеЙЕФДѓЙцФЃMIMOВтЪдЬЈЫљашЕФгВМўКЭШэМўЃЌИУВтЪдЬЈжЇГжЪЕЪБДІРэвдМАдкбаЗЂЭХЖгЫљИааЫШЄЕФЦЕЖЮКЭДјПэЩЯНјааЫЋЯђЭЈаХЁЃЪЙгУNIШэМўЮоЯпЕчЃЈSDRsЃЉКЭLabVIEWЯЕЭГЩшМЦЦНЬЈШэМўЃЌетжжMIMOЯЕЭГЕФФЃПщЛЏЬиадДйЪЙЯЕЭГДгНігаМИИіНкЕуЗЂеЙЕНСЫ128ЬьЯпЕФДѓЙцФЃMIMOЯЕЭГЁЃВЂЧвЫцзХЮоЯпбаОПЕФбнНјЃЌЛљгкгВМўЕФСщЛюадЃЌЫќвВПЩвдБЛжиаТВПЪ№ЕНЦфЫћХфжУЕФгІгУжаЃЌБШШчЕуЖдЕуЭјТчжаЕФЗжВМЪННкЕуЃЌЛђЖраЁЧјЗфЮбЭјТчЕШЁЃ

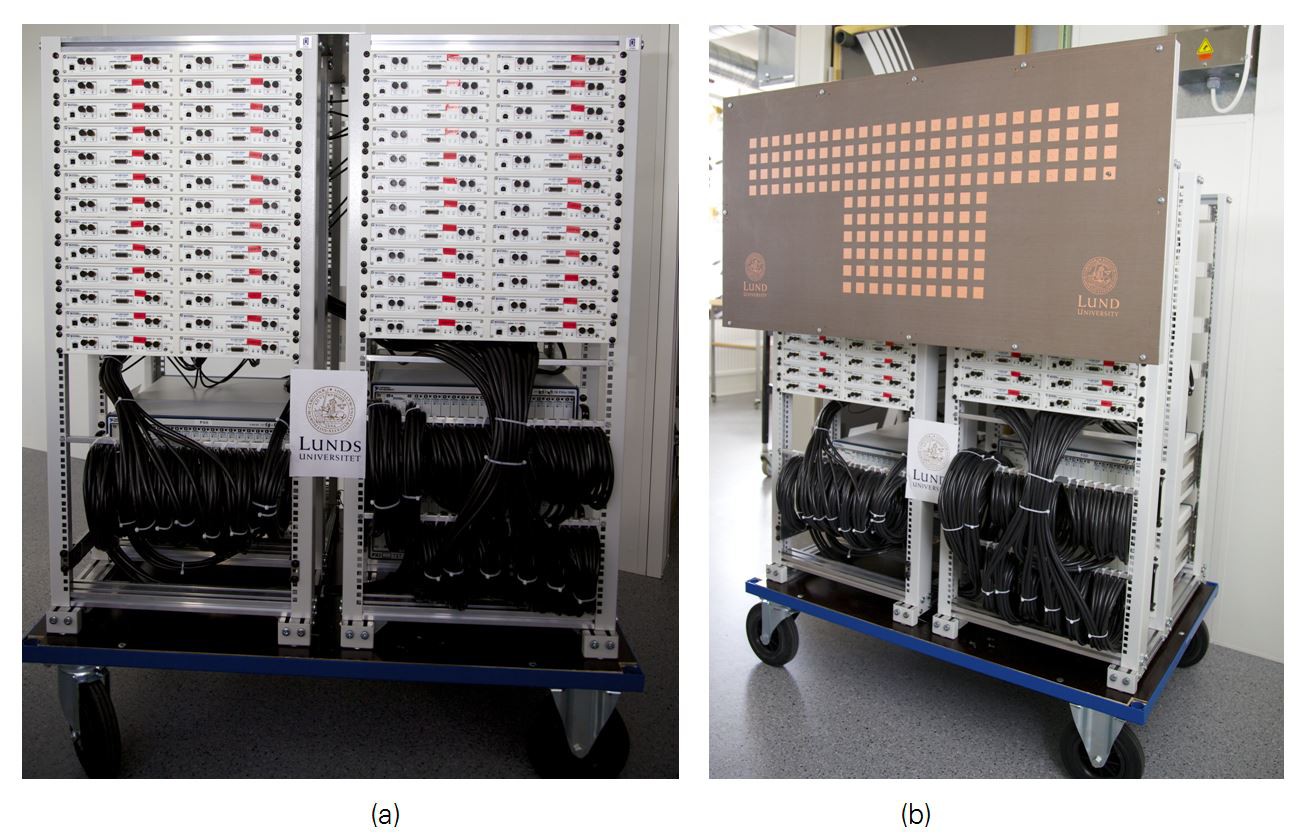

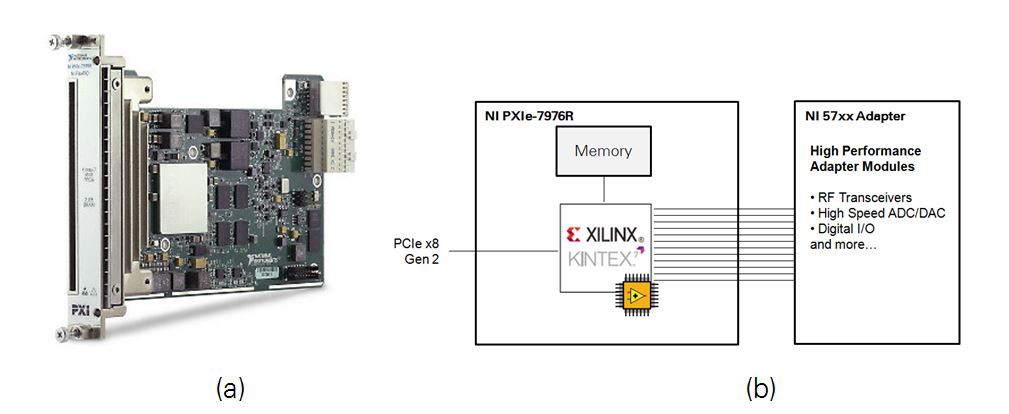

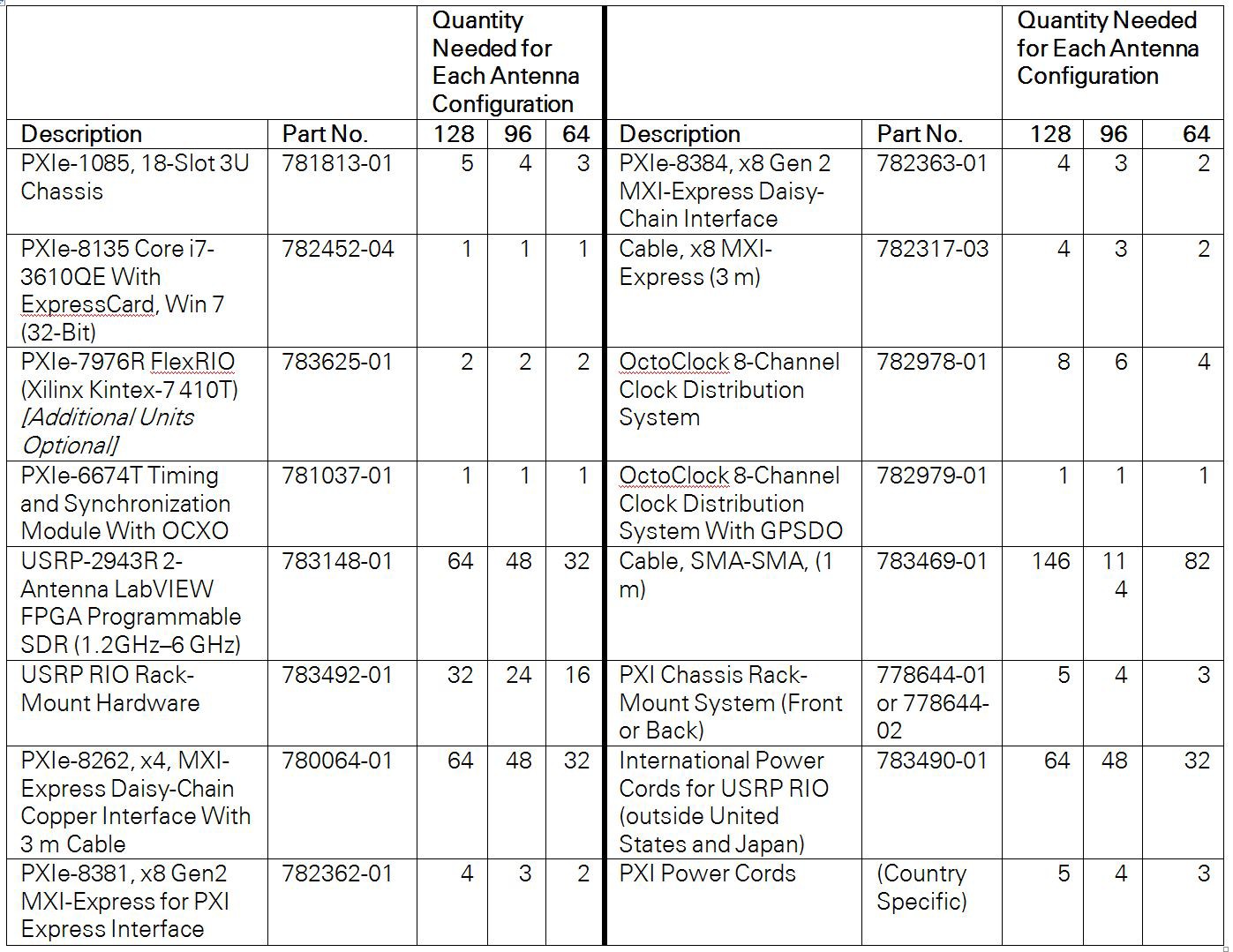

ЭМ1. Ш№ЕфТЁЕТДѓбЇЁЊЁЊЛљгкUSRP RIOЕФДѓЙцФЃMIMOВтЪдЬЈ (a)

вЛжжздЖЈвхЕФКсЯђМЋЛЏЬљЦЌЬьЯпеѓСа(b)ЁЃ

Ш№ЕфТЁЕТДѓбЇЕФOve EdforsНЬЪкКЭFredrik TufvessonНЬЪкгыNIвЛЦ№КЯзїЃЌЪЙгУNIДѓЙцФЃMIMOгІгУГЬађПђМмПЊЗЂГіСЫвЛЬзЪРНчЩЯзюДѓЙцФЃЕФMIMOЯЕЭГЃЈМћЭМ1ЃЉЁЃЫћУЧЕФЯЕЭГЪЙгУСЫ50ЬзUSRP

RIOШэМўЮоЯпЕчРДЪЕЯжДѓЙцФЃMIMOЛљеОЪеЗЂаХЛњЬьЯпЪ§ЃЈМћБэ1ЃЉЮЊ100ЬьЯпЕФХфжУЁЃЛљгкШэМўЮоЯпЕчЕФИХФюЃЌNIКЭТЁЕТДѓбЇбаЗЂЭХЖгПЊЗЂСЫЯЕЭГМЖЕФШэМўКЭЮяРэВуЃЌИУЮяРэВуЪЙгУСЫРрЫЦгкLTEЕФЮяРэВуКЭЪБЗжИДгУММЪѕРДЪЕЯжвЦЖЏЖЫНгШыЁЃдкетвЛКЯзїЙ§ГЬжаЫљПЊЗЂЕФШэМўЃЌПЩзїЮЊДѓЙцФЃMIMOгІгУГЬађПђМмЕФвЛВПЗжБЛЯТдиЁЃБэ1жаеЙЪОСЫДѓЙцФЃMIMOгІгУГЬађПђМмЫљжЇГжЕФЯЕЭГКЭавщВЮЪ§ЁЃ

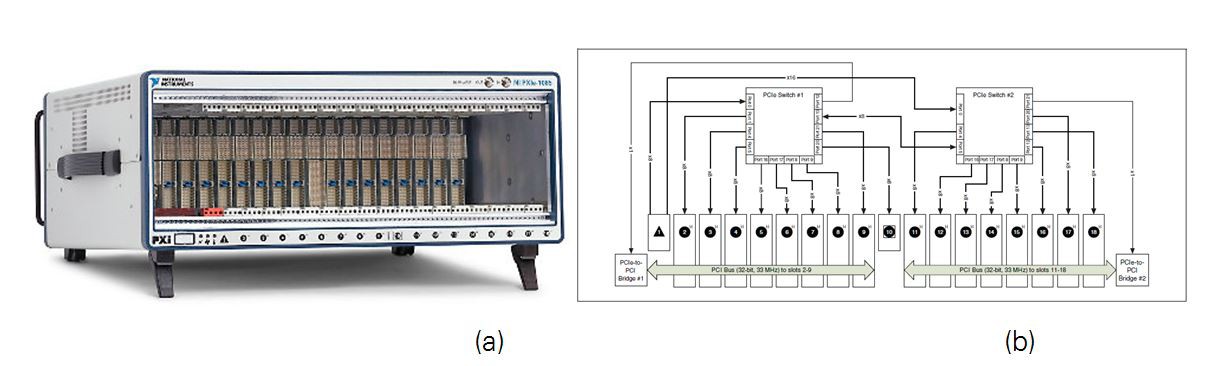

Бэ1. ДѓЙцФЃMIMOгІгУГЬађПђМмЯЕЭГВЮЪ§

ДѓЙцФЃMIMOЯЕЭГМмЙЙ

е§ШчЦфЫћЭЈбЖЭјТчЃЌДѓЙцФЃMIMOЯЕЭГгЩЛљеОЪеЗЂаХЛњЃЈBTSЃЉКЭгУЛЇЩшБИЃЈUEЃЉЛђепЪЧвЦЖЏгУЛЇЫљзщГЩЁЃ

ДѓЙцФЃMIMOЯЕЭГеЙЭћЗфЮбЭјТчЕФгІгУЃЌЦфЭЈГЃгЩЛљеОЪеЗЂаХЛњ(BTS)КЭгУЛЇЩшБИЃЈUEЃЉЛђвЦЖЏгУЛЇЫљЙЙГЩЁЃШЛЖјЃЌДѓЙцФЃMIMOГЙЕзИФБфСЫвдЭљашвЊХфжУДѓСПЕФBTSЬьЯпвдЭЌЪБИњЖрИігУЛЇЩшБИНјааЭЈбЖЕФДЋЭГЭиЦЫНсЙЙЁЃдкNIКЭТЁЕТДѓбЇКЯзїПЊЗЂЕФЯЕЭГжаЃЌЦфBTSВЩгУСЫУПгУЛЇЩшБИ10ИіЛљеОЬьЯпЕЅдЊЕФЯЕЭГЩшМЦвђЪ§ЃЌПЩЭЌвЛЪБМфЬсЙЉ10ИігУЛЇЃЌЖдетИі100ЬьЯпЛљеОНјааШЋДјПэЗУЮЪЕФФмСІЁЃУПгУЛЇЩшБИ10ИіЛљеОЬьЯпЕЅдЊЕФетвЛЯЕЭГЩшМЦвђЪ§вбОЪЙЕУжкЖрРэТлГЩЙћЕУЕНБЛжЄЪЕЁЃ

дквЛИіДѓЙцФЃMIMOЯЕЭГжаЃЌвЛзщгУЛЇЩшБИЭЌЪБЗЂЩфвЛзще§НЛЕМЦЕЕНЛљеОЪеЗЂаХЛњЃЈBTSЃЉЁЃЖјBTSЫљНгЪеЕФЩЯааСДТЗЕМЦЕОЭПЩБЛгУРДЙРМЦаХЕРОиеѓЁЃдкЯТааСДТЗЪБЯЖжаЃЌИУаХЕРЙРМЦМДБЛгУгкМЦЫуЯТааСДТЗаХКХЕФдЄБрТыЦїЁЃРэЯыЧщПіЯТЃЌетОЭЕМжТУПвЛИівЦЖЏгУЛЇДгЮоИЩШХЕФаХЕРЩЯЪеЕНЫљвЊДЋДяИјЫћУЧЕФаХЯЂЁЃдЄБрТыЦїЩшМЦЪЧвЛИіПЊЗХЕФбаОПСьгђЃЌЧвЪЪгУгкИїжжИїбљЕФЯЕЭГЩшМЦФПБъЁЃОйИіР§згЃЌдЄБрТыЦїПЩгУРДЩшМЦОЁПЩФмЕиЖдЦфЫћгУЛЇВЛВњЩњИЩШХЁЂзюаЁЛЏзмЗјЩфЙІТЪЃЌЛђепЪЧМѕЩйЫљЗЂЫЭЩфЦЕаХКХЕФЗхжЕЦНОљЙІТЪБШЁЃ

ДѓЙцФЃMIMOгІгУГЬађПђМмПЩгУгкКмЖрЕФХфжУгІгУжаЃЌЧвПЩжЇГж64ЕН128ЬьЯпИпДя20MHzЫВЪБЪЕЪБДјПэЃЌЭЌЪБжЇГжЖрИіЖРСЂгУЛЇЩшБИЭЌЪБЪЙгУЁЃетИіРрЫЦLTEЕФавщЪЙгУ2048ИіЕуЕФПьЫйИЕРявЖБфЛЛМЦЫуЃЈFFTЃЉКЭ0.5КСУыЕФЪБЯЖЃЌШчБэ1жаЫљЪОЁЃет0.5КСУыЕФЪБЯЖШЗБЃСЫзуЙЛЕФаХЕРвЛжТадЃЌДйНјСЫвЦЖЏВтЪдГЁОАжаЃЈЛЛОфЛАЫЕЃЌгУЛЇЩшБИЪЧдкдЫЖЏЕФЃЉЕФаХЕРЛЅвзадЁЃ

ДѓЙцФЃMIMOгВМўКЭШэМўзщГЩ

ЩшМЦвЛИіДѓЙцФЃMIMOЯЕЭГашвЊЫФИіЪєадЃК

СщЛюЕФШэМўЮоЯпЕчЃЌПЩгУгкНгЪмКЭЗЂЫЭЩфЦЕаХКХ

ЩфЦЕЩшБИжЎМфОЋШЗЕФЪБМфКЭЦЕТЪЭЌВН

ОпгаИпЭЬЭТСПКЭШЗЖЈадЕФзмЯпЃЌгУвдДЋЪфКЭЛуМЏКЃСПЕФЪ§Он

ИпадФмЕФДІРэФмСІЃЌгУвдТњзуЮяРэВуКЭНщжЪЗУЮЪПижЦЃЈMACЃЉжДааЪБЫљашЕФЪЕЪБадФмашЧѓ

РэЯыЧщПіЯТЃЌетаЉЕФЪєадПЩБЛПьЫйздЖЈвхвдТњзуИќЖрИќЙуЗКЕФбаЗЂашЧѓЁЃ

ЛљгкNIЦНЬЈЕФДѓЙцФЃMIMOгІгУГЬађПђМмНЋШэМўЮоЯпЕчЁЂЪБжгЗжХфФЃПщЁЂИпЪ§ОнЭЬЭТСПPXIЯЕЭГвдМАLabVIEWЯрНсКЯЃЌЬсЙЉСЫвЛИіОпгаТГАєадКЭШЗЖЈадЕФбаЗЂЫљЪЙгУЕФдаЭЩшМЦЦНЬЈЁЃетвЛВПЗжОЭОпЬхНтЪЭСЫЛљгкNIЕФДѓЙцФЃMIMOЛљеОКЭгУЛЇЩшБИжеЖЫжаЫљгУЕНЕФИїжжгВМўКЭШэМўВПЗжЁЃ

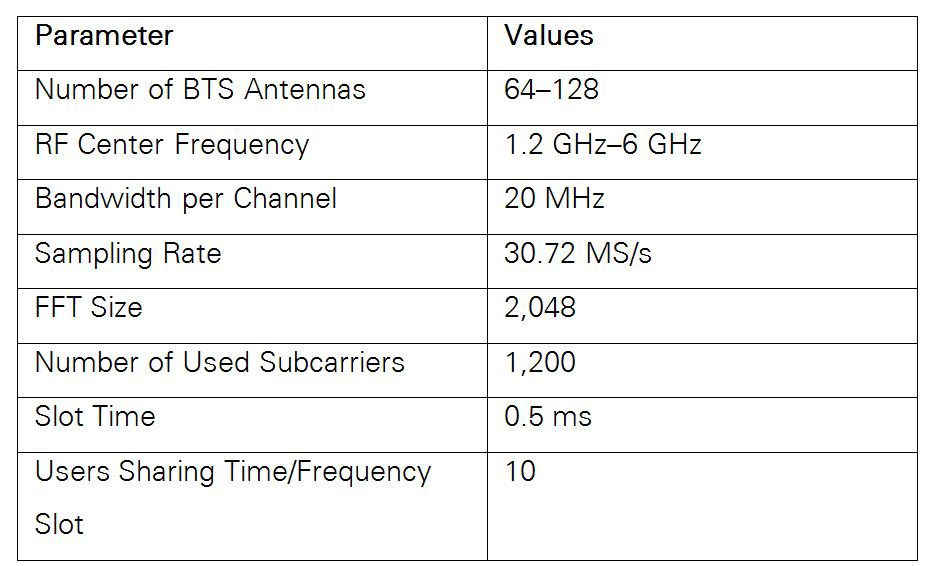

USRPШэМўЮоЯпЕч

USRP RIOШэМўЮоЯпЕчАќКЌСЫвЛИі2X2 MIMOМЏГЩЪеЗЂвЧКЭгУгкЬсИпЛљДјДІРэЫйЖШЕФИпадФмXilinx

Kintex-7 FPGAЃЌЫљгаЕФетаЉгВМўОљЗтзАдквЛИі0.5UЕФЛњМмАВзАЪНЭтПЧФкЁЃЫќНЋжїЛњПижЦЦїЭЈЙ§PCI

Express x4змЯпСЌНгЕНЯЕЭГПижЦЦїЃЌЮЊЬЈЪНЕчФдЛђепPXI ExpressжїЛњЬсЙЉИпДя800MB/sЕФЪ§ОнДЋЪфЫйЖШЃЈЛђЪЧЭЈЙ§ExpressCardЮЊБЪМЧБОЕчФдЬсЙЉ200MB/sЕФЫйЖШЃЉЁЃЭМ2ЬсЙЉСЫUSRP

RIOгВМўЕФГЬађПђЭМИХРРЁЃ

USRP RIOЛљгкLabVIEWПЩжиХфжУI/O (RIO)МмЙЙЃЌНсКЯСЫПЊЗХЕФLabVIEWЯЕЭГЩшМЦШэМўКЭИпадФмЕФгВМўФЃПщЃЌДгЖјДѓДѓМђЛЏСЫПЊЗЂЁЃИпЖШЕФШэгВМўМЏГЩНЕЕЭСЫЯЕЭГМЏГЩЕФФбЖШЃЌетЖдгкШчДЫЙцФЃЕФЯЕЭГРДЫЕОпгаживЊвтвхЃЌЪЙЕУбаЗЂШЫдБПЩвдМЏжаИќЖрЕФОЋСІдкбаЗЂЩЯЁЃОЁЙмећИіNIгІгУГЬађПђМмШэМўЖМЪЧЛљгкLabVIEWПЊЗЂЕФЃЌЕЋLabVIEWПЩвдМЏГЩ.mНХБОЮФМўЁЂANSI

C/C++МАHDLЕШЦфЫћБрГЬЩшМЦгябдЕФIPЃЌЭЈЙ§ДњТыжигУРДЬсИпПЊЗЂаЇТЪЁЃ

ЭМ2. USRP RIOгВМў(a) вдМАЯЕЭГПђЭМ (b)

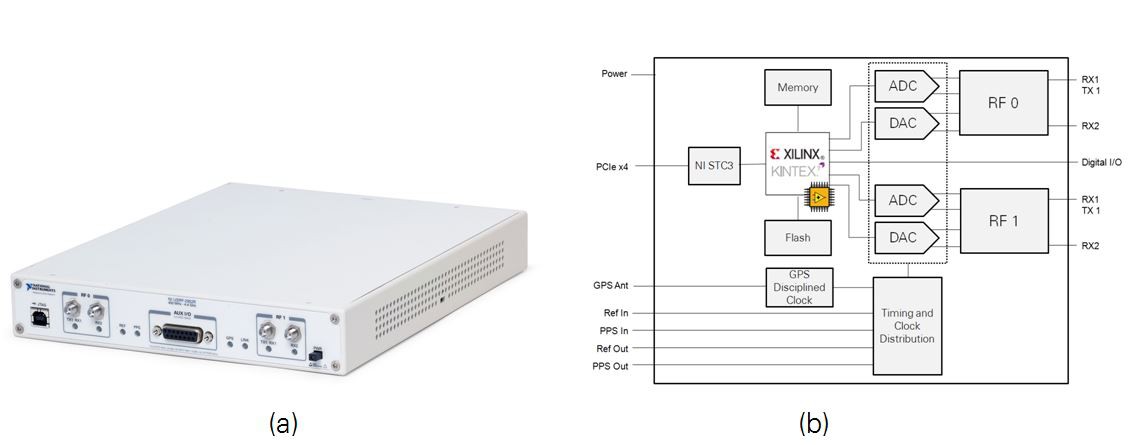

PXI ExpressЛњЯфБГАх

ДѓЙцФЃMIMOгІгУГЬађПђМмЪЙгУPXIe-1085ЛњЯфЃЌетЪЧвЛПюИпМЖЕФ18ВлPXIЛњЯфЃЌЦфЪЙгУЕФPCI

ExpressЕкЖўДњММЪѕЪЙЕУУПвЛИіВхВлЖМПЩгУгкИпЭЬЭТСПЁЂЕЭбгГйадЕФгІгУЩшМЦЁЃИУЛњЯфгЕгаУПВхВлИпДя4

GB/sЕФзЈгУДјПэЃЌвдМА12 GB/sЕФЯЕЭГДјПэЁЃЭМ3ЫљеЙЪОЕФЪЧЫЋПЊЙиЕФБГАхМмЙЙЭМЁЃЖрPXIЛњЯфФмЭЈЙ§ОеЛЈСДЛђепаЧаЮСДЕФХфжУЗНЪНРЉеЙДюНЈИпЭЈЕРЪ§ЕФЯЕЭГЁЃ

ЭМ3. 18ВлPXIe-1085ЛњЯф(a) вдМАЯЕЭГПђЭМ (b)

ИпадФмПЩжиХфжУFPGAДІРэФЃПщ

ДѓЙцФЃMIMOгІгУГЬађПђМмЪЙгУСЫFlexRIO FPGAФЃПщРДЬэМгСщЛюЕФИпадФмЕФДІРэФЃПщЃЌетаЉФЃПщЪЧЛљгкPXIаЮЪНЃЌВЂПЩЪЙгУLabVIEW

FPGAФЃПщНјааБрГЬЁЃPXIe-7976R FPGAФЃПщПЩвдЖРСЂЪЙгУЃЌЫќЬсЙЉСЫТпМЕЅдЊЗсИЛЧвПЩЖЈжЦЕФXilinx

Kintex-7 410TЃЌЭЈЙ§PCI Express Gen 2 x8змЯпгыPXI ExpressБГАхЯрСЌЁЃДЫЭтРћгУИпадФмЕФЩфЦЕЪеЗЂЦїЁЂЛљДјФЃЪ§зЊЛЛЦї/

Ъ§ФЃзЊЛЛЦївдМАИпЫйЪ§зжI/OЃЌДѓВПЗжВхШыЪНFlexRIOЪЪХфЦїФЃПщПЩНјвЛВНРЉеЙИУЦНЬЈЕФI/OЙІФмЁЃ

ЭМ4. PXIe-7976R FlexRIOФЃПщ(a) вдМАЯЕЭГПђЭМ (b)

8ЭЈЕРЪБжгЭЌВН

Ettus ResearchЙЋЫОЕФOctoClock 8ЭЈЕРЪБжгЗжХфФЃПщЬсЙЉСЫЖдИпДя8ЬзUSRPЩшБИЪБМфКЭЦЕТЪЕФЭЌВНЃЌЭЈЙ§дкЦЅХфГЄЖШаХКХжаЗХДѓКЭЗжИювЛИіЭтВП10MHzВЮПМЪБжгКЭУПУыТіГхЪ§ЃЈPPSЃЉаХКХЕФАЫжжЗНЗЈРДЪЕЯжЭЌВНЁЃOctoClock-GЪЙгУФкВПМЏГЩЕФGPSЫјЖЈОЇЬхеёЕДЦїЃЈGPSDOЃЉзїЮЊФкВПЪБМфКЭЦЕТЪВЮПМЁЃЭМ4ЯдЪОЕФЪЧOctoClock-GЕФЯЕЭГИХЭМЁЃЧАУцАхЩЯЕФвЛИіПЊЙигУРДЙЉгУЛЇбЁдёЪЙгУФкВПЪБжгдДЛЙЪЧЭтВПВЮПМЪБжгЁЃгаСЫOctoClockФЃПщЃЌгУЛЇОЭПЩвдМђЕЅЕиДюНЈГіMIMOЯЕЭГЃЌВЂгыЦфЫћПЩФмЩцМАЕНMIMOбаОПЕФИпЭЈЕРЪ§ЯЕЭГЛђвЛЦ№аЭЌЙЄзїЁЃ

ЭМ5. OctoClock-GФЃПщ(a) вдМАЯЕЭГПђЭМ (b)

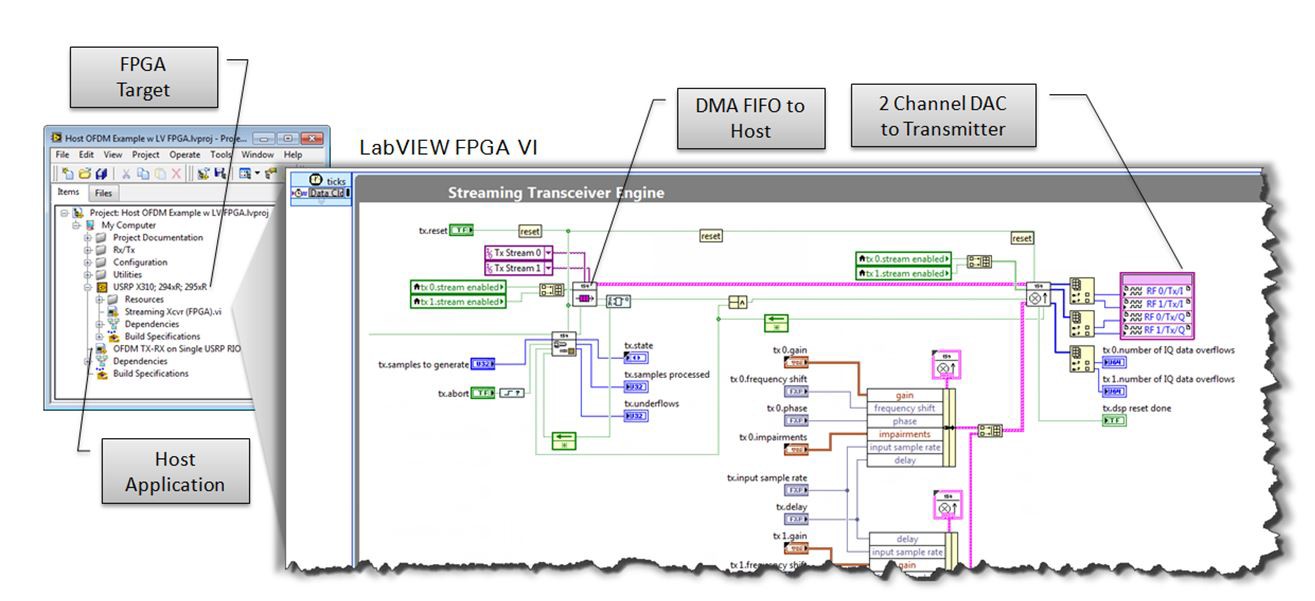

LabVIEWЯЕЭГЩшМЦЛЗОГ

LabVIEWЬсЙЉСЫвЛИіМЏГЩЛЏЕФЙЄОпСДЃЌгУвдЙмРэЯЕЭГМЖШэгВМўЯИНкЃЛдкЭМаЮЛЏгУЛЇНчУцЩЯПЩЪгЛЏЯЕЭГаХЯЂЃЌПЊЗЂЭЈгУДІРэЦїЃЈGPPЃЉЁЂЪЕЪБКЭFPGAДњТыЃЛвдМАНЋДњТыВПЪ№ЕНбаЗЂВтЪдЬЈЩЯЁЃНшжњLabVIEWЃЌгУЛЇПЩвдЧсЫЩМЏГЩЦфЫћБрГЬЛЗОГжаЕФДњТыЃЌБШШчANSI

C/C++ПЩЭЈЙ§ЕїгУПтНкЕуКЏЪ§МЏГЩЁЂVHDLПЩЭЈЙ§IPМЏГЩНкЕуМЏГЩЁЂЩѕжС.mЮФМўНХБОвВПЩЭЈЙ§LabVIEW

MathScriptЪЕЪБФЃПщНјааМЏГЩЁЃетЪЙЕУПЊЗЂОпгаИпЖШПЩЖСадКЭПЩЖЈжЦадЕФИпадФмЩшМЦБфЕУПЩФмЁЃЫљгаЕФгВМўКЭШэМўдкЭЌвЛИіLabVIEWЯюФПжаНјааЙмРэЃЌЪЙЕУбаОПШЫдБФмЙЛНЋДњТыВПЪ№жСЫљгаДІРэЕЅдЊВЂдкЭГвЛЕФЛЗОГжадЫааИїжжВтЪдГЁОАЁЃДѓЙцФЃMIMOгІгУГЬађПђМмВЩгУLabVIEWНјааПЊЗЂЪЧвђЮЊLabVIEWЬсЙЉЕФИпаЇТЪМАЦфЛљгкLabVIEW

FPGAФЃПщБрГЬКЭПижЦI/OЕФФмСІЁЃ

ЭМ6. LabVIEWЯюФПКЭLabVIEW FPGAгІгУГЬађ

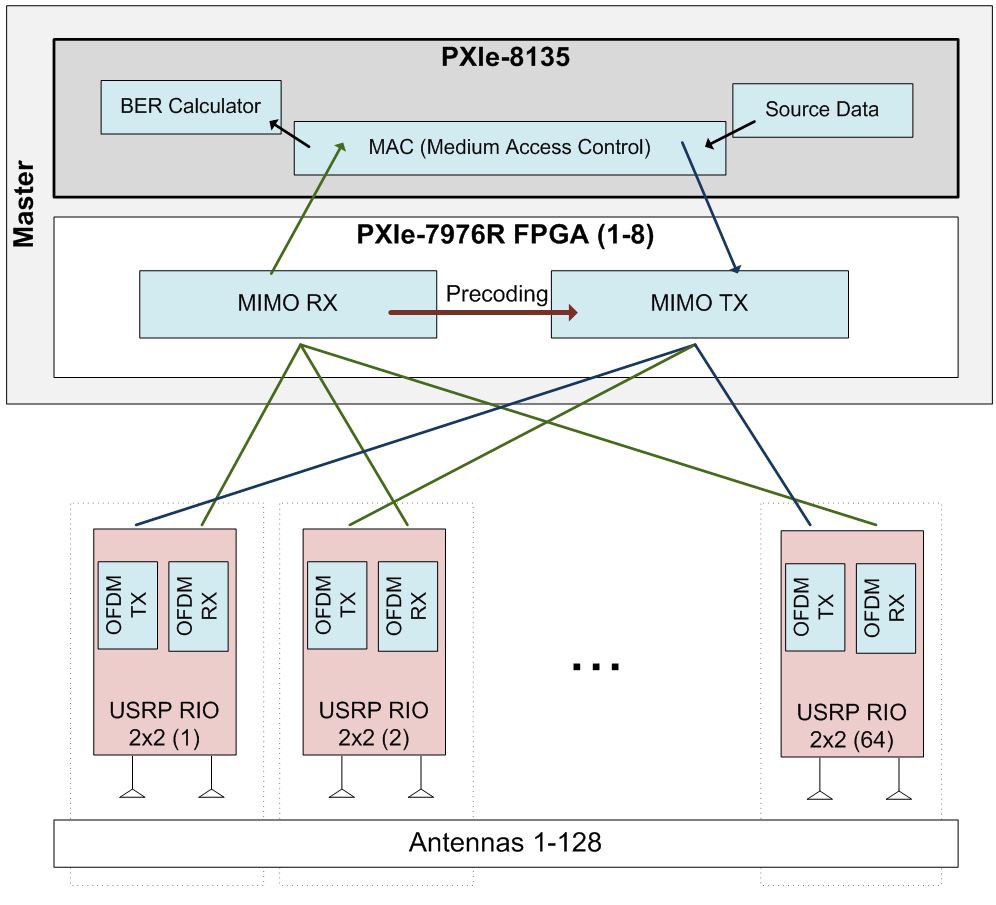

ДѓЙцФЃMIMO BTSгІгУГЬађПђМмМмЙЙ

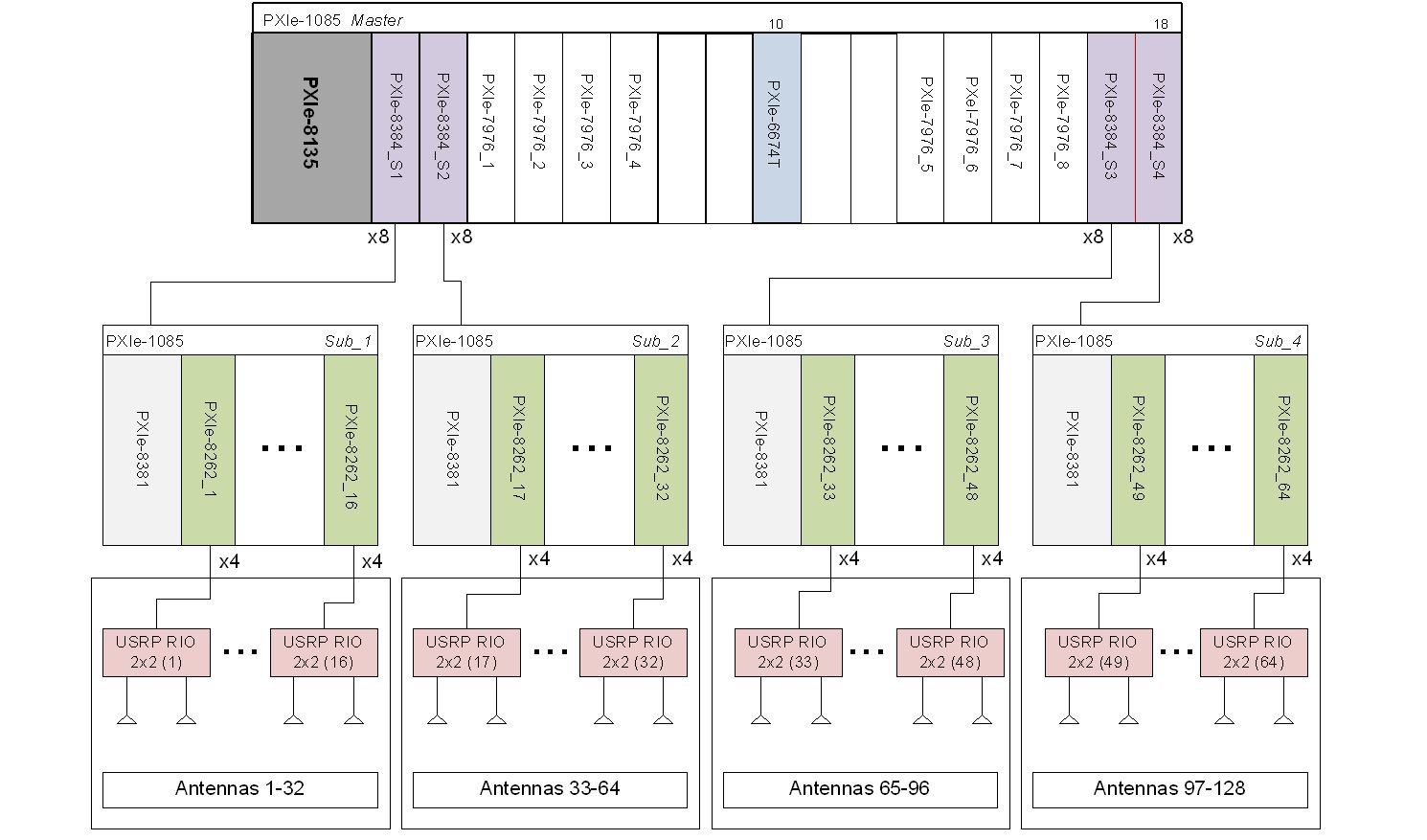

вдЩЯШэгВМўЦНЬЈзщМўЯрНсКЯМДПЩЙЙГЩПЩДгМИИљЬьЯпРЉеЙЕНГЌЙ§128ИљЭЌВНЬьЯпЕФВтЪдЬЈЁЃЮЊСЫБугкгУЛЇРэНтЃЌБОММЪѕАзЦЄЪщНіЫЕУїСЫ64ЁЂ96вдМА128ЬьЯпХфжУЁЃ128ЬьЯпЯЕЭГАќКЌСЫ64ИіЫЋЭЈЕРUSRP

RIOЩшБИЃЌЭЈЙ§аЧаЮМмЙЙСЌНгЕНЫФИіPXIЛњЯфЩЯЁЃжїЛњЯфЛуМЏЪ§ОнКѓгЩFPGAКЭЛљгкЫФКЫIntel

i7ДІРэЦїЕФPXIПижЦЦїНјааМЏжаДІРэЁЃ

дкЭМ7жаЃЌжїЛњЯфЪЙгУСЫPXIe-1085ЛњЯфзїЮЊжїЪ§ОнЛуМЏНкЕуКЭЪЕЪБаХКХДІРэв§ЧцЁЃPXIЛњЯфЬсЙЉСЫ17ИіВхВлЃЌдЄСєИјЪфШыЪфГіЩшБИЁЂЖЈЪБКЭЭЌВНФЃПщЁЂгУгкЪЕЪБаХКХДІРэЕФFlexRIO

FPGAФЃПщвдМАСЌНгДгЛњЯфЕФРЉеЙФЃПщЁЃ128ЬьЯпЕФДѓЙцФЃMIMO BTSЯЕЭГашвЊЗЧГЃИпЕФЪ§ОнЭЬЭТСПРДЛуМЏКЭЪЕЪБДІРэ128ИіЭЈЕРЗЂЫЭКЭНгЪеЕФI-Qе§НЛаХКХЃЌЖдДЫPXIe-1085ЛњЯфЪЧзюМббЁдёЃЌЫќжЇГжЭЬЭТСПИпДя3.2GB/sЕФPCI

Gen 2 x8Ъ§ОнСДТЗЁЃ

ЭМ7. ЛљгкPXIКЭUSRP RIOЕФПЩРЉеЙДѓЙцФЃMIMOЯЕЭГПђЭМ

дкжїЛњЯфЕквЛВлЮЛЕФPXIe-8135 ЪЕЪБПижЦЦїЛђЧЖШыЪНМЦЫуЛњЕЃШЮзХжабыЯЕЭГПижЦЦїЕФНЧЩЋЁЃPXIe-8135

ЪЕЪБПижЦЦїОпга2.3GHzЫФКЫi7-3610QEДІРэЦїЃЈЕЅКЫЯТзюДѓПЩГЌЦЕЬсЩ§ЕН3.3GHzЃЉЁЃжїЛњЯфФкЛЙАќКЌ4ИіPXIe-8384ЃЈS1ЕНS4ЃЉНгПкФЃПщЃЌгУгкНЋзгЛњЯфСЌНгЕНжїЯЕЭГЁЃжїДгЛњЯфМфЭЈЙ§MXIзмЯпНјааСЌНгЃЌШЗЧаРДЫЕЪЧPCI

ExpressGen 2 x8змЯпЃЌЮЊжїДгНкЕужЎМфЬсЙЉСЫИпДя3.2GB/sЕФЪ§ОнДЋЪфЭЬЭТСПЁЃ

ЯЕЭГЛЙАќРЈСЫ8ИіPXIe-7976R FlexRIO FPGAФЃПщЃЌгУРДТњзуДѓЙцФЃMIMOЯЕЭГжаЕФЪЕЪБаХКХДІРэашЧѓЁЃВхВлЕФЮЛжУХфжУЪОР§еЙЪОСЫжїЛњЯфжаЕФFPGAПЩвдЭЈЙ§МЖСЊЗНЪНСЌНгЃЌвджЇГжУПвЛИізгНкЕуЕФЪ§ОнДІРэашЧѓЁЃУПИіFlexRIOФЃПщПЩвдЭЈЙ§БГАхвдЕЭгк5ІЬsЕФбгГйКЭИпДя3GB/sЕФЭЬЭТСПгыЦфЫћFlexRIOФЃПщЛђЫљгаUSRP

RIOНјааЪ§ОнЭЈаХЁЃНјааНгЪеЛђЗЂЫЭЪ§ОнЃЌВЂЧвбгЪБаЁгкЧвЭЬЭТСПЁЃ

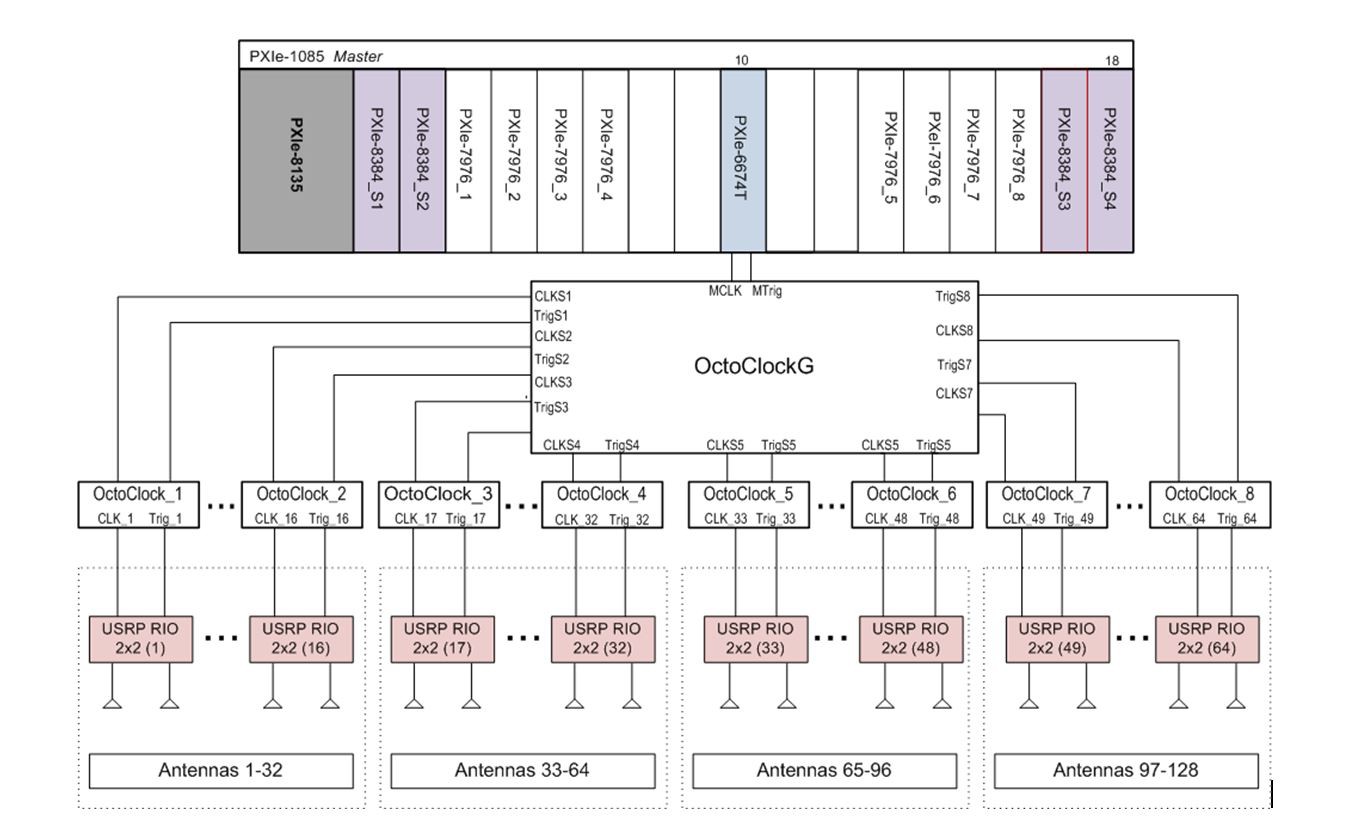

ЖЈЪБКЭЭЌВН

ЖЈЪБКЭЭЌВНЖдгкШЮКЮвЛИіашвЊВПЪ№ДѓСПЮоЯпЕчЩшБИЕФЯЕЭГРДЫЕЖМЪЧжСЙиживЊЕФЃЌЖдгкДѓЙцФЃMIMOЯЕЭГРДЫЕвВЪЧШчДЫЁЃBTSЯЕЭГЙВЯэвЛИіЭЈгУ10MHzВЮПМЪБжгКЭвЛИіЪ§зжДЅЗЂаХКХЃЌгУгкЦєЖЏУПИіЮоЯпЕчЩшБИЕФЪ§ОнВЩМЏКЭЩњГЩЃЌвдШЗБЃећИіЯЕЭГжЎМфЕФЯЕЭГМЖЭЌВНЃЈВЮМћЭМ8ЃЉЁЃPXIe-6674TЖЈЪБКЭЭЌВНФЃПщОпгавЛИіКуЮТОЇЬхеёЕДЦїЃЈOCXOЃЉЃЌЮЛгкжїЛњЯфЕФЕк10ВлЃЌПЩЩњГЩвЛИіЗЧГЃЮШЖЈЧвОЋШЗЕФ10MHzВЮПМЪБжгЃЈ50

ppbЕФОЋШЗЖШЃЉВЂЬсЙЉвЛИіЪ§зжДЅЗЂаХКХРДЪЕЯжгыOctoClock-GЪБжгЗжХфФЃПщЕФЭЌВНЁЃжЎКѓЃЌOctoClock-GЬсЙЉВЂЛКДцетвЛИі10MHzВЮПМЪБжгаХКХЃЈMCLKЃЉКЭДЅЗЂаХКХЃЈMTrigЃЉЕНOctoClockФЃПщЃЌвдвЛЖдАЫЕФБШР§ЬсЙЉИјUSRP

RIOЩшБИЃЌДгЖјШЗБЃЫљгаЬьЯпЙВЯэ10MHzЕФВЮПМЪБжгКЭжїДЅЗЂаХКХЁЃетРяЬсЕНЕФПижЦМмЙЙПЩОЋШЗЕиПижЦУПвЛИіЮоЯпЕчЩшБИ/ЬьЯпЕЅдЊЁЃ

ЭМ8. ДѓЙцФЃMIMOЯЕЭГЪБжгЗжХфПђЭМ

Бэ2ЬсЙЉСЫ64ЁЂ96КЭ128ЬьЯпЯЕЭГЕФЛљеОХфМўЧхЕЅПьЫйВЮПМЁЃЫќАќРЈСЫШчЭМ1жаЫљЪОЕФгВМўЩшБИКЭЩшБИСЌНгЯпРТЁЃ

Бэ2. ДѓЙцФЃMIMOЛљеОХфМўЧхЕЅ

ЛљеОЪеЗЂаХЛњ(BTS)ШэМўМмЙЙ

ЛљеОгІгУГЬађПђМмШэМўЪЧИљОнБэ1жаЫљСаЕФЯЕЭГВЮЪ§ФПБъЖјЩшМЦЕФЃЌЦфжаUSRP

RIOжаЕФFPGAИКд№ЮяРэВуЕФе§НЛЦЕЗжИДгУЃЈOFDMЃЉДІРэЃЌ PXIжїЛњЯфжаЕФFPGAИКд№MIMOЮяРэВуДІРэЁЃИќИпВуЕФНщжЪЗУЮЪПижЦКЏЪ§дђдкPXIПижЦЦїЩЯЕФгЂЬиЖћЭЈгУДІРэЦїЃЈGPPЃЉжадЫааЁЃИУЯЕЭГМмЙЙПЩдЪаэНјааДѓСПЕФЪ§ОнДІРэЧвОпгазуЙЛЕЭЕФбгЪБадРДЮЌГжаХЕРЛЅвзадЁЃдЄБрТыЕФВЮЪ§жБНгДгНгЪеЛњДЋЪфЕНЗЂЩфЛњЃЌвдЛёЕУзюИпЕФЯЕЭГадФмЁЃ

ЭМ9. ДѓЙцФЃMIMOЯЕЭГЪ§ОнКЭДІРэПђЭМ

ДгЬьЯпПЊЪМЃЌOFDMЮяРэВуЕФДІРэдкFPGAжаЪЕЯжЃЌетбљМЦЫуЧПЖШзюДѓЕФДІРэОЭПЩдкЬьЯпИННќжДааЁЃжЎКѓЃЌМЦЫуНсЙћгыMIMOНгЪеЛњЃЈMIMO

RXЃЉЕФIPКЏЪ§ЯрНсКЯЃЌДгЖјЕУЕНУПИігУЛЇКЭУПИіИБдиВЈЕФаХЕРаХЯЂЁЃШЛКѓдйНЋМЦЫуЕУЕНЕФаХЕРВЮЪ§ДЋЪфЕНMIMOЗЂЩфЖЫЃЈMIMO

TXЃЉНјаадЄБрвыЃЌНЋФмСПМЏжаЕНЕЅвЛгУЛЇЕФЛиТЗжаЁЃЫфШЛНщжЪЗУЮЪПижЦЕФФГаЉВПЗжЪЧдкFPGAжаЪЕЯжЃЌЕЋЪЧЦфДѓВПЗжЕФЪЕЯжЛЙгаЦфЫћИќИпВуЕФвЛаЉДІРэЛЙЪЧдкЭЈгУДІРэЦїЃЈGPPЃЉжаЪЕЯжЕФЁЃЯЕЭГУПИіНзЖЮЪЙгУЕФЬиЖЈЫуЗЈЪЧЕБЧАвЛИіЛюдОЕФбаОПСьгђЁЃећИіЯЕЭГПЩЪЙгУLabVIEWКЭLabVIEW

FPGAНјаажиаТХфжУЁЊЁЊдкЬсЩ§ЫйЖШЕФЭЌЪБЮоашЮўЩќГЬађЕФПЩЖСадЁЃ

гУЛЇЩшБИ

УПвЛИігУЛЇЩшБИДњБэвЛЬЈЪжЛњЛђепЪЧЦфЫћЕЅШыЕЅГіЃЈSISOЃЉЛђОпга2x2

MIMOЮоЯпЙІФмЕФЮоЯпЩшБИЁЃгУЛЇЩшБИЃЈUEЃЉЕФдаЭЪЕбщЪЙгУСЫОпгаМЏГЩЪНGPSDOЕФUSRP

RIOЃЌВЂЭЈЙ§вЛИљPCI ExpressзЊExpressCardЯпРТСЌНгЕНвЛЬЈБЪМЧБОЕчФдЁЃGPSDOЕФживЊаддкгкЫќЬсЙЉСЫИќИпЕФЦЕТЪОЋШЗадЃЌЖјЧвШчЙћНЋРДНјааЯЕЭГРЉеЙгаашвЊЪБЃЌвВПЩЬсЙЉЭЌВНКЭЛёШЁЕиРэЮЛжУЕФФмСІЁЃвЛИіЕфаЭЕФВтЪдЬЈЪЕЯжЛсЭЈГЃАќКЌЖрИігУЛЇЩшБИЕФЯЕЭГЃЌЦфжаУПвЛЬЈUSRP

RIOПЩЯрЕБгквЛЬЈЛђСНЬЈгУЛЇЩшБИЁЃдкгУЛЇЩшБИЩЯВПЪ№ЕФШэМўгыBTSЕФШэМўЗЧГЃЯрЫЦЃЌШЛЖјЫќжЛЪЧзїЮЊвЛИіЕЅЬьЯпЯЕЭГЪЕЯжЃЌЫљвдНЋЫќЕФЮяРэВуЗХдкUSRP

RIOжаЕФFPGAЩЯЪЕЯжЃЌЖјАбНщжЪЗУЮЪПижЦВуЃЈMACЃЉЗХдкжїЛњPCЩЯЪЕЯжЁЃ

ЭМ10. ЪЙгУБЪМЧБОЕчФдКЭUSRP RIOНјааЕфаЭЕФгУЛЇЩшБИДюНЈ

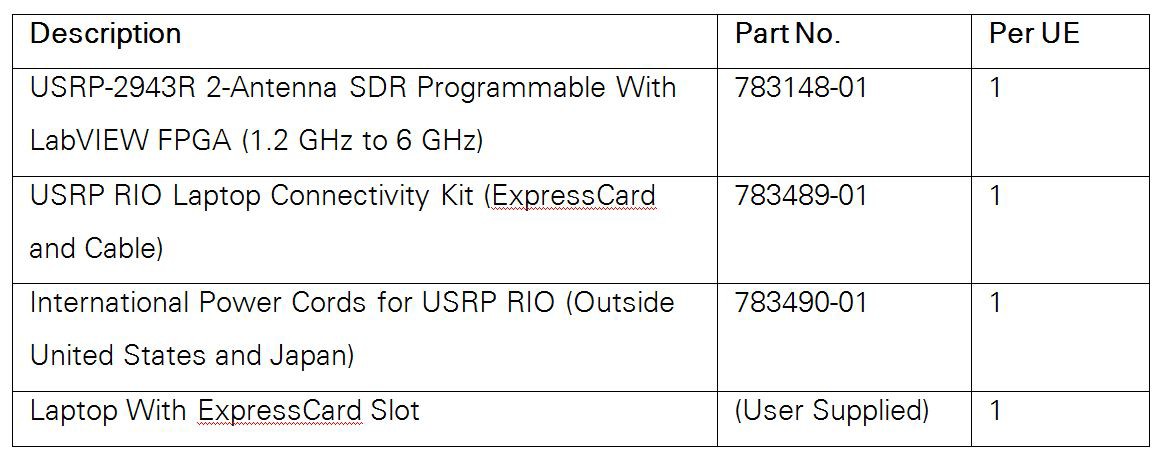

Бэ3ЬсЙЉСЫдквЛИіЕЅгУЛЇЩшБИЯЕЭГжаЪЙгУЕФХфМўЧхЕЅЁЃЫќАќКЌСЫЭМ10жаЫљЪОЕФгВМўЩшБИКЭСЌНгЯпРТЁЃЛђепЃЌШчЙћбЁдёЬЈЪНЕчФдзїЮЊгУЛЇЩшБИПижЦЦїЪБЃЌПЩвдЪЙгУPCI

ExpressСЌНгЁЃ

Бэ3. гУЛЇЩшБИХфМўЧхЕЅ

НсТл

NIММЪѕЭЈЙ§LabVIEWЯЕЭГЩшМЦШэМўвдМАUSRP RIOКЭPXIЦНЬЈЕФзщКЯе§дкГЙЕзИФИяИпЖЫПЦбаЯЕЭГЕФдаЭЩшМЦЗНЗЈЁЃБОЮФеТНщЩмСЫвЛжжДюНЈДѓЙцФЃЖрШыЖрГіЃЈMIMOЃЉЯЕЭГЕФПЩааЗНЗЈРДНјвЛВНЭЦНј5GЕФбаОПЁЃИУгІгУГЬађПђМмжаЪЙгУЕФИїжжNIММЪѕЕФЖРЬизщКЯЪЕЯжСЫДѓСПЮоЯпЕчЩшБИдкЪБМфКЭЦЕТЪЩЯЕФЭЌВНЃЌЖјЧвPCI

ExpressММЪѕвВЬсЙЉСЫвд15.7GB/sЫйТЪЩЯЯТааДЋЪфКЭЛуМЏI-QаХКХЫљашЕФЭЬЭТСПЁЃFPGAЕФЪ§ОнСїЩшМЦЗНЪНМђЛЏСЫЮяРэВуКЭНщжЪЗУЮЪПижЦВуЩЯЕФИпадФмДІРэЃЌТњзуЪЕЪБДІРэЕФвЊЧѓЁЃ

ЮЊБЃжЄетаЉВњЦЗФмТњзуЮоЯпММЪѕбаОПШЫдБЕФЬиЖЈашЧѓЃЌNIе§дкЛ§МЋЕигыаавЕСьЯШЕФбаЗЂШЫдБКЭТЁЕТДѓбЇЕШЪРНчУћаЃНјааКЯзїЁЃетаЉКЯзїЭЦЖЏСЫвЛаЉбаОПСьгђШЁЕУСюШЫаЫЗмЕФНјеЙЃЌЭЌЪБвВДйНјСЫашвЊКЭе§дкЪЙгУДѓЙцФЃMIMOгІгУГЬађПђМмЕШЙЄОпЕФЙЄГЬЪІКЭПЦбаШЫдБжЎМфЕФЗНЗЈЁЂIPКЭзюМбЪЕМљЙВЯэЁЃ

|