|

Ƕ��ʽӦ��ϵͳ��ư���Ӳ��ƽ̨������ƽ̨�����֡�ǰ������Ƕ��ʽ������/������Ϊ���ĵ�Ӳ��ϵͳ����������Χ��Ƕ��ʽ����ϵͳ����������ϵͳ����������������ܲ��ɷֵģ�������Ҫ�����֮�����Ȩ���Ż�������ʵ��Ӧ�ý��������Ͳü���

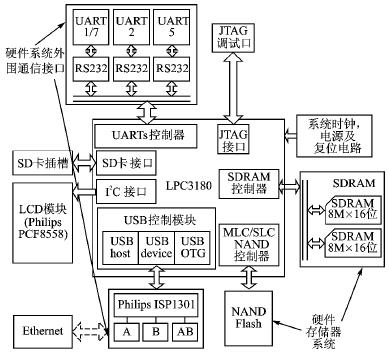

����arm926EJS�ں˵�LPC3180�ڲ������˷ḻ��������Դ��ΪǶ��ʽϵͳ�����ṩ�˺ܴ����ƿռ䡣���Ľ�ϱ��߿���LPC3180Ƕ��ʽƽ̨��ʵ�ʾ��飬��������ܸ�ϵͳ��ʵ�֡��ṹ��ɺ�ʵ������

1 LPC3180оƬ���Խ���

LPC3180��Philips��˾���Ƴ���һ��ARM9��������������90nm���ռ�����Ƭ�ڼ���ARM9EJS�������ںˣ����и������ܡ����ĵ����ԣ���ʹ���ںܶ�Թ������е�Ƕ��ʽӦ�ó���������ʹ�ø����ܵ�arm9��������LPC3180�ں�����������ѹΪ1.2V���ڵ���ģʽ�¿ɽ���

0.9 V��ͬʱ��LPC3180��Ϊһ�����͵�32λ���������������Ի�������

- Ƭ�ڼ�����������(VFP)Э��������LPC3180�ĸ������㵥Ԫ��3����������ˮ�ߣ�֧�ֲ��е����Ȼ�˫���ȸ����/������/���Լ����ۻ����㣬��ȫ����IEEE754���������ڸ��ٸ������㳡�ϡ�

- Ƭ�ڼ���USB OTG����ģ�飬ͬʱ֧�����ЯUSB���豸��USB������������������PDA���������ʹ�ӡ�����豸ֱ��������������PC�����롣

- LPC3180���ö���AHB����ϵͳ��Ϊ������ģ���ṩ���������ߣ�����CPU��ָ�����ߺ��������ߡ�2��DMA���������������Լ�1��USB�������������ߡ�

LPC3180���ڲ��ܹ���ͼ1��ʾ��

ͼ1 LPC3180�ڲ��ܹ�

LPC3180�������������� �ڲ�����MLC/SLCNAND��������SDR/DDR

SDRAM��������SD ���ӿڣ�UART��SPI��I2C��Χͨ��ģ�飬�Լ�����/���붨ʱ����RTC�����Ź���ʱ����10λADC����������ģ�顣

2 Ӳ��ƽ̨���

��LPC3180Ϊ���ĵ�Ӳ��ƽ̨��ƿ����ͼ2��ʾ��

ͼ2 LPC3180Ӳ��ƽ̨��ƿ�ͼ

��1�� �洢��ϵͳ

NAND Flash�洢����ͨ��LPC3180�ڲ����ɵ�MLC/SLC

NAND������ֱ����Ӷ༶�� NAND Flash��������ϵͳѡ��ST NAND256R3A����32

MB�洢�ռ��������ϵͳ��������Ƕ��ʽ����ϵͳ�ں˺��ļ�ϵͳ�Ĵ�СҪ��

SDRAM�洢����ϵͳѡ��2Ƭ16λMICRON SDRAM����������32λSDRAM�洢��ϵͳ��

32 MB SDRAM�ռ䣬������Ƕ��ʽ����ϵͳ�Լ��ϲ�Ӧ�ó��������Ҫ��

SD����ۡ�ϵͳͨ��LPC3180�ڲ����ɵ�SD���ӿڣ��ṩSD����ۣ�������SD�洢����������Ϊ�ⲿ�洢�ռ䡣

��2�� ��Χͨ�Žӿ�

UART�ӿڡ�LPC3180�ڲ������˱�UARTģ�����UARTģ�飬����550��ҵ����ϵͳ������UART1/7��UART2��UART5������ʵ�ֻ����Ĵ���ͨ�Ź��ܣ�ͬʱ��UART5������ϵͳ����ʱ���ⲿ�������ء�

USB�ӿڡ�LPC3180�ڲ�������USB host��USB device�Լ�

USB OTG��������ͨ���ⲿUSB�շ�ģ��Philips ISP1301���� USB host�ӿ�A��USB

device�ӿ�B�Լ�USB OTG�ӿ� AB��

��3�� ������Χģ��

ϵͳͨ��I2C�ӿ�������һ�������ַ���LCD��ʾģ�飬����Ӧ�ó������н����ʾ��ͬʱ��Ϊ�˼�Ӳ��ϵͳ��ƣ�ϵͳ����̫��ģ��ͨ��

USB host�ӿ�A��������ʽʵ��������

3 ϵͳ�ؼ�ģ�����

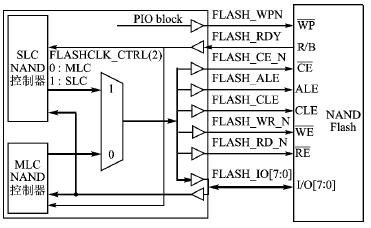

3.1 NAND Flash�洢��ģ��

LPC3180�ڲ�������MLC/SLC NAND��������ͨ���ⲿ���ſ�ֱ����Ӷ༶��NAND

Flash ��������ͼ3��ʾ����Ҫע�����MLC��SLC NAND������ͨ�����Ÿ��ã�ʹ����ͬ�Ľӿ���

NAND Flash��������ͬһʱ��ֻ������������һ���������������ϵͳ�ϵ�����ͨ������FLASH_CTRL�Ĵ���ѡ��Ҫʹ�õ�NAND��������������״̬ʱ��Ҳ��ͨ��д�Ĵ����ر�NAND���������Խ����ġ�NAND

Flash�洢��ģ��������ϵͳ��Ҫ�ľ�̬���ݴ洢�ռ䣬���ڴ洢ϵͳ���������еļ��س��������LPC3180ϵͳ������DZز����ٵġ�

ͼ3 NAND Flash�ӿ�����ͼ

3.2 USB�ӿ�ģ��

LPC3180�ڲ�����USB����ģ�飬��������USB�����㣬ϵͳͨ�����USB�շ�ģ��ISP1301ʵ��USB��������ӿڡ�ͼ4��USB�ӿ�����ͼ��LPC3180�ڲ�ͨ��AHB���豸��������USB���������ɹ�����ȫ��(12

Mb/s)�͵��� (1.5 Mb/s)����ģʽ�¡�

ͼ4 USB�ӿ�����ͼ

4 ����ϵͳ���

����ϵͳ��ɰ���ϵͳ��������Bootloader��Ƕ��ʽ����ϵͳ�Լ��ϲ�Ӧ�ó�������Bootloader�������ڲ���ϵͳ֮ǰ������������Ҫ���������ϵͳ����֮ǰ��Ҫ��Ӳ����ʼ���Ͳ���ϵͳ���أ�����ϵͳ������Ƕ��ʽƽ̨�ĺ��ij�����Ҫ�����Ǹ�Ч�ع����ͷ���ײ�Ӳ����Դ����Ϊ�ϲ�Ӧ�ó����ṩ��Ӳ��ϸ���ص�ϵͳ���ýӿڡ�

����ϵͳ��Ʊ�����Ӳ��ƽ̨���ܽ�ϡ�LPC3180����NAND Flash��Ϊ����ϵͳ�ij���洢������ϵͳ����ʱͨ��Ƭ��

ROM��bootstrap����,��NAND Flash���ز�ִ���ⲿ����������ʵ������ϵͳ���������衣��ˣ���������ϵͳ��ȡ��ͼ5��ʾ����ƽṹ��

ͼ5 ����ϵͳ�ṹ��ͼ

��1�� ϵͳ�������� Bootloader

���������������ȴ�Ƭ�ڵ�bootstrap����ʼ�����ϵͳ��ȡ����Bootloader��ƣ�������һ��Sibl�͵ڶ���

U��boot��

����Sibl��bootstrap���ز�ִ�еĵ�һ�����������ڳ����С���ܵ�bootstrap���ص����ƣ��������Ͼ���������С�ͻ�����רһ������������������Ӳ����ʼ�����⣬��Ҫ������ʵ����������(����U��boot)��NAND

Flash�ļ��أ������һ��Bootloader����֮ǰ���ڴ��ַ�ռ�ֲ���

�ڶ���Bootloader���ù���ǿ���sourceforge��Դ����U��boot��U��boot����Ҫ���������Ƕ��ʽ����ϵͳ����ǰ�ĵײ�Ӳ����ʼ������ΪLinux�ں��ṩ����������������������ϵͳLinux�ں�����������,Ϊ��ʵ�ֳ������ļ����д��

NAND Flash��U��bootǶ����һ��NAND��ϵͳ��ͨ��U��boot���û�������ʵ�ֶ�NAND

Flash�Ķ�/д�������ɽ�������д��NAND Flashָ���ĵ�ַ�ռ䡣

��2�� Ƕ��ʽ����ϵͳ

LPC3180�ڲ�������arm926EJS�������ںˣ����洢��������ԪMMU��֧�ֶ�������Ƕ��ʽ����ϵͳ��ϵͳͨ����д�弶֧�ִ��룬��ֲ��

Linux2.6.10��Ϊƽ̨����ϵͳ�������ȶ���Linux2.6�ں�ʵ��������ȡ����̹������ڴ�����ȹ��ܣ�ͬʱ�����Linux�Ŀ������ԣ����ں˽��вü���Ӳ�������������ӣ�ϵͳʵ����һ��С�͵�����ǿ����ں˳�����Ӧ��Ƕ��ʽϵͳ�洢��Դ��Խ�ȱ��״����

5 ϵͳ�������̷���

������������ṹ��ɷ�����֪������ϵͳ�������̷�Ϊ3�����裺

�� ϵͳ�ϵ�����ȴ�Ƭ��ROM�̻���bootstrap����ִ�С�bootstrap��������ⲿ�����������ز�����ִ�С�bootstrap���й������ȶ���������GPIO_01�����GPIO_01��Ϊ�ߣ����NAND

Flash���س�������ϵͳ�����������Ϊ�ͣ������μ��USB�ӿں�UART5�ӿڣ�ͨ���ⲿ����������������ϵͳͨ������GPIO_IO����������

bootstrap�������̣�������GPIO_01��Ϊ�ߣ���NAND Flash���س���

�� ϵͳ�����ĵڶ���������bootstrap���ص���������Sibl��Sibl���ϵͳ��Ҫ�ij�ʼ����NAND

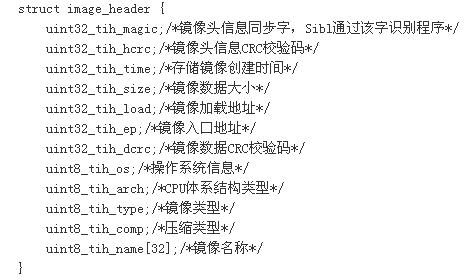

Flash���ؾ������ָ����SDRAM�ռ䡣�����������ʼλ��������64�ֽڵ�ͷ��Ϣ������Siblʶ��ͼ��أ�ͷ��Ϣ���ݽṹ���£�

Sibl��NAND Flash��ʼ��ַ��ʼ�����������������ͬ����ih_magic����ʶ�����������ƫ�Ƶ�ַ��ȡ�����Сih_size�ͼ��ص�ַ

ih_load����������ص�ָ����SDRAM�ռ䣻������ɺ����CRCУ����ih_dcrc��SDRAM���ݽ���CRC��⣻�����ݾ�������

ih_type�жϾ����Ƿ��ִ�У�����ִ�У������뾵����ڵ�ַih_ep������Sibl��������NAND

Flash�������

�������ʹ��U-boot�ṩ�Ĺ���mkimage����ͷ��Ϣ�������ʽ���£�

mkimage-A arch-O os-T type-C comp-a

addr-e ep-n name-d data_file image

�� ���Sibl���غ��ڴ�ռ�ֲ���ͼ6��ʾ��ϵͳ�����������̵ĵ�����U-

boot��U-boot���Linux�ں˾���Ľ�ѹ���Ͳ���ϵͳ����ǰ�ij�ʼ�������������ں���ڵ�ַ����ɶ�Linux��������

ͼ6 ϵͳ���������ڴ�ռ�ֲ�ͼ

6 ϵͳ���ܷ���

ϵͳ�����ṩ��һ��������LPC3180Ƕ��ʽ��Ӳ��ƽ̨�������LPC3180���������������в��Ժͷ��������Է�����ʹ��һ�����������ܼ����㷨����

ADS�������ֱ����ʹ��Ӳ��VFP�����������������汾�IJ��Գ����ڲ�ͬ��CPUʱ��Ƶ���±Ƚ�����ʱ�䣬������1���С�

����ʵ�����ݣ����Եó����ۣ�VFPЭ����������ͬʱ��Ƶ���£������5�����ҵĸ����������ܡ���ˣ�LPC3180ƽ̨���VFPЭ���������ܹ�ʵ�ָ��ӵĸ��������ܼ��㷨�����������м���Ӳ���������㵥Ԫ����ʹ�������������ݴ������������ߣ��ܹ�ʤ�ζ����������źŴ���Ӧ�á�

����

���Ľ�������LPC3180������Ϊ���ĵ�Ƕ��ʽ��Ӳ��ƽ̨�������ʵ�֣������ԡ���֤��LPC3180�ĸ����������ܡ���ƽ̨����LPC3180��Ӧ�ÿ������н�����塣ĿǰLPC3180��ҽ����е����ҵ���ơ�POS���������źŴ������������Ź㷺��Ӧ�á�

|