| 编辑推荐: |

本文主要介绍了高性能GPU服务器AI网络架构相关内容,希望对你的学习有帮助。

本文来自于微信公众号智能计算芯世界 ,由火龙果软件Linda编辑推荐。 |

|

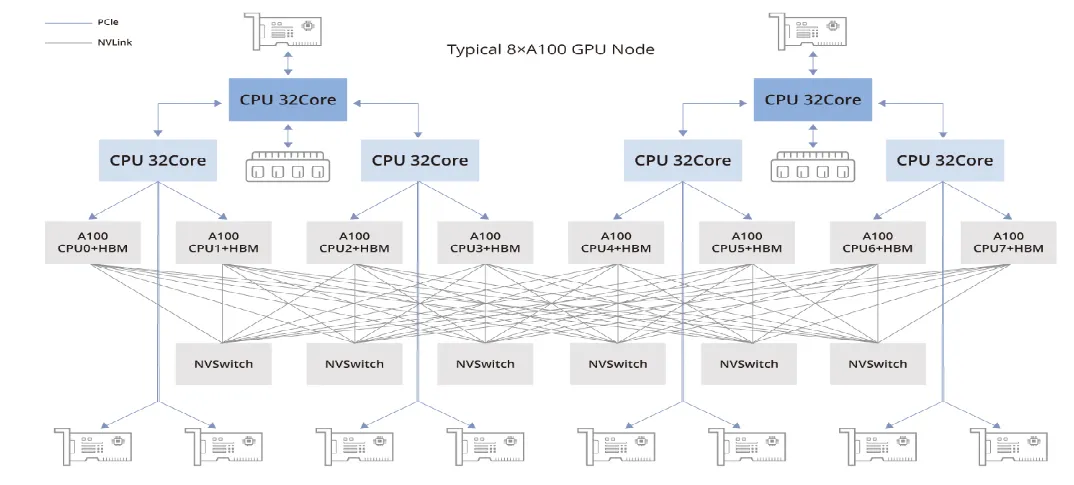

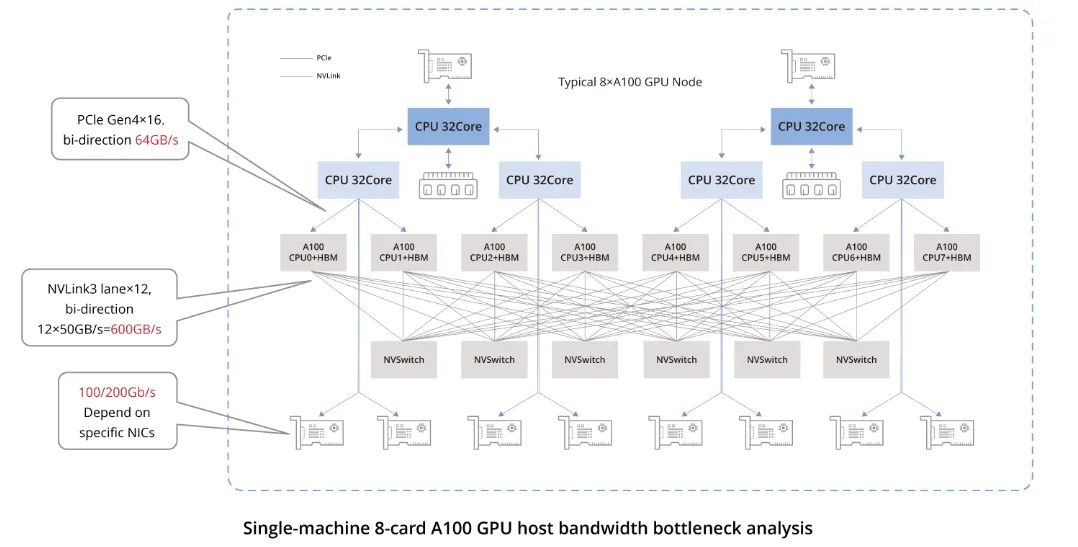

在大规模模型训练的领域中,构建高性能GPU服务器的基础架构通常依托于由单个服务器搭载8块GPU单元所组成的集群系统。这些服务器内部配置了如A100、A800、H100或H800等高性能GPU型号,并且随着技术发展,未来可能还会整合{4,

8} L40S等新型号GPU。下图展示了一个典型的配备了8块A100 GPU的服务器内部GPU计算硬件连接拓扑结构示意图。

本文将依据上述图表,对GPU计算涉及的核心概念与相关术语进行深入剖析和解读。

PCIe交换机芯片

在高性能GPU计算的领域内,关键组件如CPU、内存模块、NVMe存储设备、GPU以及网络适配器等通过PCIe(外设部件互连标准)总线或专门设计的PCIe交换机芯片实现高效顺畅的连接。历经五代技术革新,目前最新的Gen5版本确保了设备间极为高效的互连性能。这一持续演进充分彰显了PCIe在构建高性能计算系统中的核心地位,显著提升了数据传输速度,并有力地促进了现代计算集群中各互联设备间的无缝协同工作。

NVLink概述

NVLink定义

NVLink是英伟达(NVIDIA)开发并推出的一种总线及其通信协议。NVLink采用点对点结构、串列传输,用于中央处理器(CPU)与图形处理器(GPU)之间的连接,也可用于多个图形处理器之间的相互连接。与PCI

Express不同,一个设备可以包含多个NVLink,并且设备之间采用网格网络而非中心集线器方式进行通信。该协议于2014年3月首次发布,采用专有的高速信号互连技术(NVHS)。

该技术支持同一节点上GPU之间的全互联,并经过多代演进,提高了高性能计算应用中的双向带宽性能。

NVLink的发展历程:从NVLink 1.0到NVLink 4.0

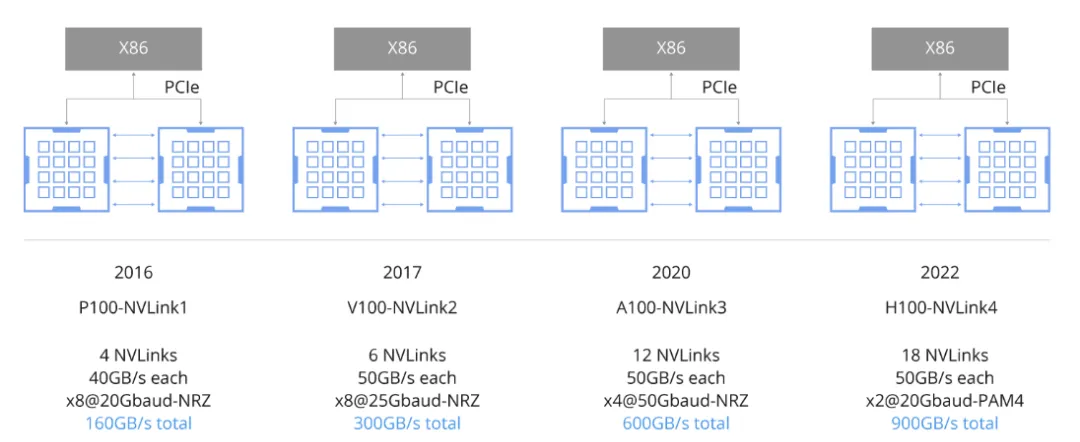

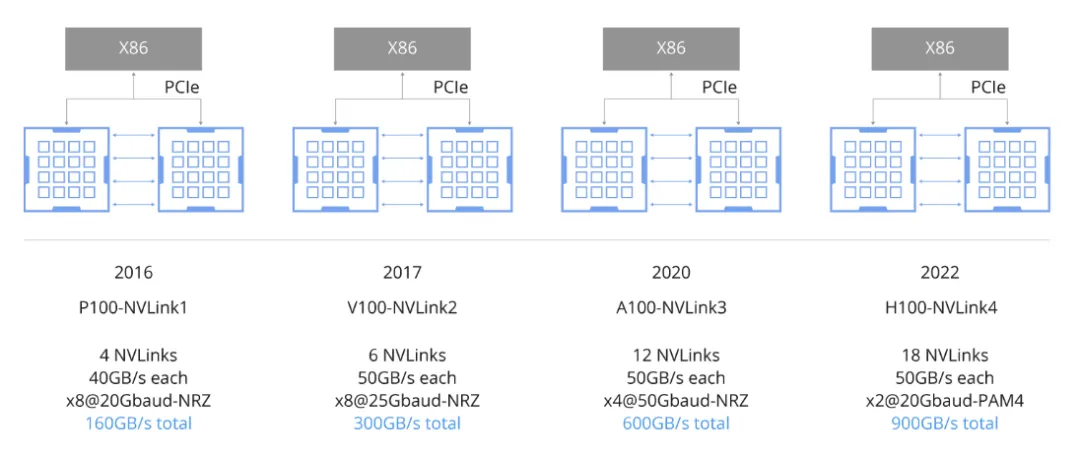

NVLink技术在高性能GPU服务器中的演进如下图所示:

NVLink 1.0

连接方式:采用4通道连接。

总带宽:实现高达160 GB/s的双向总带宽。

用途:主要用于加速GPU之间的数据传输,提升协同计算性能。

NVLink 2.0

连接方式:基于6通道连接。

总带宽:将双向总带宽提升至300 GB/s。

性能提升:提供更高的数据传输速率,改善GPU间通信效率。

NVLink 3.0

连接方式:采用12通道连接。

总带宽:达到双向总带宽600 GB/s。

新增特性:引入新技术和协议,提高通信带宽和效率。

NVLink 4.0

连接方式:使用18通道连接。

总带宽:进一步增加至双向总带宽900 GB/s。

性能改进:通过增加通道数量,NVLink 4.0能更好地满足高性能计算和人工智能应用对更大带宽的需求。

NVLink 1.0、2.0、3.0和4.0之间的关键区别主要在于连接通道数目的增加、所支持的总带宽以及由此带来的性能改进。随着版本迭代,NVLink不断优化GPU间的数据传输能力,以适应日益复杂且要求严苛的应用场景。

NVSwitch

NVSwitch是NVIDIA专为满足高性能计算和人工智能应用需求而研发的一款交换芯片,其核心作用在于实现同一主机内部多颗GPU之间的高速、低延迟通信。

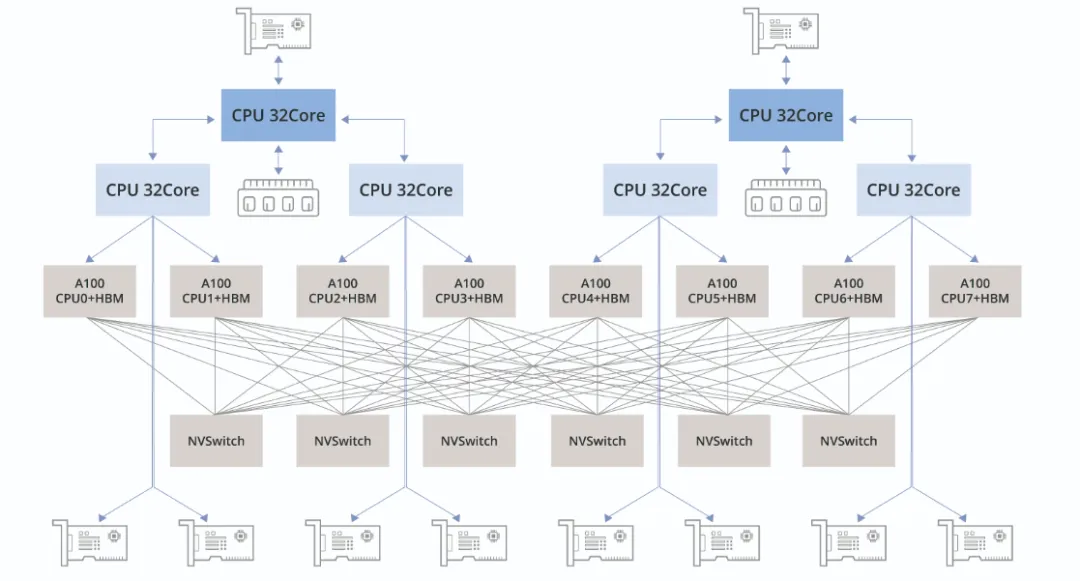

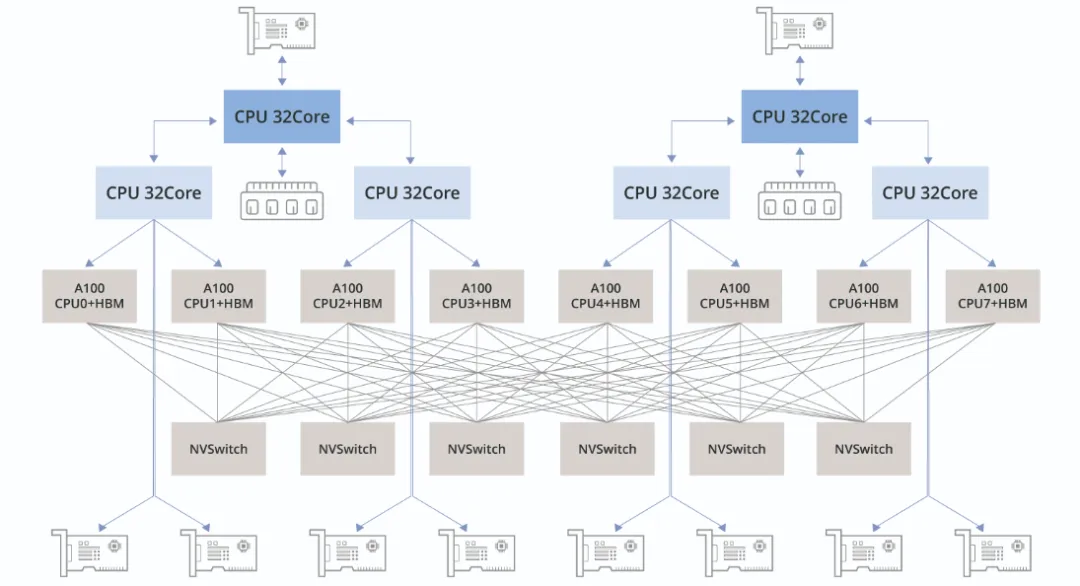

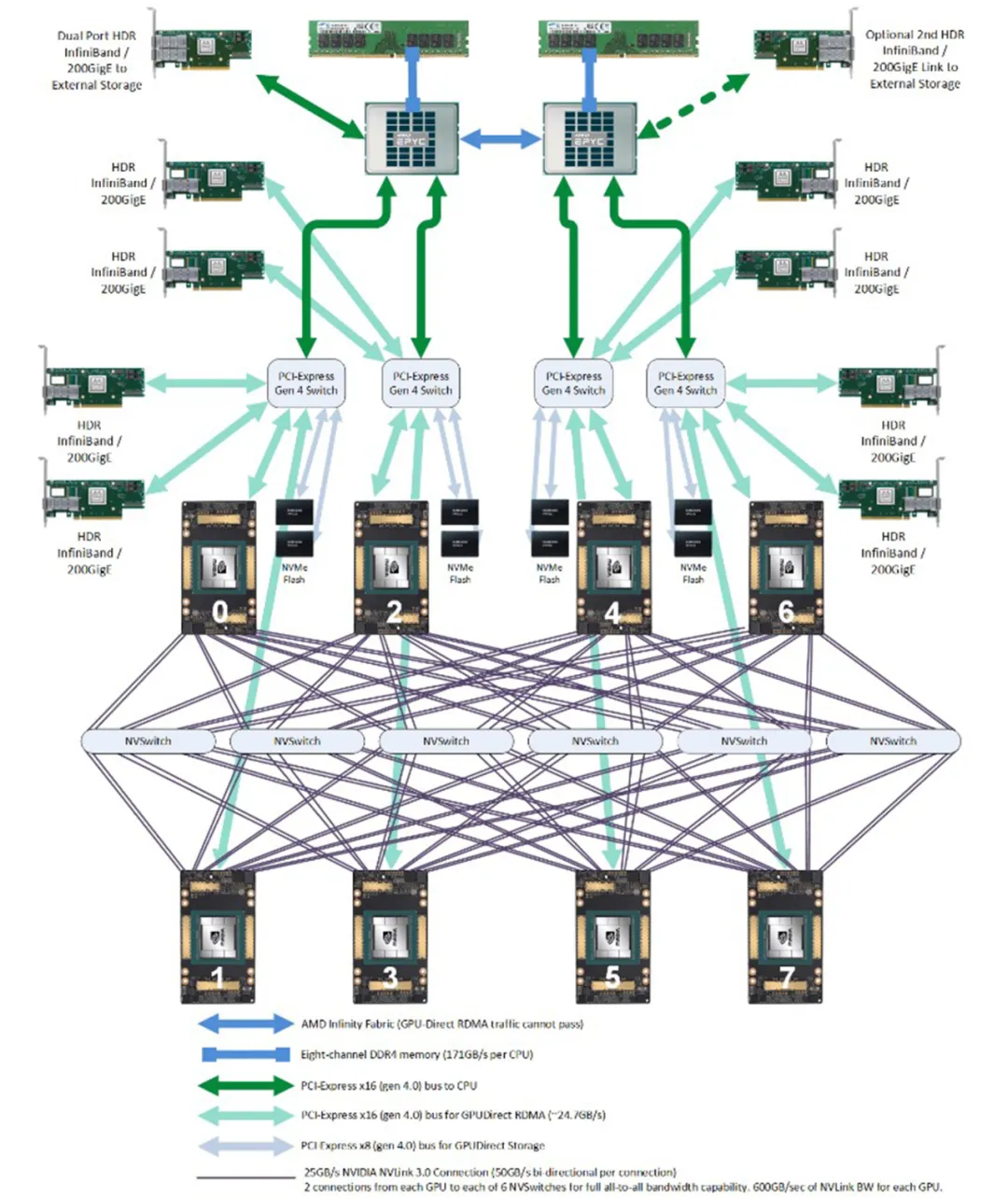

下图呈现了一台典型配置8块A100 GPU的主机硬件连接拓扑结构。

下图展示的是浪潮NF5488A5 NVIDIA HGX A100 8 GPU组装侧视图。在该图中,我们可以清楚地看到,在右侧六个大型散热器下方隐蔽着一块NVSwitch芯片,它紧密围绕并服务于周围的八片A100

GPU,以确保GPU间的高效数据传输。

NVLink交换机

NVLink交换机是一种由NVIDIA专为在分布式计算环境中的不同主机间实现GPU设备间高性能通信而设计制造的独立交换设备。不同于集成于单个主机内部GPU模块上的NVSwitch,NVLink交换机旨在解决跨主机连接问题。可能有人会混淆NVLink交换机和NVSwitch的概念,但实际上早期提及的“NVLink交换机”是指安装在GPU模块上的切换芯片。直至2022年,NVIDIA将此芯片技术发展为一款独立型交换机产品,并正式命名为NVLink交换机。

HBM(高带宽内存)

传统上,GPU内存与常见的DDR(双倍数据速率)内存相似,通过物理插槽插入主板并通过PCIe接口与CPU或GPU进行连接。然而,这种配置在PCIe总线中造成了带宽瓶颈,其中Gen4版本提供64GB/s的带宽,Gen5版本则将其提升至128GB/s。

为了突破这一限制,包括但不限于NVIDIA在内的多家GPU制造商采取了创新手段,即将多个DDR芯片堆叠整合,形成了所谓的高带宽内存(HBM)。例如,在探讨H100时所展现的设计,GPU直接与其搭载的HBM内存相连,无需再经过PCIe交换芯片,从而极大地提高了数据传输速度,理论上可实现显著的数量级性能提升。因此,“高带宽内存”(HBM)这一术语精准地描述了这种先进的内存架构。

HBM的发展历程:从HBM1到HBM3e

带宽单位解析

在大规模GPU计算训练领域,系统性能与数据传输速度密切相关,涉及到的关键通道包括PCIe带宽、内存带宽、NVLink带宽、HBM带宽以及网络带宽等。在衡量这些不同的数据传输速率时,需注意使用的带宽单位有所不同。

在网络通信场景下,数据速率通常以每秒比特数(bit/s)表示,且为了区分发送(TX)和接收(RX),常采用单向传输速率来衡量。而在诸如PCIe、内存、NVLink及HBM等其他硬件组件中,带宽指标则通常使用每秒字节数(Byte/s)或每秒事务数(T/s)来衡量,并且这些测量值一般代表双向总的带宽容量,涵盖了上行和下行两个方向的数据流。

因此,在比较评估不同组件之间的带宽时,准确识别并转换相应的带宽单位至关重要,这有助于我们全面理解影响大规模GPU训练性能的数据传输能力。

众所周知,在大型模型训练中,通常采用每台服务器配备多个GPU的集群架构。如上我们对GPU网络中的核心术语与概念进行了详尽介绍。下面将进一步深入探讨常见的GPU系统架构。

8台配备NVIDIA A100 GPU的节点/8台配备NVIDIA A800 GPU的节点

如上图所示的A100 GPU拓扑结构中,8块A100 GPU所组成的拓扑包含以下组件:

两颗CPU芯片(及其两侧相关的内存,NUMA架构):中央处理器负责执行通用计算任务。

两块存储网络适配卡(用于访问分布式存储,具备带内管理等功能):这些网卡用于访问分布式存储资源。

四颗PCIe Gen4交换芯片:PCIe Gen4是PCIe接口的第四代,提供了更高的数据传输速率。

六颗NVSwitch芯片:NVSwitch使得GPU与GPU之间能够以极高的速度直接通信,这对于大规模深度学习节点和并行计算任务的有效运行至关重要。

八块GPU:A100 GPU作为主要处理单元,负责执行并行计算,尤其适合人工智能和深度学习工作负载。

八块GPU专用网络适配卡:每块GPU配备一块专用的网络适配卡,旨在优化GPU之间的通信,并提升并行处理任务的整体性能。

接下来的部分我们将对这些组件进行详细解读。下一张图片将提供更详尽的拓扑结构信息供参考。

存储网络卡

在GPU架构中,存储网络卡的定位主要涉及其通过PCIe总线与中央处理器(CPU)的连接,以及负责促进与分布式存储系统的通信。以下是存储网络卡在GPU架构中的主要作用:

读写分布式存储数据:存储网络卡的主要功能之一是高效地从分布式存储系统读取和写入数据。这对于深度学习模型训练过程至关重要,在此过程中频繁访问分布在各处的训练数据以及将训练结果写入检查点文件极为重要。

节点管理任务:存储网络卡的功能不仅限于数据传输,还包括节点管理任务。这包括但不限于通过SSH(安全外壳协议)进行远程登录、监控系统性能以及收集相关数据等任务。这些任务有助于对GPU集群的运行状态进行监控和维护。

虽然官方推荐使用BF3 DPU,但在实践中,只要满足带宽需求,可以选用其他替代解决方案。例如,为了成本效益考虑,可以考虑使用RoCE;而为了最大限度提升性能,则优先选择InfiniBand。

NVSwitch 网络结构

在完全互联网络拓扑中,每个节点都直接与所有其他节点相连。通常情况下,8块GPU通过六个NVSwitch芯片以全互联配置相连接,这一整体也被称为NVSwitch架构。

在全互联结构中,每条线路的带宽取决于单个NVLink通道的带宽,表示为n * bw-per-nvlink-lane。对于采用NVLink3技术、每条通道带宽为50GB/s的A100

GPU,在全互联结构中,每条线路的总带宽为12 * 50GB/s = 600GB/s。需要注意的是,此带宽是双向的,既支持数据发送也支持接收,因此单向带宽为300GB/s。

相比之下,A800 GPU将NVLink通道的数量从12减少到了8。因此,在全互联结构中,每条线路的总带宽变为8

* 50GB/s = 400GB/s,单向带宽为200GB/s。

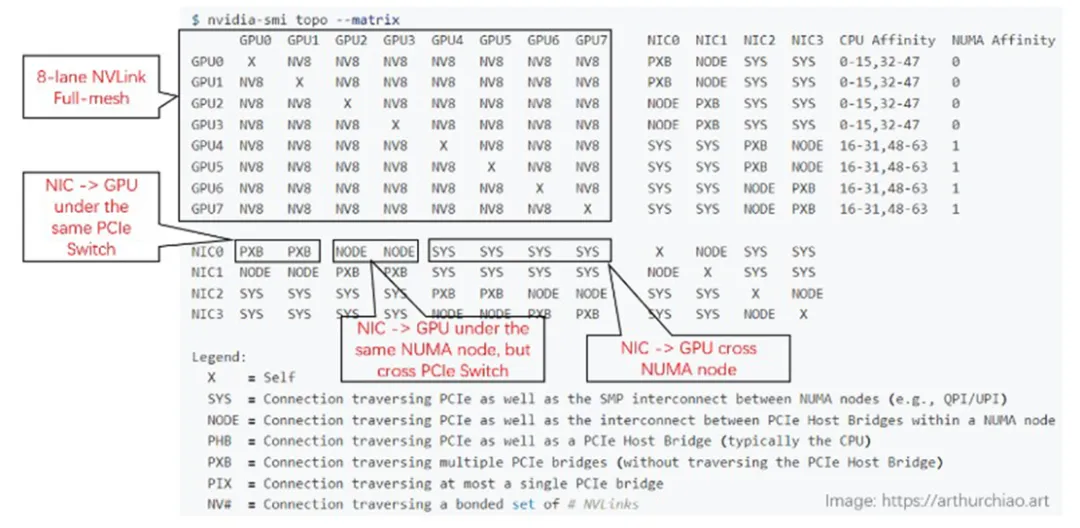

以下是一个由8*A800组成的设备的nvidia-smi拓扑结构图示。

GPU与GPU之间的连接(左上区域):所有连接均标记为NV8,表示有8条NVLink连接。

网络接口卡(NIC)连接:在同一CPU芯片内:标记为NODE,表示无需跨越NUMA结构,但需要穿越PCIe交换芯片。在不同CPU芯片之间:标记为SYS,表示必须跨越NUMA结构。

GPU至NIC的连接:在同一CPU芯片内且处于同一PCIe交换芯片下:标识为NODE,表示仅需穿越PCIe交换芯片。

在同一CPU芯片内但不在同一PCIe交换芯片下:指定为NNODE,表示需要同时穿越PCIe交换芯片和PCIe主机桥接芯片。

在不同CPU芯片之间:标记为SYS,表示需要跨越NUMA结构、PCIe交换芯片,并覆盖最长距离。

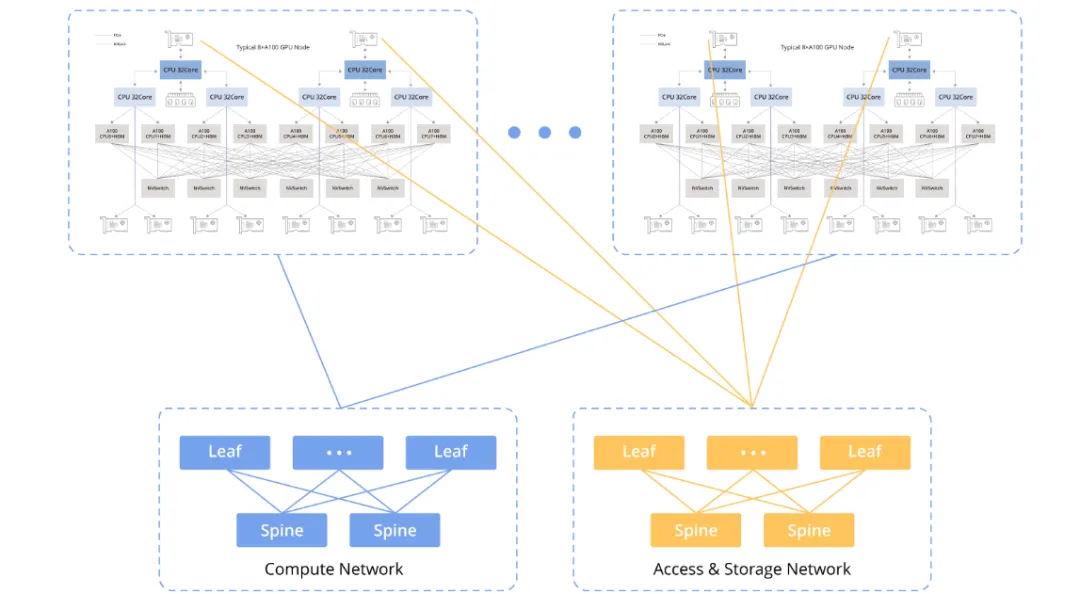

GPU节点互联架构

以下图表展示了GPU节点间的互联架构:

计算网络

计算网络主要用于连接GPU节点,支持并行计算任务之间的协同工作。这包括在多块GPU之间传输数据、共享计算结果以及协调大规模并行计算任务的执行。

存储网络

存储网络用于连接GPU节点和存储系统,支持大规模数据的读写操作。这包括将数据从存储系统加载到GPU内存中,以及将计算结果写回存储系统。

为了满足AI应用对高性能的需求,在计算网络和存储网络上,RDMA(远程直接内存访问)技术至关重要。在两种RDMA技术——RoCEv2和InfiniBand之间进行选择时,需要权衡成本效益与卓越性能,每种选项都针对特定应用场景和预算考虑进行了优化。

公共云服务提供商通常在其配置中采用RoCEv2网络,例如CX配置,其中包含8个GPU实例,每个实例配备8

* 100Gbps。与其他选项相比,只要能满足性能要求,RoCEv2相对较为经济实惠。

数据链路连接中的带宽瓶颈

该图表突出了关键连接的带宽规格:

同一主机内GPU之间的通信:通过NVLink技术,双向带宽达到600GB/s,单向带宽达到300GB/s。

同一主机内GPU与其各自网络接口卡(NIC)之间的通信:采用PCIe Gen4交换芯片,双向带宽为64GB/s,单向带宽为32GB/s。

不同主机间GPU之间的通信:数据传输依赖于NIC,带宽取决于所使用的具体NIC。当前在中国,对于A100/A800型号常用的NIC提供主流的单向带宽为100Gbps(12.5GB/s)。因此,相较于同一主机内的通信,不同主机间的GPU通信性能显著下降。

200Gbps(25GB/s)接近PCIe Gen4的单向带宽。400Gbps(50GB/s)超越了PCIe

Gen4的单向带宽。

因此,在此类配置中使用400Gbps的网卡并不能带来显著优势,因为要充分利用400Gbps带宽需要PCIe

Gen5级别的性能支持。

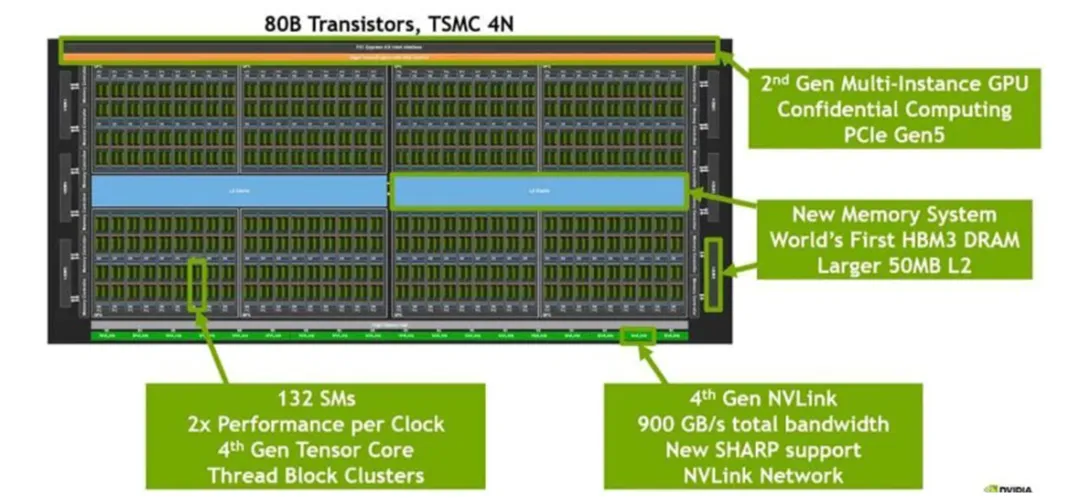

8x NVIDIA H100/8x NVIDIA H800 主机

H100主机内部的硬件拓扑结构

H100主机的整体硬件架构与A100八卡系统的架构非常相似,但也存在一些差异,主要体现在NVSwitch芯片的数量和带宽升级上。

在每个H100主机内部,配置了4颗芯片,比A100配置减少了两颗。

H100芯片采用4纳米工艺制造,底部一行配备了18条Gen4 NVLink连接,从而提供了900GB/s的双向总带宽。

H100 GPU 芯片

该芯片采用尖端的4纳米工艺制造,表明其采用了先进的制造技术。

芯片底部一排包含18个Gen4 NVLink连接,提供双向总带宽为18条通道 * 每通道25GB/s

= 900GB/s。

芯片中央蓝色区域代表L2高速缓存,用于存储临时数据的高速缓冲区。

芯片左右两侧则集成了HBM(高带宽内存)芯片,这些芯片作为图形内存使用,存储图形处理所需的数据。 |